# **40 A Stackable Synchronous Buck Regulator**

### **NCP3296**

The NCP3296, a highly-efficient stackable synchronous buck regulator, is capable of operating with an input range from 3 V to 18 V and supporting up to 40 A continuous load currents. Higher output currents can be achieved by 2, 3, or 4 parallel NCP3296 devices operating as an interleaved multi-phase buck regulator.

The NCP3296 utilizes fixed-frequency current-mode control to provide accurate voltage regulation and fast transient response. Flexible programming of function and parameters supports multiple applications.

### **Features**

- V<sub>IN</sub>: 3 18 V with Input Feed–Forward

- V<sub>OUT</sub>: 0.5 5.5 V with Remote Output Voltage Sense

- 40 A Continuous Output Current Stackable to 160 A

- Fixed Frequency Current Mode Control

- Integrated 5 V LDO or External Supply

- Enable with Programmable VIN UVLO

- Programmable Boot–Up Voltage

- Programmable Soft-Start

- Pre-Bias Start-Up

- Programmable Current Limit

- · Power Good Indicator

- Selectable Protection Mode (Latch-off or Hiccup)

- Under-Voltage and Over-Voltage Protection

- Output Discharge in Shutdown

- 150°C Operating Junction Temperature

### **Typical Applications**

- Networking Routers and Switches

- · Telecom Digital Baseband

- Telecom Radio Unit

- Server and Desktop Computers, Notebooks, Gaming

- High Density Power Solutions

- DC/DC Modules

- General Purpose POL Regulator

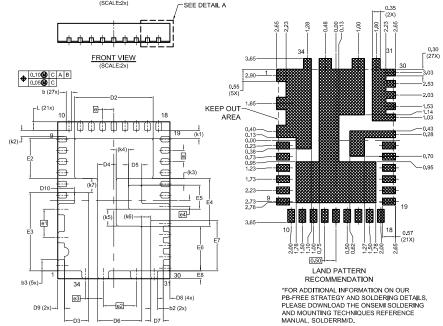

WQFN34 5x7, 0.5P CASE 510CL

### MARKING DIAGRAM

NCP3296 = Specific Device Code A = Assembly Location

WL = Wafer Lot

YY = Year WW = Work Week

G = Pb-Free Designator

### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 23 of this data sheet.

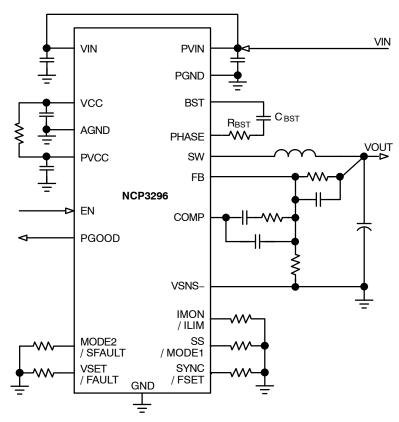

Figure 1. Typical 12 V<sub>IN</sub>, 40 A Application Circuit for Single Input Supply (LDO Enabled)

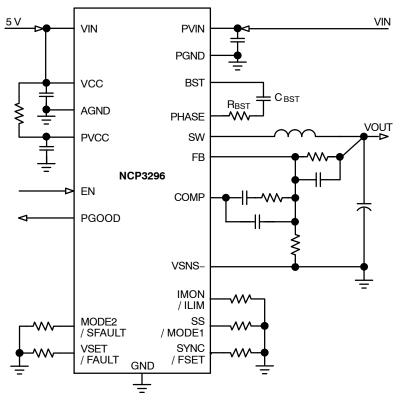

Figure 2. Typical 12  $V_{\text{IN}}$ , 40 A Application Circuit with External 5 V VCC Supply (LDO Disabled)

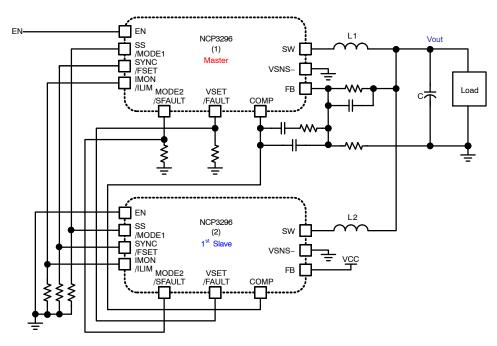

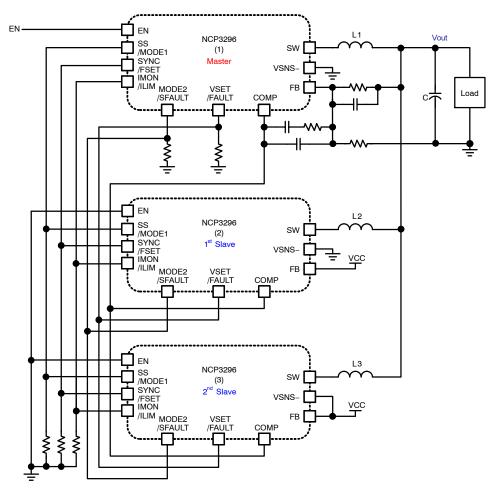

Figure 3. Typical 80 A Application Circuit with 2 Parallel NCP3296

Figure 4. Typical 120 A Application Circuit with 3 Parallel NCP3296

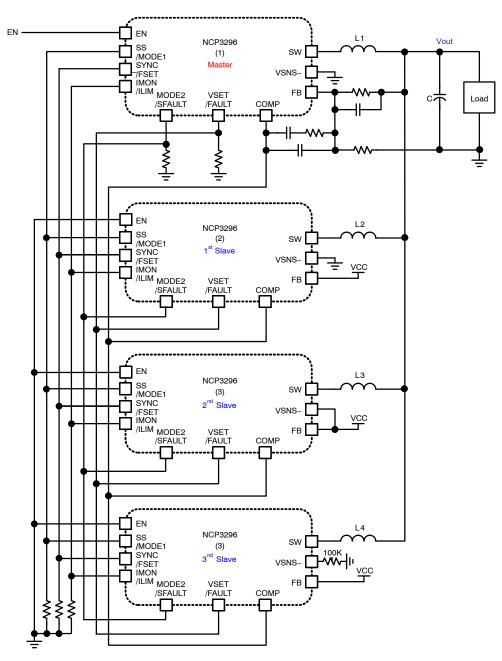

Figure 5. Typical 160 A Application Circuit with 4 Parallel NCP3296

Figure 6. Functional Block Diagram

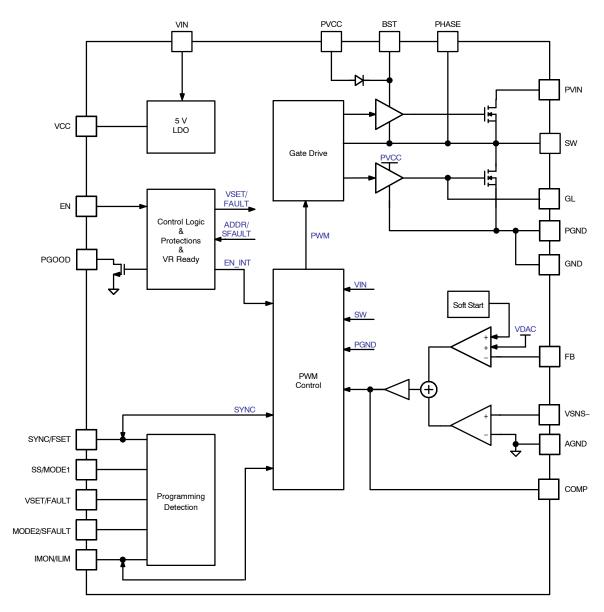

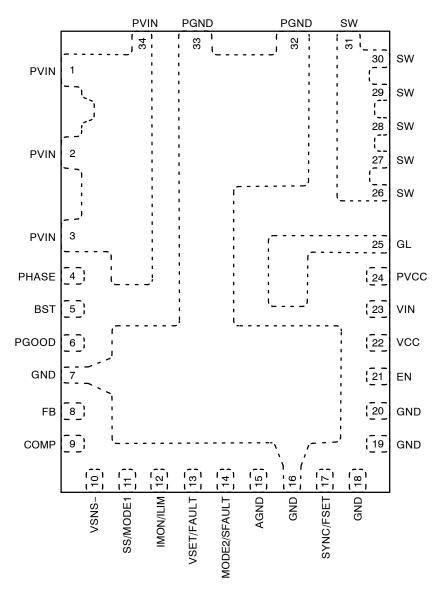

### **PIN CONNECTIONS**

Figure 7. Pin Assignment, Top Transparent View (5 x 7 mm, 0.5 mm Pitch)

### **PIN DESCRIPTION**

| Pin                       | Name              | Туре          | Description                                                                                                                                                                                                                                                                                  |

|---------------------------|-------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1~3, 34                   | PVIN              | Power         | <b>Power Supply Input</b> . Power supply input pins of the device, which are connected to the drain of internal high–side power MOSFET. Bypass directly to PGND with $\geq$ 22 $\mu$ F ceramic capacitors using the lowest impedance possible connections to the IC pins.                    |

| 4                         | PHASE             | Power         | <b>Phase Node</b> . Provides a return path for integrated high-side gate driver, which is internally connected to the source of the high-side MOSFET.                                                                                                                                        |

| 5                         | BST               | Power         | <b>Bootstrap</b> . Provides bootstrap voltage for high–side gate driver. A 0.22 $\mu$ F, 25 V ceramic capacitor is required from this pin to PHASE. A resistor (R <sub>BST</sub> ) in series with capacitor (C <sub>BST</sub> ) is also recommended.                                         |

| 6                         | PGOOD             | Logic Output  | <b>Power GOOD</b> . Open–drain output. Provides a logic high valid power good output signal, indicating the regulator's output is in the regulation window.                                                                                                                                  |

| 7, 16,<br>18~20,<br>32~33 | GND<br>PGND       | Power Ground  | <b>Power Ground</b> . Power supply ground pins of the device, which are connected to the source of the internal low–side power MOSFET. Must be connected to the system ground using lowest possible impedance path.                                                                          |

| 8                         | FB                | Analog Input  | <b>Feedback</b> . Inverting input to error amplifier. Also used to program the slave phase number.                                                                                                                                                                                           |

| 9                         | COMP              | Analog Output | Compensation. Output of error amplifier.                                                                                                                                                                                                                                                     |

| 10                        | VSNS-             | Analog Input  | Voltage Sense Negative Input. Connect this pin to remote voltage negative sense point. Also used to program the slave phase number.                                                                                                                                                          |

| 11                        | SS / MODE1        | Analog Input  | <b>Soft Start and Mode 1</b> . A 1% resistor between this pin and ground sets default soft start time, operation mode, and VOUT_SCALE_LOOP.                                                                                                                                                  |

| 12                        | IMON / ILIM       | Analog I/O    | IMON and Current Limit. IMON voltage output/input pin. A 1% resistor between this pin and ground programs the per–phase valley current limit and protection mode.                                                                                                                            |

| 13                        | VSET / FAULT      | Analog I/O    | <b>Boot–Up Voltage and FAULT</b> . A resistor from this pin to ground programs the boot–up voltage. Output pin of fault signal from master.                                                                                                                                                  |

| 14                        | MODE2 /<br>SFAULT | Analog I/O    | <b>Mode 2 and SFAULT</b> . A resistor from this pin to ground programs the device operation mode and phase count. Output pin of fault signal from slave.                                                                                                                                     |

| 15                        | AGND              | Analog Ground | Analog Ground. Ground of controller. Must be connected to the system ground using a low impedance single–point connection to GND/PGND.                                                                                                                                                       |

| 17                        | SYNC / FSET       | Analog I/O    | Synchronization Clock and Frequency Set. Synchronization clock output from master. A resistor between this pin and ground programs frequency.                                                                                                                                                |

| 21                        | EN                | Logic Input   | <b>Enable</b> . High enables the controller. Input supply UVLO can be programmed at this pin with external resistor divider.                                                                                                                                                                 |

| 22                        | VCC               | Power         | Output of LDO and Supply Voltage Input of Controller. Output of LDO and bias supply input of controller. A 2.2 $\mu$ F or larger ceramic capacitor bypasses this input to GND. This capacitor should be placed as close as possible to the pin.                                              |

| 23                        | VIN               | Power         | <b>Power Supply Input of LDO</b> . Power supply input of LDO. Use 1.0 $\mu$ F or more ceramic bypass capacitor to power ground. The capacitors should be placed as close as possible to this pin. For applications using an external VCC source, connect this pin to VCC and the 5 V source. |

| 24                        | PVCC              | Power         | Supply Voltage Input of Gate Drivers. A 4.7 $\mu$ F, 25 V or larger ceramic capacitor bypasses this input to PGND. This capacitor should be placed as close as possible to this pin.                                                                                                         |

| 25                        | GL                | Analog Output | Gate of Low-Side MOSFET. Directly connected with the gate of the low-side power MOSFET. No external connection is necessary.                                                                                                                                                                 |

| 26~31                     | SW                | Power         | Switch Node. Connect to the external inductor. These pins are interconnection between internal high-side MOSFET and low-side MOSFET.                                                                                                                                                         |

### MAXIMUM RATINGS (All voltages with respect to GND/PGND, unless otherwise specified.)

| Ra                                | ating (Note 1)                         | Symbol                               | Min                  | Max                     | Unit |  |

|-----------------------------------|----------------------------------------|--------------------------------------|----------------------|-------------------------|------|--|

| Input Voltage                     |                                        | $V_{VIN}, V_{PVIN}$                  | -0.3                 | 22                      | V    |  |

| Driver Supply Voltage             |                                        | V <sub>PVCC</sub>                    | -0.3                 | 6.5                     | V    |  |

| Analog Supply Voltage to AGND     | )                                      | V <sub>VCC</sub>                     | -0.3                 | 6.5                     | V    |  |

| SW, PHASE Voltage                 |                                        | V <sub>SW</sub> , V <sub>PHASE</sub> | -0.5,<br>-5 (<10 ns) | 25,<br>28 (<10 ns)      | V    |  |

| BST Voltage                       |                                        | V <sub>BST</sub>                     | -0.3                 | 30                      |      |  |

| BST to SW/PHASE Voltage           |                                        | $V_{BST-SW}$                         | -0.3                 | V                       |      |  |

| GL Voltage                        |                                        | V <sub>GL</sub>                      | -0.3,<br>-2 (<50 ns) | V <sub>PVCC</sub> + 0.3 | V    |  |

| VSNS- to AGND                     | Normal Dynamic Operation Range         | V <sub>SNS</sub> -                   | -0.2                 | 0.2                     | V    |  |

|                                   | During Slave Configuration at Start-up | 1                                    | -0.2                 | V <sub>VCC</sub> + 0.3  |      |  |

| SCL, SDA, PGOOD, ALERT# P         | ins                                    |                                      | -0.3                 | 6.5                     | ٧    |  |

| Other Pins                        |                                        |                                      | -0.3                 | V <sub>VCC</sub> + 0.3  | ٧    |  |

| GND/PGND to AGND (Note 2)         |                                        | $V_{AGND}$                           | -0.3                 | 0.3                     | ٧    |  |

| Operating Junction Temperature    | ,                                      | TJ                                   | -40                  | 150                     | °C   |  |

| Storage Temperature               |                                        | TSTG                                 | -55                  | 150                     | °C   |  |

| Lead Temperature Soldering Re     | flow (Note 3)                          | T <sub>SLD</sub>                     | 2                    | 60                      | °C   |  |

| ESD, Human Body Model per Al      | NSI/ESDA/JEDEC JS-001                  | ESD <sub>HBM</sub>                   | 2                    | _                       | kV   |  |

| ESD, Charge Device Model per      | ANSI/ESDA/JEDEC JS-002                 | ESD <sub>CDM</sub>                   | 1.5                  | -                       | kV   |  |

| Maximum Latch-up Current Rat      | ing, 150°C, per JEDEC JESD78           | I <sub>LU</sub>                      | -100 100             |                         | mA   |  |

| Moisture Sensitivity Level per IP | C/JEDEC Standard: J-STD-020A           | MSL                                  |                      | 1                       |      |  |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

- 2. GND and PGND are internally connected. AGND requires PCB connection to GND.

- 3. For information, please refer to our Soldering and Mounting Techniques Reference Manual, SOLDERRM/D

### THERMAL CHARACTERISTICS

| Rating                                       | Symbol         | Value | Unit |

|----------------------------------------------|----------------|-------|------|

| Thermal Resistance, Junction-to-Air (Note 4) | $R_{	heta JA}$ | 14.6  | °C/W |

| Thermal Resistance, MOSFET Junction-to-PCB   | $R_{	heta JB}$ | 1.5   | °C/W |

<sup>4.</sup> Values are based upon onsemi Evaluation Board of 2 oz. copper thickness and FR4 PCB substrate.

### RECOMMENDED OPERATING CONDITIONS

| Rating                     | Symbol              | Min | Max | Unit |

|----------------------------|---------------------|-----|-----|------|

| Input Voltage (Note 5)     | $V_{VIN}, V_{PVIN}$ | 3   | 18  | V    |

| Output Voltage             | V <sub>OUT</sub>    | 0.5 | 5.5 | V    |

| Output Current, Continuous | l <sub>OUT</sub>    | 0   | 40  | Α    |

| SW Voltage, Peak (Note 6)  | V <sub>SW pk</sub>  | -   | 22  | V    |

| Junction Temperature       | $T_J$               | -40 | 150 | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

- 5. Operation at <4.5V<sub>IN</sub> requires external 5 V supply be applied to the VIN and VCC pins per Figure 2.

6. Operation above V<sub>SW pk</sub> may result in reduced IMON accuracy (V<sub>IMON ACY</sub>).

<sup>1.</sup> Refer to ELECTRICAL CHARACTERISTICS, RECOMMENDED OPERATING RANGES and/or APPLICATION INFORMATION for Safe Operating parameters.

**ELECTRICAL CHARACTERISTICS** (VIN = PVIN = 12 V, VOUT = 1.0 V,  $F_{SW}$  = 500 kHz, circuit of Figure 1. Typical values:  $T_A = T_J = 25^{\circ}C$ , min/max:  $-40^{\circ}C \le T_J \le 150^{\circ}C$ , unless otherwise specified.)

| Parameter                     | Conditions                                                                             | Symbol               | Min  | Тур  | Max        | Unit |

|-------------------------------|----------------------------------------------------------------------------------------|----------------------|------|------|------------|------|

| SUPPLY CURRENT                |                                                                                        |                      |      |      |            |      |

| Input Shutdown Current        | EN = 0, VIN = PVIN, LDO Enabled                                                        | I <sub>PVIN_SD</sub> | -    | 7    | 9          | mA   |

|                               | EN = 0, LDO Disabled, VCC = 5.2 V                                                      |                      |      | 375  | 480        | μΑ   |

| Input Quiescent Current       | 12 V <sub>IN</sub> , VIN = PVIN, no switching                                          | I <sub>PVIN_Q</sub>  | -    | 10   | 17         | mA   |

|                               | 18 V <sub>IN</sub> , VIN = PVIN, no switching                                          |                      | _    | 10   | 17         |      |

| INTERNAL LINEAR REGULATOR     |                                                                                        |                      |      |      |            |      |

| LDO Output Voltage            | 6 V $\leq$ V <sub>VIN</sub> $\leq$ 18 V, EN = 0, I <sub>VCC</sub> = 0 – 50 mA external | V <sub>CC</sub>      | 4.8  | 5.0  | 5.3        | V    |

| LDO Drop-Out Voltage          | V <sub>VIN</sub> = 5 V, EN = 0, I <sub>VCC</sub> = 50 mA external                      | $V_{DO}$             | -    | -    | 250        | mV   |

| LDO Current Limit             | V <sub>VIN</sub> = 5.4 V, EN = 0                                                       | I <sub>CC_MAX</sub>  | 95   | -    | -          | mA   |

| VCC UVLO Threshold            | V <sub>VCC</sub> rising                                                                | V <sub>CC_OK</sub>   | -    | 4.4  | 4.5        | V    |

|                               | V <sub>VCC</sub> falling                                                               | V <sub>CC_UV</sub>   | 4.0  | 4.2  | -          |      |

|                               | Hysteresis                                                                             | V <sub>CC HYS</sub>  | -    | 200  | -          | mV   |

| ENABLE                        |                                                                                        |                      | •    | •    | •          |      |

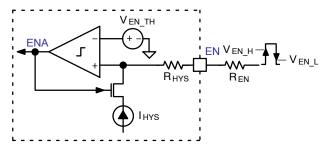

| EN On Threshold               | EN rising                                                                              | V <sub>EN_TH</sub>   | 1.08 | 1.20 | 1.32       | V    |

| Hysteresis Resistance         |                                                                                        | R <sub>HYS</sub>     | _    | 40   | _          | kΩ   |

| Hysteresis Current            |                                                                                        | I <sub>EN_HYS</sub>  | _    | 5.2  | _          | μΑ   |

| EN Input Leakage Current      | EN = 1 V                                                                               | I <sub>EN LKG</sub>  | _    | _    | 0.5        | μΑ   |

| DEFAULT PROGRAMMING /DETE     | CTION                                                                                  | _                    | •    | •    | •          |      |

| Source Current from Pin       | SS/MODE1 pin                                                                           | I <sub>SS</sub>      | 9.7  | 10   | 10.3       | μΑ   |

|                               | IMON/ILIM pin                                                                          | I <sub>ILIM</sub>    | 9.7  | 10   | 10.3       |      |

|                               | VSET/FAULT pin                                                                         | I <sub>VSET</sub>    | 9.7  | 10   | 10.3       |      |

|                               | MODE2/SFAULT pin                                                                       | I <sub>ADDR</sub>    | 9.7  | 10   | 10.3       |      |

|                               | SYNC/FSET pin                                                                          | I <sub>FSW</sub>     | 9.7  | 10   | 10.3       |      |

| PWM MODULATOR                 |                                                                                        | <u> </u>             |      |      |            |      |

| Minimum On-Time (Note 7)      |                                                                                        | T <sub>ON MIN</sub>  | _    | 35   | 55         | ns   |

| Minimum Off-Time (Note 7)     |                                                                                        | T <sub>OFF MIN</sub> | _    | 275  | 300        | ns   |

| VOLTAGE ERROR AMPLIFIER       |                                                                                        |                      |      |      |            |      |

| Open Loop DC Gain (Note 7)    |                                                                                        | $AV_{EA}$            | _    | 80   | _          | dB   |

| Unity Gain Bandwidth (Note 7) |                                                                                        | GBW <sub>EA</sub>    | -    | 12   | _          | MHz  |

| Slew Rate (Note 7)            |                                                                                        | SR <sub>COMP</sub>   | _    | 15   | _          | V/μs |

| Output Source/Sink Current    | V <sub>COMP</sub> = 1.2 V                                                              | I <sub>COMP</sub>    | 10   | 20   | _          | mA   |

| COMP Voltage Swing            | I <sub>COMP(SOURCE)</sub> = 2 mA                                                       | V <sub>COMP_H</sub>  | 3.1  | 3.4  | _          | V    |

|                               | I <sub>COMP(SINK)</sub> = 2 mA                                                         | V <sub>COMP L</sub>  | -    | 0.55 | 0.78       | V    |

| FB Bias Current               | V <sub>FB</sub> = 1.00 V                                                               | I <sub>FB</sub>      | -150 | _    | 150        | nA   |

| CURRENT SENSE AMPLIFIER       |                                                                                        |                      |      |      |            |      |

| Closed Loop DC Gain           |                                                                                        | $AV_{CA}$            | -    | -10  | _          | mV/A |

| -3dB Gain Bandwidth (Note 7)  |                                                                                        | BW <sub>CA</sub>     | _    | 7    | _          | MHz  |

| REFERENCE VOLTAGE             | <u>'</u>                                                                               |                      | •    |      |            |      |

| Reference Voltage (Note 7)    | Programmable Range, $R_{SS/MODE1}$ = 10.0 kΩ                                           | $V_{FB}$             | 0.50 | _    | 1.25       | V    |

| <b>3</b> ( ,                  | Resolution, $R_{SS/MODE1} = 10.0 \text{ k}\Omega$                                      | <b>-</b>             | _    | 50   | -          | mV   |

|                               | Setting/Value                                                                          | Determined by F      |      |      | SET/EALILT | V    |

|                               | 5                                                                                      |                      |      | , ,  | 1/1 / TOL1 |      |

**ELECTRICAL CHARACTERISTICS** (VIN = PVIN = 12 V, VOUT = 1.0 V,  $F_{SW}$  = 500 kHz, circuit of Figure 1. Typical values:  $T_A = T_J = 25^{\circ}C$ , min/max:  $-40^{\circ}C \le T_J \le 150^{\circ}C$ , unless otherwise specified.) (continued)

| Parameter                                          | Co                                                                    | onditions                           | Symbol                            | Min                    | Тур                                          | Max      | Unit |

|----------------------------------------------------|-----------------------------------------------------------------------|-------------------------------------|-----------------------------------|------------------------|----------------------------------------------|----------|------|

| REFERENCE VOLTAGE                                  |                                                                       |                                     |                                   |                        |                                              |          |      |

| Reference Voltage Accuracy                         | 0°C ≤ T <sub>J</sub> ≤ 125°C                                          | R <sub>VSET</sub> = 10.0 kΩ         | V <sub>FB_ACCY</sub>              | 494                    | 500                                          | 506      | mV   |

|                                                    |                                                                       | R <sub>VSET</sub> = 82.5 kΩ         |                                   | 994                    | 1000                                         | 1006     |      |

|                                                    |                                                                       | R <sub>VSET</sub> = open            | 1                                 | 1243                   | 1250                                         | 1257     |      |

|                                                    | $-40^{\circ}\text{C} \le \text{T}_{\text{J}} \le 150^{\circ}\text{C}$ | R <sub>VSET</sub> = 10.0 kΩ         |                                   | 492                    | 500                                          | 508      |      |

|                                                    |                                                                       | R <sub>VSET</sub> = 82.5 kΩ         | 1                                 | 992                    | 1000                                         | 1008     |      |

|                                                    |                                                                       | R <sub>VSET</sub> = open            | 1                                 | 1241                   | 1250                                         | 1259     |      |

| CYCLE-BY-CYCLE CURRENT LIM                         | IIT                                                                   |                                     |                                   |                        |                                              |          |      |

| Valley Current Limit (Note 7)                      | Threshold Range                                                       |                                     | $I_{VLY}$                         | 10                     | -                                            | 60       | Α    |

|                                                    | Resolution                                                            | 10 ≤ A I <sub>VLY</sub> < 20 A      | 1                                 | _                      | 2                                            | _        | 1    |

|                                                    |                                                                       | 20 ≤ A I <sub>VLY</sub> < 60 A      |                                   | -                      | 4                                            | _        | 1    |

|                                                    | Setting                                                               | 1                                   |                                   | Determi                | ned by R <sub>IN</sub>                       | 1ON/ILIM | 1    |

|                                                    | Accuracy, I <sub>VLY</sub> ≥ 20 A                                     | A, 0°C < T <sub>J</sub> < 125°C     | 1                                 | -5                     | -                                            | 10       | %    |

|                                                    | Accuracy, I <sub>VLY</sub> ≥ 20 A                                     |                                     | -10                               | -                      | 15                                           | 1        |      |

| Over–Current Protection<br>De–Bounce Time (Note 7) | Consecutive cycles before fault state entry                           |                                     | T <sub>D_VLY</sub>                | -                      | 32 / F <sub>SW</sub>                         | -        | s    |

| Negative Current Limit Threshold (Note 7)          | Low-Side FET                                                          | I <sub>LIM_NEG</sub>                | -                                 | 45                     | -                                            | Α        |      |

| SWITCHING FREQUENCY                                |                                                                       |                                     |                                   |                        |                                              |          |      |

| Switching Frequency, 1 Phase                       | Programmable Rang                                                     | e                                   | F <sub>SW</sub>                   | 200                    | -                                            | 2000     | kHz  |

|                                                    | Resolution                                                            | 200 ≤ F <sub>SW</sub> < 400 kHz     | 1                                 | _                      | 50                                           | _        | 1    |

|                                                    |                                                                       | 400 ≤ F <sub>SW</sub> < 1,000 kHz   | 1                                 | _                      | 100                                          | _        |      |

|                                                    |                                                                       | 1,000 ≤ F <sub>SW</sub> ≤ 2,000 kHz | 1                                 | _                      | 200                                          | _        |      |

|                                                    | Setting                                                               | 1                                   | Determin                          | ned by R <sub>SY</sub> | NC/FSET                                      | 1        |      |

|                                                    | Accuracy                                                              |                                     |                                   | -10                    |                                              | 10       | %    |

| SYNCHRONIZATION (SYNC/FSET                         | PIN)                                                                  |                                     |                                   |                        | <u>.                                    </u> |          |      |

| Logic High Output Voltage, Master                  | ISYNC = 4 mA (sourci                                                  | ing)                                | VOH_SYNC                          | VCC -<br>0.3           | -                                            | _        | V    |

| Logic Low Output Voltage, Master                   | ISYNC = -4 mA (sinki                                                  | ng)                                 | VOL_SYNC                          |                        | -                                            | 0.3      | V    |

| Logic High Input Voltage, Slave                    |                                                                       |                                     | VIH_SYNC                          | VCC -<br>1.0           | -                                            | -        | V    |

| Logic Low Input Voltage, Slave                     |                                                                       |                                     | VIL_SYNC                          | _                      | -                                            | 1.0      | V    |

| Hysteresis (Slave)                                 |                                                                       |                                     |                                   | _                      | 1.3                                          | _        | V    |

| Input Current Bias, Slave                          |                                                                       |                                     | IIN_SYNC                          | -0.5                   | -                                            | 0.5      | μΑ   |

| Input Capacitance, Slave (Note 7)                  |                                                                       |                                     |                                   | _                      | 5.0                                          | _        | pF   |

| MASTER/SLAVE FAULTS (FAULT, S                      | SFAULT PINS)                                                          |                                     |                                   |                        | <u> </u>                                     |          |      |

| Tri-State Voltage                                  | I <sub>FAULT</sub> = I <sub>SFAULT</sub> = 0                          |                                     | VFLT_3ST                          | 1.7                    | 2.0                                          | 2.3      | V    |

| Tri-State Source Current                           | V <sub>FAULT</sub> = V <sub>SFAULT</sub> =                            | 1.6 V                               | I <sub>3ST UP</sub>               | 230                    | 300                                          | 370      | μΑ   |

| Tri-State Sink Current                             |                                                                       | VFAULT = VSFAULT = 2.4 V            |                                   |                        | 100                                          | 120      | μΑ   |

| Output Pull-Up Impedance                           | I <sub>FAULT</sub> = I <sub>SFAULT</sub> = 2                          | mA (sourcing)                       | I <sub>3ST_DN</sub> $R_{FLT\_HI}$ | 25                     | 36                                           | 60       | Ω    |

| Output Pull-Down Impedance                         | I <sub>FAULT</sub> = I <sub>SFAULT</sub> = -2                         |                                     | R <sub>FLT LO</sub>               | 240                    | 260                                          | 300      | Ω    |

| Input Logic Low Threshold                          |                                                                       |                                     | V <sub>FLT_IL</sub>               | _                      | _                                            | 0.4      | V    |

| Input Logic High Threshold                         |                                                                       |                                     | V <sub>FLT_IH</sub>               | VCC -<br>1.5           | -                                            | _        | V    |

**ELECTRICAL CHARACTERISTICS** (VIN = PVIN = 12 V, VOUT = 1.0 V,  $F_{SW}$  = 500 kHz, circuit of Figure 1. Typical values:  $T_A = T_J = 25^{\circ}C$ , min/max:  $-40^{\circ}C \le T_J \le 150^{\circ}C$ , unless otherwise specified.) (continued)

| Parameter                              | С                                     | onditions                                              | Symbol                | Min     | Тур                    | Max     | Unit              |

|----------------------------------------|---------------------------------------|--------------------------------------------------------|-----------------------|---------|------------------------|---------|-------------------|

| SOFT START                             |                                       |                                                        |                       |         |                        |         |                   |

| Soft Start Delay Time                  | Setting                               |                                                        | T <sub>ON_DLY</sub>   | _       | 1                      | _       | ms                |

|                                        | Accuracy                              |                                                        |                       | -0.8    | -                      | 1.4     | 1                 |

| Soft Start Time (0-V <sub>FB</sub> )   | Programmable Rang                     | ge                                                     | T <sub>SS</sub>       | 1       | -                      | 20      | ms                |

|                                        | Resolution                            |                                                        |                       | 1, 3,   | 1, 3, 5, 10, 15, or 20 |         | 1                 |

|                                        | Setting                               |                                                        |                       | Determi | ned by R <sub>S</sub>  | S/MODE1 |                   |

|                                        | Accuracy                              | Valid R <sub>VSET</sub> values ≥ 1.00 V <sub>OUT</sub> |                       | -20     | -                      | 20      | %                 |

|                                        |                                       | Valid R <sub>VSET</sub> values < 1.00 V <sub>OUT</sub> |                       | -25     | -                      | 25      |                   |

| DISABLE / SHUTDOWN                     | •                                     | •                                                      | •                     |         | •                      |         |                   |

| Output Fall Time OVP, (VFB-0)          | Setting                               |                                                        | T <sub>OFF</sub>      | _       | 5                      | _       | ms                |

|                                        | Accuracy (for valid F                 | R <sub>VSET/FAULT</sub> values)                        |                       | -20     | -                      | 20      | %                 |

| Output Discharge Load                  | SW to GND                             | · · · · · · · · · · · · · · · · · · ·                  | R <sub>SW_D</sub>     | _       | 5                      | _       | kΩ                |

| INPUT VOLTAGE PROTECTION               | •                                     |                                                        |                       |         |                        |         |                   |

| Input Over-Voltage Protection          | Threshold Range, V                    | V <sub>PVIN_OVP</sub>                                  | _                     | 18      | _                      | V       |                   |

|                                        | Accuracy                              |                                                        | _                     | -5      | -                      | 5       | %                 |

|                                        | Hysteresis                            |                                                        | V <sub>PVIN_HYS</sub> | _       | 200                    | _       | mV                |

| De-Bounce Time                         |                                       |                                                        | T <sub>D_VINOV</sub>  | _       | 1                      | _       | μs                |

| Input UVLO Threshold, Rising           | Threshold (V <sub>PVIN</sub> )        |                                                        | V <sub>PVIN_ON</sub>  | _       | 3.0                    | _       | V                 |

|                                        | -                                     | Accuracy                                               |                       |         | -                      | 5       | %                 |

| Input UVLO Threshold, Falling          | Threshold (V <sub>PVIN</sub> )        | V <sub>PVIN_OFF</sub>                                  | _                     | 2.5     | _                      | V       |                   |

|                                        | Accuracy                              |                                                        | -6                    | _       | 5                      | %       |                   |

| OUTPUT VOLTAGE PROTECTION              | · · · · · · · · · · · · · · · · · · · |                                                        |                       |         | 1                      |         |                   |

| Output Over-Voltage Fault              | Threshold                             |                                                        | V <sub>OVP_TH</sub>   | _       | 121                    | _       | % V <sub>FB</sub> |

| Threshold<br>(FB to VSNS-, Rising FB)  | Accuracy                              |                                                        | -2                    | -       | 2                      | 1       |                   |

| (i b to voive ; rubing i b)            | Hysteresis                            |                                                        |                       | _       | 25                     | _       | mV                |

|                                        | De-Bounce Time                        |                                                        | T <sub>D_OVP</sub>    | _       | 1                      | _       | μs                |

| Output Under-Voltage Fault             | Threshold                             |                                                        | V <sub>UVP_TH</sub>   | _       | 20                     | _       | % V <sub>FB</sub> |

| Threshold<br>(FB to VSNS-, Falling FB) | Accuracy                              |                                                        |                       | -3.5    | -                      | 2       | 1                 |

| (1 B to volve , 1 aming 1 B)           | Hysteresis                            |                                                        |                       | _       | 1                      | _       | 1                 |

|                                        | De-Bounce Time                        |                                                        | T <sub>D UVP</sub>    | -       | 1                      | _       | μS                |

| Absolute Over-Voltage Threshold        | Threshold, rising                     |                                                        | V <sub>OV_A</sub>     | 2.02    | 2.20                   | 2.38    | V                 |

| during Soft Start (FB to VSNS-)        | Hysteresis                            |                                                        | V <sub>OV_HYS</sub>   | _       | 25                     | -       | mV                |

| THERMAL PROTECTION                     | •                                     |                                                        |                       |         |                        | •       |                   |

| Thermal Shutdown Threshold (Note 7)    | T <sub>J</sub> rising                 |                                                        | T <sub>SD</sub>       | 160     | 170                    | _       | °C                |

| Restart Temperature Threshold (Note 7) | T <sub>J</sub> falling                |                                                        | T <sub>RST</sub>      | _       | 155                    | -       | °C                |

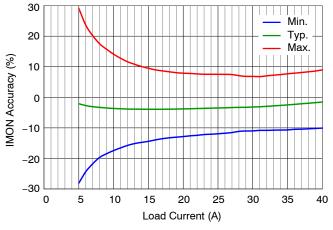

| IMON                                   | -                                     |                                                        | <u> </u>              |         | -                      | -       | -                 |

| Output Offset Voltage                  | I <sub>OUT</sub> = 0 A                |                                                        | V <sub>IMON_0</sub>   | -       | 1.00                   | -       | V                 |

| Output Voltage Gain                    | $V_{IMON} = [1.00 + (0.0)]$           | 015625 * I <sub>OUT</sub> )] V                         | V <sub>IMON_I</sub>   | -       | 15.625                 | -       | mV/A              |

| Output Accuracy (Note 7)               | I <sub>OUT</sub> = 40 A               |                                                        | V <sub>IMON_ACY</sub> | -       | ±6                     | _       | %                 |

|                                        | I <sub>OUT</sub> = 25 A               | _                                                      | -                     | ±8      | -                      | 1       |                   |

|                                        | I <sub>OUT</sub> = 10 A               |                                                        | _                     | ±12     | _                      | 1 '     |                   |

$\begin{tabular}{ll} \textbf{ELECTRICAL CHARACTERISTICS} (VIN = PVIN = 12 \ V, \ VOUT = 1.0 \ V, \ F_{SW} = 500 \ kHz, \ circuit \ of Figure 1. \\ Typical values: $T_A = T_J = 25^{\circ}C$, min/max: $-40^{\circ}C \le T_J \le 150^{\circ}C$, unless otherwise specified.) (continued) $T_A = T_J = 25^{\circ}C$, min/max: $-40^{\circ}C \le T_J \le 150^{\circ}C$, unless otherwise specified.) (continued) $T_A = T_J = 25^{\circ}C$, min/max: $-40^{\circ}C \le T_J \le 150^{\circ}C$, unless otherwise specified.) (continued) $T_A = T_J = 25^{\circ}C$, min/max: $-40^{\circ}C \le T_J \le 150^{\circ}C$, unless otherwise specified.) (continued) $T_A = T_J = 25^{\circ}C$, min/max: $-40^{\circ}C \le T_J \le 150^{\circ}C$, unless otherwise specified.) $T_A = T_J = 25^{\circ}C$, min/max: $-40^{\circ}C \le T_J \le 150^{\circ}C$, unless otherwise specified.) $T_A = T_J = 25^{\circ}C$, min/max: $-40^{\circ}C \le T_J \le 150^{\circ}C$, unless otherwise specified.) $T_A = T_J = 25^{\circ}C$, min/max: $-40^{\circ}C \le T_J \le 150^{\circ}C$, unless otherwise specified.) $T_A = T_J = 25^{\circ}C$, with $T_A = 25^{\circ}C$, wit$

| Parameter                                  | Conditions                                                                   | Symbol               | Min | Тур | Max | Unit             |

|--------------------------------------------|------------------------------------------------------------------------------|----------------------|-----|-----|-----|------------------|

| POWER GOOD (AS A PERCENTAGI                | E OF V <sub>OUT</sub> )                                                      |                      |     |     | _   |                  |

| PGOOD Assertion (V <sub>OUT</sub> Rising)  | Threshold                                                                    | V <sub>PG_ON</sub>   | _   | 90  | _   | %V <sub>FB</sub> |

|                                            | Accuracy                                                                     |                      | -2  | _   | 2   | 1                |

| PGOOD Leakage Current                      | V <sub>PGOOD</sub> = 5 V                                                     | I <sub>IOH_PG</sub>  | -   | _   | 1.0 | μΑ               |

| PGOOD Startup Delay                        | From end of soft-start (V <sub>OUT</sub> ramping) until PGOOD asserts        | T <sub>DH_PD</sub>   | -   | 560 | 720 | μs               |

| PGOOD De-Assert (V <sub>OUT</sub> Falling) | Threshold                                                                    | $V_{PG\_OFF}$        | -   | 84  | _   | %V <sub>FB</sub> |

|                                            | Accuracy                                                                     |                      | -2  | -   | 2   | 1                |

| PGOOD Low Voltage                          | I <sub>PGOOD</sub> = -4 mA (sinking)                                         | $V_{OL\_PG}$         | -   | -   | 0.3 | V                |

| PGOOD Shutdown Delay                       | Falling EN or V <sub>FB</sub> < POWER_GOOD_OFF until PGOOD de-asserts        | T <sub>DL_PD</sub>   | -   | 2   | 5   | μs               |

| AUTO RESTART                               |                                                                              |                      |     |     |     |                  |

| Automatic-Restart (Hiccup) Delay           | Setting                                                                      | T <sub>HCP</sub>     | -   | 32  | _   | ms               |

| Time                                       | Accuracy                                                                     |                      | -15 | _   | 20  | %                |

| POWER STAGE                                |                                                                              |                      |     |     |     |                  |

| High-Side MOSFET On Resistance             | V <sub>BST</sub> - V <sub>PHASE</sub> = 5 V                                  | R <sub>DS_HI</sub>   | -   | 1.8 | _   | mΩ               |

| Low-Side MOSFET On Resistance              | V <sub>PVCC</sub> = 5 V                                                      | R <sub>DS_LO</sub>   | -   | 0.8 | -   | mΩ               |

| High-Gate Pull-Up Resistance (Note 7)      | V <sub>BST</sub> – V <sub>PHASE</sub> = 5 V, I <sub>HG</sub> = 2 mA (source) | R <sub>HG_UP</sub>   | -   | 1.5 | -   | Ω                |

| High-Gate Pull-Down Resistance (Note 7)    | V <sub>BST</sub> - V <sub>PHASE</sub> = 5 V, I <sub>HG</sub> = 2 mA (sink)   | R <sub>HG_DN</sub>   | _   | 0.6 | -   | Ω                |

| Leading Edge Dead Time (Note 7)            | SW/PHASE rising, V <sub>BST</sub> – V <sub>PHASE</sub> = 5 V                 | T <sub>SWD_UP</sub>  | -   | 14  | _   | ns               |

| Low-Gate Pull-Up Resistance (Note 7)       | V <sub>PVCC</sub> = 5 V, I <sub>LG</sub> = 2 mA (source)                     | R <sub>LG_UP</sub>   | -   | 0.8 | -   | Ω                |

| Low-Gate Pull-Down Resistance (Note 7)     | V <sub>PVCC</sub> = 5 V, I <sub>LG</sub> = 2mA (sink)                        | R <sub>LG_DN</sub>   | -   | 0.4 | -   | Ω                |

| Trailing Edge Dead Time (Note 7)           | SW/PHASE falling, V <sub>PVCC</sub> = 5 V                                    | T <sub>SWD_DN</sub>  | -   | 9   | -   | ns               |

| BST Rectifier On Resistance                | V <sub>PVCC</sub> = 5 V, I <sub>F</sub> = 2 mA                               | R <sub>BST_ON</sub>  | -   | 50  | _   | Ω                |

| BST Rectifier Reverse Leakage<br>Current   | V <sub>PVCC</sub> = 5 V, V <sub>PHASE</sub> = 25 V                           | R <sub>BST_LKG</sub> | -   | _   | 3   | μΑ               |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

7. Performance over the indicated operating temperature range by design and/or characterization and may not be production tested.

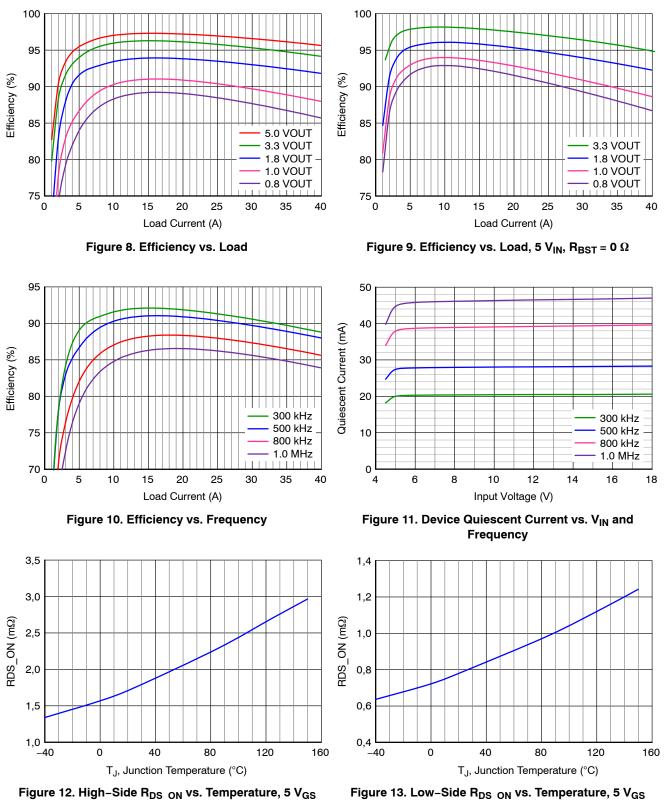

### TYPICAL PERFORMANCE CHARACTERISTICS

(RESULTS USE FIGURE 1 CIRCUIT,  $V_{IN}$  = 12 V,  $V_{OUT}$  = 1.0 V,  $F_{SW}$  = 500 KHZ,  $R_{BST}$  = 3.3  $\Omega$ ,  $T_A$  = 25°C, UNLESS OTHERWISE SPECIFIED. L AND C<sub>OUT</sub> VALUES (NOTE 8).)

Figure 13. Low-Side  $R_{DS\ ON}$  vs. Temperature, 5  $V_{GS}$

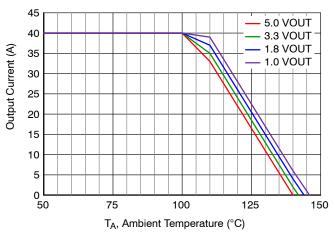

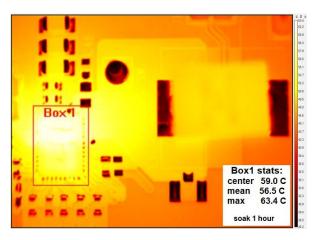

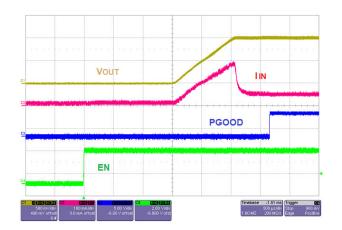

### TYPICAL PERFORMANCE CHARACTERISTICS (CONTINUED)

Figure 14. Thermal Safe Operating Area, No Airflow

Figure 15. Thermal Image, No Airflow, I<sub>OUT</sub> = 40 A

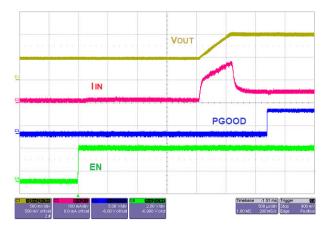

Figure 16. Start-Up, No Load,  $R_{SS/MODE1} = 10 \text{ k}\Omega$

Figure 17. Pre-Bias Start-Up, No Load,  ${\rm R_{SS/MODE1}} = {\rm 10~k}\Omega$

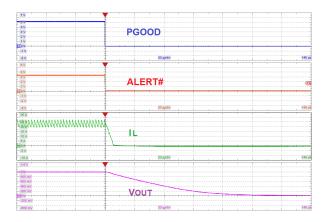

Figure 18. Over–Current Protection Response, Latch–Off,  $I_{VLY} = 20 \text{ A}$

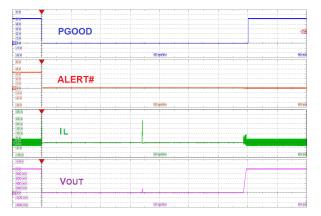

Figure 19. Over–Current Protection Response and Auto–Restart, Hiccup, I<sub>VLY</sub> = 20 A

### TYPICAL PERFORMANCE CHARACTERISTICS (CONTINUED)

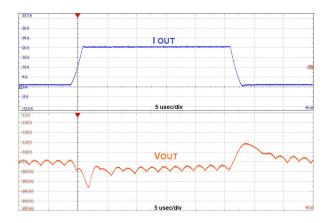

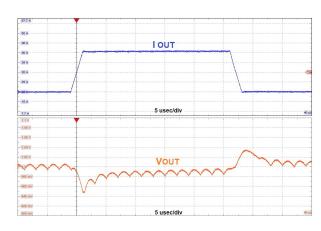

Figure 20. Load Transient Response, 1 – 21 A, 10 A/μs

Figure 21. Load Transient Response, 20 – 40 A,  $10~A/\mu s$

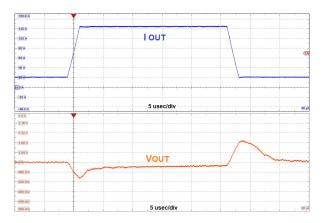

Figure 22. 4-Phase Load Transient Response, 20 – 125 A, 50 A/μs

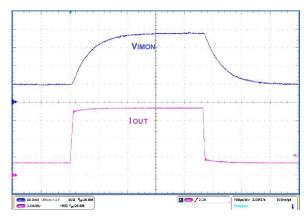

Figure 23. Dynamic IMON Tracking, 3 – 11 A, 1 A/ $\mu s$

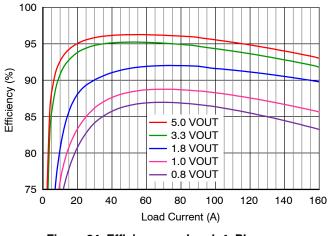

Figure 24. Efficiency vs. Load, 4-Phase

Figure 25. IMON Accuracy vs. Load

| INCIL | Ν | O. | Т | Ε |

|-------|---|----|---|---|

|-------|---|----|---|---|

| - 11 | IOTL.                                |               |                     |         |           |               |                     |                      |

|------|--------------------------------------|---------------|---------------------|---------|-----------|---------------|---------------------|----------------------|

| 8    | . C <sub>OUT</sub> used for testing: | <u>Phases</u> | Capacitance         | L used: | $V_{OUT}$ | <u>L (nH)</u> | DCR ( $\mu\Omega$ ) | Supplier             |

|      |                                      | 1             | 20  22 μF ceramic + |         | <1.5      | 210           | 290                 | Eaton FP1108R1-R21-R |

|      |                                      |               | 2  470 μF poscap    |         | 1.8       | 330           | 155                 | Wurth 744305033      |

|      |                                      | 4             | 20  22 μF ceramic + |         | 3.3       | 560           | 1,400               | Wurth 744373770056   |

|      |                                      |               | 6  470 μF poscap    |         | 5.0       | 1,000         | 2,300               | Pulse PA4343.102NLT  |

### APPLICATION INFORMATION

### General

The NCP3296, a highly efficient stackable synchronous buck regulator, is capable of operating over an input voltage range of 3.0 V to 18 V, supporting load currents up to 40 A. Higher output currents can be achieved by paralleling up to four NCP3296 devices.

The NCP3296 employs a fixed frequency current mode control scheme to provide accurate voltage regulation and fast transient response. Flexible programmability of function and parameters support multiple applications.

### **VOUT Scale Loop Setting**

For  $V_{OUT}$  Scale other than 1, a resistor divider of equivalent ratio is required from  $V_{OUT}$  to FB to VSNS-.

Using Table 2, select the value ( $R_{PIN}$ ) for  $R_{SS/MODE1}$  corresponding to the desired  $V_{OUT}$  Scale level and soft–start time ( $T_{SS}$ ).

### **V<sub>OUT</sub>** Setting

Use Table 2 to select the value ( $R_{PIN}$ ) for  $R_{VSET/FAULT}$  corresponding to the desired  $V_{OUT}$  level for the previously established  $V_{OUT}$  Scale setting.

### **Setting Frequency**

Use Table 2 to select the value (R<sub>PIN</sub>) for R<sub>SYNC/FSET</sub> associated with the desired switching frequency per phase and the total number of phases to be implemented.

### **Current Limit Setting**

The per phase current limit setting ( $I_{VLY}$ ) and protection mode (hiccup/latch-off) are established by  $R_{IMON/ILIM}$ , according to the  $R_{PIN}$  value ( $R_{PIN}$ ) shown in Table 2.

### Master/Slave Configuration

The NCP3296 can be configured as either a master or slave in an interleaved, multi-phase POL system, by its FB and VSNS- pin configuration, as shown in Table 1.

**Table 1. MASTER/SLAVE CONFIGURATION**

|                       | FB               | VSNS-        | Application      |

|-----------------------|------------------|--------------|------------------|

| Master                | V <sub>OUT</sub> | GND          | 1, 2, 3, 4 phase |

| 1 <sup>st</sup> Slave | VCC              | GND          | 2, 3, 4 phase    |

| 2 <sup>nd</sup> Slave | VCC              | VCC          | 3, 4 phase       |

| 3 <sup>rd</sup> Slave | VCC              | 100 kΩ – GND | 4 phase          |

### **Operation Modes**

Device operating mode is determined by 1% resistor selection ( $R_{PIN}$ ) at the appropriate device pin, as shown in Table 2.

**Table 2. OPERATING MODE SELECTION**

|                          | R <sub>V</sub> | SET/FAULT F                              | Pin                          | R <sub>SS/MO</sub>      | <sub>DE1</sub> Pin                                    | R <sub>IMON/ILIM</sub> Pin                             | R <sub>MODE2/S</sub> | FAULT Pin                   |             | R <sub>SYNC/FSET</sub> Pir |             |             |     |

|--------------------------|----------------|------------------------------------------|------------------------------|-------------------------|-------------------------------------------------------|--------------------------------------------------------|----------------------|-----------------------------|-------------|----------------------------|-------------|-------------|-----|

|                          |                | Set V <sub>OUT</sub>                     |                              |                         | <sub>JT</sub> Scale<br>ft–Start<br>(T <sub>SS</sub> ) | Set Current<br>Limit (I <sub>VLY</sub> ),<br>per Phase | and Pro              | se Count<br>otection<br>ode | Set         | Set Frequency (F           |             | , per       |     |

| R <sub>PIN</sub><br>(kΩ) | 1 Scale<br>(V) | <sup>1</sup> / <sub>2</sub> Scale<br>(V) | 1/ <sub>4</sub> Scale<br>(V) | T <sub>SS</sub><br>(ms) | V <sub>OUT</sub> -<br>Scale (N)                       | I <sub>LIM</sub><br>(A)                                | Phases<br>(N)        | Mode                        | 1φ<br>(kHz) | 2φ<br>(kHz)                | 3φ<br>(kHz) | 4φ<br>(kHz) |     |

| 10.0                     | 0.50           | 1.30                                     | 2.40                         | 1                       | 1                                                     | 10                                                     | 1 phase              | Hiccup                      | 200         | 200                        | 200         | 200         |     |

| 15.0                     | 0.55           | 1.35                                     | 2.50                         | 3                       |                                                       | 12                                                     | (1φ)                 | _                           |             | 250                        | 250         | 250         | 250 |

| 18.2                     | 0.60           | 1.40                                     | 2.60                         | 5                       |                                                       | 14                                                     |                      |                             | Latch-Off   | 300                        | 300         | 300         | 300 |

| 22.1                     | 0.65           | 1.45                                     | 2.70                         | 10                      |                                                       | 16                                                     |                      |                             | 350         | 350                        | 350         | 350         |     |

| 27.4                     | 0.70           | 1.50                                     | 2.80                         | 15                      |                                                       | 18                                                     | 2 phase              | Hiccup                      | 400         | 400                        | 400         | 400         |     |

| 33.2                     | 0.75           | 1.55                                     | 2.90                         | 1                       | 1/2                                                   | 20                                                     | (2φ)                 |                             | 500         | 450                        | 450         | 450         |     |

| 39.2                     | 0.80           | 1.60                                     | 3.00                         | 3                       |                                                       | 24                                                     |                      |                             | Latch-Off   | 600                        | 500         | 500         | 500 |

| 47.5                     | 0.85           | 1.65                                     | 3.10                         | 5                       |                                                       | 28                                                     |                      |                             | 700         | 550                        | 550         |             |     |

| 56.2                     | 0.90           | 1.70                                     | 3.20                         | 10                      |                                                       | 32                                                     | 3 phase              | e Hiccup                    | 800         | 600                        | 600         |             |     |

| 68.1                     | 0.95           | 1.75                                     | 3.30                         | 15                      |                                                       | 36                                                     | (3φ)                 |                             | 900         | 650                        | 650         |             |     |

| 82.5                     | 1.00           | 1.80                                     | 3.40                         | 1                       | 1/4                                                   | 40                                                     |                      | Latch-Off                   | 1,000       | 700                        |             |             |     |

| 100                      | 1.05           | 1.90                                     | 3.50                         | 3                       |                                                       | 44                                                     |                      |                             | 1,200       | 750                        |             |             |     |

| 121                      | 1.10           | 2.00                                     | 4.00                         | 5                       |                                                       | 48                                                     | 4 phase              | Hiccup                      | 1,400       | 800                        |             |             |     |

| 150                      | 1.15           | 2.10                                     | 4.50                         | 10                      |                                                       | 52                                                     | (4φ)                 |                             | 1,600       | 850                        |             |             |     |

| 182                      | 1.20           | 2.20                                     | 5.00                         | 15                      |                                                       | 56                                                     |                      | Latch-Off                   | 1,800       | 900                        |             |             |     |

| 221                      | 1.25           | 2.30                                     | 5.50                         | 20                      | 1                                                     | 60                                                     |                      |                             | 2,000       | 1,000                      |             |             |     |

The use of substitute resistor values is not recommended.

### **Soft Start**

The NCP3296 soft–start function allows starting into a pre–biased output. When the device is enabled, the soft–start ramp time (T<sub>SS</sub>) begins after a fixed delay (T<sub>ON DLY</sub>).

During the soft-start ramp, switching is prevented when pre-biased  $V_{FB}$  exceeds the target reference voltage. At the end of soft-start, if  $V_{FB}$  continues to be greater than the programmed reference level, switching will commence to bring the output into compliance.

When the device is disabled, or at falling UVLO, the device shuts down immediately and the power MOSFETs are forced off.

### **Enable**

The NCP3296 is enabled when the rising EN voltage  $(V_{EN\ H})$  exceeds  $V_{EN\ TH}$ , as illustrated below:

Figure 26. Enable Thresholds and Hysteresis

Optional  $R_{\rm EN}$  can be added externally to increase the amount of hysteresis to reach the falling threshold. The falling threshold can be calculated by:

$$V_{EN\_L} = V_{EN\_TH} - I_{HYS} \cdot (R_{HYS} + R_{EN})$$

(eq. 1)

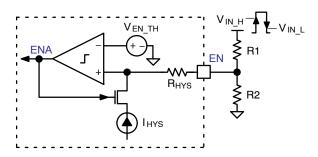

The EN pin can also be used to implement an input supply UVLO function using the circuit below:

Figure 27. EN Pin Input UVLO Circuit

The associated rising and falling V<sub>IN</sub> thresholds are:

$$V_{IN\_H} = V_{EN\_TH} \cdot \left(\frac{R1}{R2} + 1\right) \tag{eq. 2}$$

$$V_{IN\_L} = K + R1 \cdot \left(\frac{K}{R2} - I_{HYS}\right)$$

(eq. 3)

where:

$$K = V_{EN\_TH} - I_{HYS} \cdot R_{HYS}$$

(eq. 4)

To avoid unintended or undefined operation, the EN pin should not be left floating in the application.

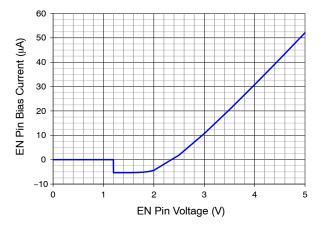

Figure 28. Typical EN Pin Bias Current

### **Over-Current Protection (OCP)**

The NCP3296 employs a cycle-by-cycle valley current limit ( $I_{VLY}$ ) threshold to protect the regulator. The average current limit ( $I_{LIM}$ ) value can be calculated from the inductor ripple current and  $I_{VLY}$  using:

$$I_{LIM} = I_{VLY} + \frac{V_{OUT} \cdot (V_{IN} - V_{OUT})}{2 \cdot V_{IN} \cdot L \cdot F_{SW}}$$

(eq. 5)

OCP detection starts at the beginning of the soft–start ramp ( $T_{SS}$ ) and extends until shutdown. Inductor current is monitored between SW and PGND. If the OCP event lasts for more than 32 consecutive switching cycles, the device enters fault state (hiccup or latch–off). If  $V_{OUT}$  is falling rapidly, the device may trip under–voltage protection before the 32 current limit cycles accumulate.

To restart the device from an OCP latch-off condition, the system needs to toggle VCC or EN off, then back on.

### **Output Under-Voltage Protection (UVP)**

UVP detection is active from when PGOOD asserts at the end of soft–start, until shutdown. The NCP3296 will force PGOOD low and turn off both power MOSFETs once the FB pin voltage falls below  $V_{\rm UVP\_TH}$  threshold for more than  $T_{\rm D~UVP}$ .

To restart the device after a UVP latch-off, the system needs to toggle VCC or EN off, and then back on.

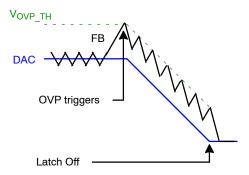

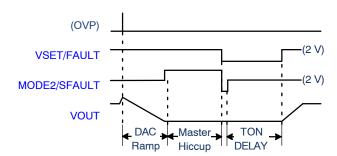

### **Output Over-Voltage Protection (OVP)**

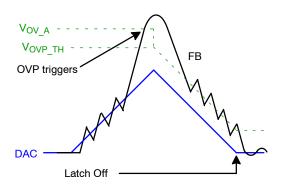

The NCP3296 offers output over-voltage protection to protect the regulator and prevent the possible destruction of the downstream load. OVP is active from the beginning of soft-start until shutdown, latch-off, or during hiccup idle time.

During operation, if the FB pin voltage exceeds the  $V_{OVP\_TH}$  threshold for longer than  $T_{D\_OVP}$ , OVP is triggered and PGOOD is forced low.

Once OVP triggers, FCCM operation is maintained while the DAC voltage ramps down at the T<sub>OFF</sub> rate, preventing large negative voltage spikes from occurring at the output. Once the DAC reaches 0, the high-side FET is turned off, while the low-side FET remains on.

Figure 29. OVP Behavior during Normal Operation

During soft–start, the OVP threshold is set to a fixed absolute value of  $V_{\rm OV\ A}$ .

Figure 30. OVP Behavior during Start-Up

To restart the device after an OVP latch-off, the system needs to toggle VCC or EN off, and then back on.

### Thermal Shutdown (T<sub>SD</sub>)

Severe overheating is prevented by forcing the entire device into shutdown when die temperature  $(T_J)$  reaches the thermal shutdown threshold  $(T_{SD})$ .  $T_{SD}$  detection activates when VCC and EN are valid. Once the thermal protection is triggered, the entire chip remains off until  $T_J$  cools to  $T_{RST}$ , where an automatic recovery and soft–start sequence commence.

### Input Over-Voltage Protection (V<sub>IN</sub> OVP)

When the input voltage, measured at the PVIN pin, exceeds the  $V_{PVIN\_OVP}$  threshold for the de-bounce time of  $T_{D\ VINOV}$ , the device enters fault state and switching ceases.

Once the input voltage falls below  $V_{PVIN\_OVP} - V_{PVIN\_HYS}$ , an automatic restart occurs after a fixed 32 ms delay.

### Hiccup / Latch-Off Mode

The selected resistor value at the MODE2/SFAULT pin  $(R_{MODE2/SFAULT})$  determines whether hiccup or latch-off protection mode is applied under  $V_{OUT}$  OVP,  $V_{OUT}$  UVP, or OCP conditions.

To restart a device in latch–off mode, EN or VCC need to be toggled. In hiccup mode, the idle time counter ( $T_{HCP}$ ) begins counting when the device shuts down for OCP, UVP, or the end of OVP DAC ramp down. A normal start–up sequence automatically occurs once  $T_{HCP}$  expires.

### **PGOOD Pin**

The PGOOD signal is held low during soft-start and in shutdown state.

PGOOD is high while  $V_{FB}$  remains within the adjustable regulation envelope determined by the  $V_{OVP\_TH}$  and  $V_{UVP\ TH}$  thresholds.

During thermal shutdown (T<sub>SD</sub>), PGOOD is low until the device sufficiently cools. PGOOD will be low during all fault conditions.

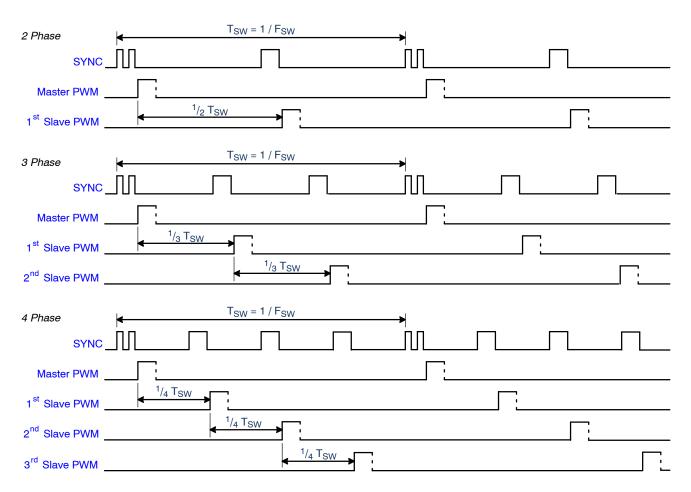

### Multi-Phase Frequency and Synchronization

Per phase switching frequency ( $F_{SW}$ ) and phase count (N) are programmed by  $R_{SYNC/FSET}$  and  $R_{MODE2/SFAULT}$  resistor value selections per Table 2. The sequential interleave order of the slave phases is determined by FB and VSNS- pin connections shown in Table 1.

In a multi-phase system, the master outputs a SYNC signal to the parallel slaves' SYNC pins to establish a common switching frequency and evenly space the interleaved phases, as shown in the subsequent figure:

The falling edge of the SYNC pulse resets the ramp, beginning the interleaved PWM on cycles after a narrow propagation delay. The vertical dotted lines signify the modulated PWM edge (duty cycle).

Figure 31. Multi-Phase Synchronization Timing

### **FAULT and SFAULT Operation**

In a multi-phase application, communication between the master and slaves is accomplished via signaling over the VSET/FAULT and MODE2/SFAULT pins.

The following table is a summary of NCP3296 actions in response to the main fault conditions:

Table 3. MASTER / SLAVE ACTIONS BY PROTECTION TYPE

| Master / Standalone |                                                                                                     | Protection |  | Slave                  |                                                                                      |  |

|---------------------|-----------------------------------------------------------------------------------------------------|------------|--|------------------------|--------------------------------------------------------------------------------------|--|

| Detection           | Action                                                                                              | Туре       |  | Detection              | Action                                                                               |  |

| V <sub>CC</sub>     | Auto recoverable Both power MOSFETS off FAULT pulled high SFAULT pulled low                         | UVLO       |  | V <sub>CC</sub>        | Auto recoverable Both power MOSFETS off FAULT pulled high SFAULT pulled low          |  |

| T <sub>J</sub>      | Auto recoverable Both power MOSFETS off FAULT pulled low                                            | TSD        |  | TJ                     | Auto recoverable<br>Both power MOSFETS off<br>SFAULT pulled low                      |  |

| I <sub>DRAIN</sub>  | Cycle-by-cycle current limit<br>Both power MOSFETS off<br>FAULT pulled low                          | OCP        |  | I <sub>DRAIN</sub>     | Cycle-by-cycle current limit<br>Both power MOSFETS off<br>SFAULT pulled low          |  |

| $V_{FB}$            | Both power MOSFETS off FAULT pulled low                                                             | UVP        |  | Master V <sub>FB</sub> | Both power MOSFETS off after<br>Master pulls FAULT low                               |  |

| V <sub>FB</sub>     | Ramp down DAC with FCCM<br>High-side FET turns off<br>Low-side FET remains on<br>SFAULT pulled high | OVP        |  | Master V <sub>FB</sub> | Once Master pulls SFAULT high:<br>High-side FET turns off<br>Low-side FET remains on |  |

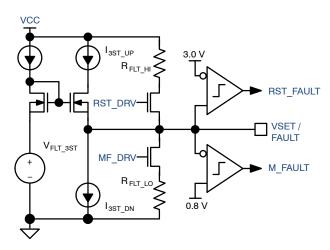

### **FAULT and SFAULT Signaling**

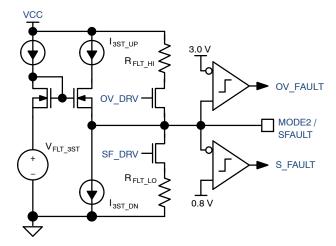

The VSET/FAULT and MODE2/SFAULT pins utilize bi-directional signaling for master/slave communication and fault management. The figures below illustrate how the circuit works:

Figure 32. VSET/FAULT Pin Circuit

The internal signal MF\_DRV asserts high when a master fault occurs. RST\_DRV gets asserted to reset the system. M\_FAULT and RST\_FAULT are the associated fault signals (active high).

Figure 33. MODE2/SFAULT Pin Circuit

The internal signal OV\_DRV asserts when the master detects an output OVP event, which forces the MODE2/SFAULT pin high. SF\_DRV asserts when a slave needs to signal a fault condition. OV\_FAULT and S\_FAULT are the associated fault signals (active high).

When EN=0, the master forces both VSET/FAULT and MODE2/SFAULT low. Switching is prohibited.

The VSET/FAULT and MODE2/SFAULT signals remain tri-stated (2 V) during normal operation.

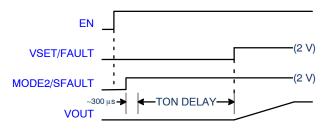

Figure 34. Master/Slave Start-Up Signals

At start-up, once EN is asserted, the master imposes a small housekeeping delay before tri-stating the MODE2/SFAULT pin, which awakens the slaves. While VSET/FAULT is low, all the master and slave FETs remain off

After the TON\_DELAY period expires, the master tri-states the VSET/FAULT pin and the soft-start cycle begins.

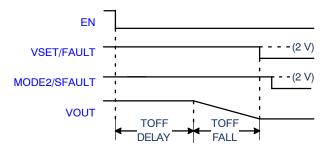

Figure 35. Master/Slave Power-Off Signals

When EN goes low, the VSET/FAULT and MODE2/SFAULT pins remain tri-stated until the TOFF\_DELAY and TOFF\_FALL intervals expire. Then, the master lowers the VSET/FAULT pin which halts switching and all FETs are turned off. Later, the master lowers the MODE2/SFAULT pin, returning the slaves to their stand-by (inactive) state.

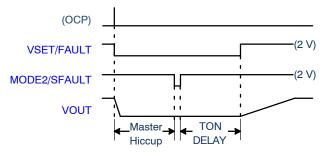

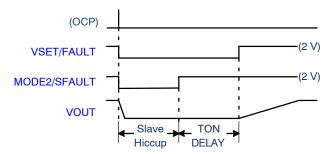

Figure 36. Master/Slave Signals, Master OCP or UVP

When the master encounters an over-current fault situation, indicated here by internal logic signal (OCP) high, it lowers the VSET/FAULT pin to instruct slaves to stop switching.

Once the master completes its hiccup cycle, it momentarily cycles MODE2/SFAULT low to reset and re-activate slaves.

Upon expiration of the TON\_DELAY interval, the master tri-stats the VSET/FAULT pin and a soft-start cycle commences.

The same signaling/sequence is used in response to output under-voltage (UVP) faults.

Figure 37. Master/Slave Signals, Slave OCP or OT Fault

When any slave encounters an over-current event, it signals the master by lowering the MODE2/SFAULT pin. As a result, the master forces VSET/FAULT low to halt all switching.

Once the slave hiccup period expires, it releases the MODE2/SFAULT signal. The master holds VSET/FAULT low to prevent all switching until TON\_DELAY elapses. When the master releases the VSET/FAULT signal to the tri-state level, the soft-start cycle commences.

The same signaling/sequence is used in response to an over-temperature (OT) fault.

Figure 38. Master/Slave Signals, OVP Fault

In the event of an output over-voltage fault (OVP), the VSET/FAULT and MODE2/SFAULT pins both remain at 2 V until the DAC ramps down the output in a controlled fashion.

During the hiccup interval, the master pulls MODE2/SFAULT high, instructing the slaves to turn off high-side FETs and enhance low-side FETs.

After the hiccup cycle, the master forces both signals low, momentarily, which resets the slaves. Slaves re-activate when the master releases the MODE2/SFAULT signal during the TON\_DELAY interval. When the master releases the VSET/FAULT signal, the re-start ramp begins.

### Operating / Fault States

The table below provides a summary of device and pin states during operating and/or fault conditions:

### **Table 4. STATE TRUTH TABLE**

|                                                                            | Action / Function |          |                |                                               |                       |  |  |