# QUAD CHANNEL EXTERNAL NMOS FET HIGH CURRENT AUTOMOTIVE LED CONTROLLER WITH INTERNAL PWM DIMMING

April 2024

#### **GENERAL DESCRIPTION**

The IS32LT3123 is a quad channel linear controller capable of accurately regulating LED current with external NMOS FETs. It integrates PWM dimming for two LED brightness levels for RCL (Rear Combination Lamp) or DRL (Daytime Running Lamp) applications. It is fully programmable with two LED brightness levels for the different intensity requirements, such as "Stop" (full brightness) and "Tail" dim (PWM dimming). A logic level at the PWMB pin is used to switch between the two brightness levels. A logic high provides the highest intensity output, while a logic low utilizes an internally generated PWM signal to reduce the intensity of the LEDs' light output.

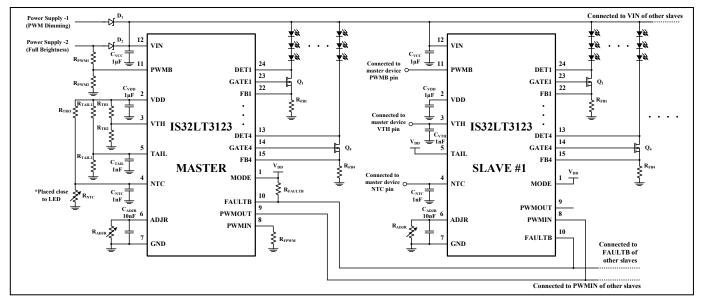

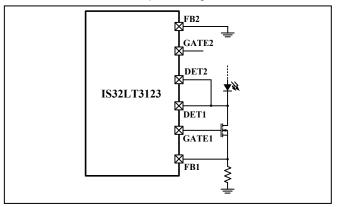

Multiple devices also can be connected in parallel in a master-slave structure for larger lighting applications.

For added system reliability, the IS32LT3123 integrates fault detection circuitry for LED open/short circuit, input over voltage and over temperature conditions. The FAULTB pin is dedicated to the fault conditions reporting and the MODE pin can control the action of the device in case of a fault condition.

The device also supports the NTC resister to monitor the LED string temperature. In case of the temperature exceeds the setting threshold, the device will reduce the drive current to protect the LED string.

The device package is an eTSSOP-24 with exposed pad for enhanced thermal dissipation.

#### **FEATURES**

- Low side external NMOS FETs support high output current with independent current setting

- One resistor to simultaneously adjust all channels for LED binning

- 200mV reference feedback voltage for high efficiency

- ±4% current accuracy over -40°C ~125°C

- 5.0V to 40V supply voltage

- PWMB voltage input to select between full brightness and PWM dimming

- Flexible LED PWM dimming options

- Internal PWM dimming set by resistors

- ✓ Programmable duty cycle, 5%~95%

- ✓ Programmable frequency, 100Hz~1kHz

- External PWM signal input dimming

- Analog voltage input for PWM dimming

- PWM slew rate control on each output to optimize EMI performance

- Robust fault protection

- Fault reporting

- ✓ LED string open/short

- √ Thermal shutdown

- LED string over temperature thermal rolloff

- Input over voltage current derating

- Controller junction over temperature thermal rolloff

- Multiple parallel IC operation for higher number of strings with fault condition and PWM dimming sync

- RoHS & Halogen-Free Compliance

- TSCA Compliance

- AEC-Q100 Qualified with Temperature Grade 1: -40°C to 125°C

#### **APPLICATIONS**

- Automotive and avionic lighting

- Rear combination light (STOP/TAIL lights)

- · Center high mounted stop light

- Position light

- Daytime running light (DRL)

- Turn light

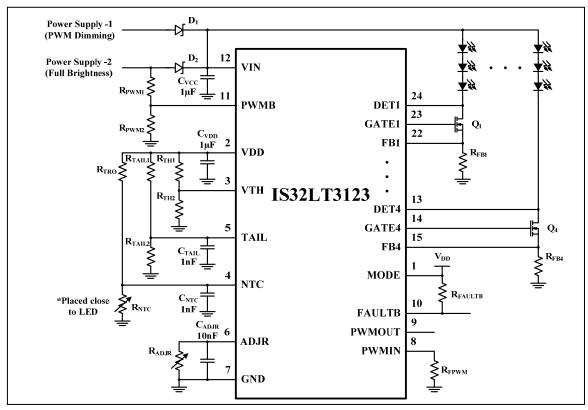

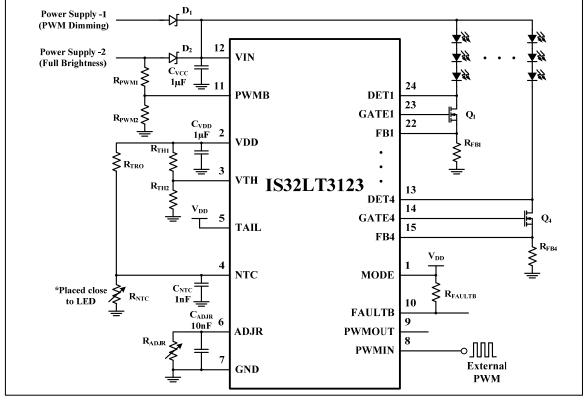

# **TYPICAL APPLICATION CIRCUIT**

Figure 1 Typical Application Circuit of Internal PWM Dimming

Figure 2 Typical Application Circuit of External PWM Dimming

Figure 3 Typical Application Circuit of Analog Input PWM Dimming

Figure 4 Typical Application Circuit of Several Devices in Parallel (one master with several slaves)

# **PIN CONFIGURATION**

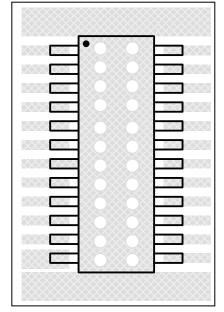

| Package Pin Configuration (Top View) |                                                             |   |                                                                                                         |  |  |  |  |  |

|--------------------------------------|-------------------------------------------------------------|---|---------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| eTSSOP-24                            | MODE VDD VTH NTC TAIL ADJR GND PWMIN PWMOUT FAULTB PWMB VIN | 1 | DET1  23 GATE1  22 FB1  21 FB2  20 GATE2  19 DET2  18 DET3  17 GATE3  16 FB3  15 FB4  14 GATE4  13 DET4 |  |  |  |  |  |

### PIN DESCRIPTION

| No.        | Pin           | Function                                                                                                                                                                                                                                                                                                                                  |

|------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | MODE          | MODE pin decides the fault mode. Tie to VDD or GND. Do not leave unconnected.                                                                                                                                                                                                                                                             |

| 2          | VDD           | Internal LDO output. Connect to GND through a 1µF X7R capacitor which should be placed as close to VDD pin as possible. It is capable to drive external circuitry with minimum 14mA current capability.                                                                                                                                   |

| 3          | VTH           | Voltage at this pin sets the $V_{\text{IN}}$ over voltage current derating threshold and the $V_{\text{IN}}$ threshold for open LED fault detect.                                                                                                                                                                                         |

| 4          | NTC           | Connect the NTC resistor divider to set the temperature threshold for the LED string temperature monitor. As long as the temperature exceeds the threshold, the reference voltage will be derated linearly according to NTC pin voltage.                                                                                                  |

| 5          | TAIL          | Connect to an external DC voltage below 3.7V for internal PWM mode to adjust operating duty cycle.  Connect TAIL pin to VDD for external PWM mode. PWM duty cycle is controlled by the PWM signal on PWMIN pin.                                                                                                                           |

| 6          | ADJR          | Connect a proper value resistor from this pin to GND to set the Internal reference voltage.                                                                                                                                                                                                                                               |

| 7          | GND           | Ground pin.                                                                                                                                                                                                                                                                                                                               |

| 8          | PWMIN         | In internal PWM mode (TAIL pin voltage < 3.7V), the frequency of PWM is set by a resistor from PWMIN to GND.  In external PWM mode (TAIL pin is connected to VDD), PWM frequency and duty cycle are determined by external PWM signal on PWMIN pin.                                                                                       |

| 9          | PWMOUT        | PWM signal output pin. In internal PWM mode, the output PWM signal is internal PWM generator. In external PWM mode, the output PWM signal is sync with PWMIN pin.                                                                                                                                                                         |

| 10         | FAULTB        | Open drain I/O diagnostic pin. Active low output driven by the device when it detects a fault condition. As an input (MODE pin high), this pin will accept an externally generated FAULTB signal to disable the device output to satisfy the "One-Fail-All-Fail" function. Note this pin requires an external pull up resistor (RFAULTB). |

| 11         | PWMB          | Full brightness mode select input. When PWMB pin is low, the device is in PWM dimming mode and the output is dimming by the internal or external PWM signal. When PWMB pin is high, the device is in full brightness mode, NMOS FET current 100% duty cycle operation. And the internal and external PWM signal are overridden.           |

| 12         | VIN           | Power input for the IC.                                                                                                                                                                                                                                                                                                                   |

| 24,19,18,1 | 3 DET1/2/3/4  | Detect NMOS FET drain voltage for channel 1/2/3/4 LED string open/short faults. If any channel is unused, connect its DET pin to used DET pin. For example, if channel 1/2 are used and channel 3/4 are not used. DET1/2 is connected to the drain of their NMOS FETs. DET3/4 can be connected to DET1 or DET2.                           |

| 23,20,17,1 | 4 GATE1/2/3/4 | Gate driver for external NMOS FET1/2/3/4.                                                                                                                                                                                                                                                                                                 |

| 22,21,16,1 | 5 FB1/2/3/4   | Current sense for channel 1/2/3/4. Connect sense resistors to independently set current level of channel 1/2/3/4.                                                                                                                                                                                                                         |

|            | Thermal Pad   | Must be connected to GND with sufficient copper plate for heat sink.                                                                                                                                                                                                                                                                      |

**ORDERING INFORMATION**

Automotive Range: -40°C to +125°C

| Order Part No.     | Package              | QTY/Reel |  |  |

|--------------------|----------------------|----------|--|--|

| IS32LT3123-ZLA3-TR | eTSSOP-24, Lead-free | 2500     |  |  |

Copyright © 2024 Lumissil Microsystems. All rights reserved. Lumissil Microsystems reserves the right to make changes to this specification and its products at any time without notice. Lumissil Microsystems assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any published information and before placing orders for products.

Lumissil Microsystems does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless Lumissil Microsystems receives written assurance to its satisfaction, that:

- a.) the risk of injury or damage has been minimized;

- b.) the user assume all such risks; and

- c.) potential liability of Lumissil Microsystems is adequately protected under the circumstances

**ABSOLUTE MAXIMUM RATINGS (NOTE 1)**

| Voltage at VIN                                                                                                    | -0.3V ~ +42V                   |

|-------------------------------------------------------------------------------------------------------------------|--------------------------------|

| Voltage at PWMB, FAULTB, DET1~4, PWMIN                                                                            | -0.3V ~ +V <sub>IN</sub> +0.3V |

| Voltage at GATE1~4, FB1~4, PWMOUT                                                                                 | -0.3V ~ +20V                   |

| Voltage at VDD, VTH, ADJR, NTC, TAIL, MODE                                                                        | -0.3V ~ +7V                    |

| Operating temperature, T <sub>A</sub> =T <sub>J</sub>                                                             | -40°C ~ +150°C                 |

| Storage temperature, T <sub>STG</sub>                                                                             | -65°C ~ +150°C                 |

| Junction temperature, T <sub>JMAX</sub>                                                                           | +150°C                         |

| Package thermal resistance, junction to ambient (4-layer standard test PCB based on JESD 51-2A), $\theta_{JA}$    | 28.1°C/W                       |

| Package thermal resistance, junction to thermal PAD (4-layer standard test PCB based on JESD 51-8), $\theta_{JP}$ | 8.55°C/W                       |

| ESD (HBM)                                                                                                         | ±2kV                           |

| ESD (CDM)                                                                                                         | ±750V                          |

**Note 1:** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other condition beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

Valid at V<sub>IN</sub>= 7V ∼ 19V

"•" symbol indicates specifications across the full operating temperature range with  $T_A$ =  $T_J$ = -40°C to +125°C, other specifications are at  $T_A$ =  $T_J$ = 25°C; unless noted otherwise.

| Symbol              | Parameter                                          | Conditions                                                                                           |   | Min. | Тур. | Max. | Unit |

|---------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------------|---|------|------|------|------|

| Input Sup           | ply                                                |                                                                                                      |   |      |      |      |      |

| $V_{\text{IN}}$     | Operating input voltage range                      |                                                                                                      | • | 5.0  |      | 40   | V    |

| V <sub>IN_UV</sub>  | V <sub>IN</sub> undervoltage release               | VIN rising                                                                                           |   |      | 4.5  |      | V    |

| VIN_UVHY            | V <sub>IN</sub> undervoltage lockout<br>hysteresis | IC disabled                                                                                          |   |      | 0.15 |      | V    |

| l <sub>IN</sub>     | VIN operational current                            | V <sub>NTC</sub> =V <sub>VTH</sub> =V <sub>TAIL</sub> =V <sub>DD</sub> ,<br>PWMB=High                | • |      |      | 13   | mA   |

| t <sub>ON</sub>     | Startup time                                       | V <sub>IN</sub> >7V, C <sub>VDD</sub> = 10μF,<br>V <sub>FB</sub> = 20mV, PWMB=High                   |   |      | 200  |      | μs   |

| Current R           | egulation                                          |                                                                                                      |   |      |      |      |      |

| V                   | Maximum reference voltage on FB                    | V <sub>VTH</sub> =V <sub>NTC</sub> =V <sub>ADJR</sub> =V <sub>DD</sub>                               | • | 192  | 200  | 208  | m\/  |

| $V_{REFMAX}$        | pins                                               | V <sub>VTH</sub> =V <sub>NTC</sub> =V <sub>ADJR</sub> =V <sub>DD</sub>                               |   | 194  | 200  | 206  | mV   |

| $V_{REFDR}$         | VIN over voltage derating for reference voltage    | V <sub>VTH</sub> = 2V, V <sub>NTC</sub> =V <sub>ADJR</sub> =V <sub>DD</sub><br>V <sub>IN</sub> ≥ 26V |   |      | 51   |      | %    |

| Errvref             | Matching between FB voltage (Note 2)               | V <sub>VTH</sub> =V <sub>NTC</sub> =V <sub>ADJR</sub> =V <sub>DD</sub>                               |   |      |      | 2    | %    |

| VREFADJR            | Reference voltage adjusted by ADJR pin             | V <sub>VTH</sub> =V <sub>NTC</sub> =V <sub>DD</sub> , R <sub>ADJR</sub> =2kΩ                         | • | 122  | 132  | 142  | mV   |

| $V_{DD}$            | VDD pin voltage output                             | I <sub>VDD</sub> = 10mA                                                                              | • | 5.0  | 5.25 | 5.5  | V    |

| I <sub>DD_LIM</sub> | VDD pin output current limit                       |                                                                                                      | • | 14   |      |      | mA   |

# **ELECTRICAL CHARACTERISTICS (CONTINUE)**

Valid at  $V_{IN}$ = 7V ~ 19V

"●" symbol indicates specifications across the full operating temperature range with T<sub>A</sub>= T<sub>J</sub>= -40°C to +125°C, other specifications are at T<sub>A</sub>= T<sub>J</sub>= 25°C; unless noted otherwise.

| Symbol             | Parameter                                                        | Min.                                                                                                 | Тур. | Max. | Unit  |      |    |

|--------------------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|------|------|-------|------|----|

| Gate Driv          | er                                                               |                                                                                                      |      |      | •     | •    |    |

| $V_{GATEH}$        | GATE high-level output                                           | V <sub>IN</sub> = 12V, PWMIN=High,<br>V <sub>FB</sub> = 150mV, V <sub>TAIL</sub> = V <sub>DD</sub>   |      | 6    |       | 8    | V  |

| VGATEL             | GATE low-level output                                            | PWMIN= Low, PWMB=Low                                                                                 |      |      |       | 0.2  | V  |

| $V_{GATED}$        | GATE driver dropout                                              | V <sub>IN</sub> = 7V, V <sub>FB</sub> = 150mV,<br>measured as (V <sub>IN</sub> - V <sub>GATE</sub> ) |      |      | 1.65  |      | V  |

| I <sub>GPU</sub>   | Gate pull-up current                                             | $V_{FB}$ = 180mV, $V_{GATE}$ = 0V, $V_{IN}$ = 7V                                                     |      |      | -0.92 |      | mA |

| I <sub>GPD</sub>   | Gate pull-down current                                           | $V_{FB}$ = 220mV, $V_{GATE}$ = 7V, $V_{IN}$ = 7V                                                     |      |      | 8.8   |      | mA |

| C <sub>GISS</sub>  | External NMOS FET gate capacitance range (Note 5)                | For stable operation                                                                                 |      | 250  |       | 2000 | pF |

| t <sub>PD</sub>    | Propagation delay (Note 5)                                       | Delay from PWMIN to<br>PWMOUT pin, TAIL<br>connected to VDD                                          |      |      | 0.1   |      | μs |

| f <sub>PWM</sub>   | Internal PWM signal frequency                                    | External R <sub>FPWM</sub> = 30kΩ,<br>across PWMIN to GND                                            | •    | 180  | 200   | 220  | Hz |

| D <sub>PWM7</sub>  | - PWM duty cycle                                                 | $V_{TAIL}$ driven by resistor divider from VDD, $V_{TAIL}/V_{DD}$ = 0.093, $R_{FPWM}$ = 30k $\Omega$ |      | 6.3  | 7     | 7.7  | %  |

| D <sub>PWM90</sub> | P vvivi daty cycle                                               | $V_{TAIL}$ driven by resistor divider from VDD, $V_{TAIL}/V_{DD}$ = 0.612, $R_{FPWM}$ = 30k $\Omega$ |      | 87   | 90    | 93   | 70 |

| t <sub>DPWM</sub>  | Delay time between PWMIN rising edge to 20% of FB                | Delay time between PWM rising edge to 20% of FB                                                      |      |      | 23    |      | us |

| tsR                | Current slew time                                                | FB rising from 20% to 90% levels, for internal reference ramp                                        |      | 49   | 70    | 91   | μs |

| tsf                | Current slew time                                                | FB falling from 90% to 20% levels, for internal reference ramp                                       |      | 49   | 70    | 91   | μs |

| tsrms              | Rise time and fall time mismatch between four strings (Note 3,4) | Rise and fall time mismatch<br>between 20% and 90%<br>levels in all strings                          |      |      |       | 5    | %  |

# **ELECTRICAL CHARACTERISTICS (CONTINUE)**

Valid at V<sub>IN</sub>= 7V ~ 19V

"•" symbol indicates specifications across the full operating temperature range with  $T_A = T_J = -40$ °C to +125°C, other specifications are at  $T_A = T_J = 25$ °C; unless noted otherwise.

| Symbol             | Parameter Conditions                                                                |                                                                                             |   |      | Тур. | Max. | Unit |

|--------------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|---|------|------|------|------|

| Logic Pin          | as .                                                                                |                                                                                             |   | •    | •    | •    |      |

| VIL                | MODE, PWMIN, FAULTB pins input low voltage                                          | Below V <sub>IL</sub> level, input voltage considered as logic LOW                          | • |      |      | 0.8  | V    |

| VIH                | MODE, PWMIN, FAULTB pins input high voltage                                         | Above V <sub>IH</sub> level, input<br>voltage considered as logic<br>HIGH                   | • | 2    |      |      | V    |

| $V_{OL}$           | FAULTB, PWMOUT pins output low voltage                                              | I <sub>OL</sub> = 1mA                                                                       | • |      |      | 0.4  | V    |

| V <sub>OH</sub>    | PWMOUT pin output high voltage                                                      | I <sub>OH</sub> = -1mA                                                                      | • | 4    |      |      | V    |

| VILF               | PWMB pin input low voltage                                                          | Below V <sub>ILF</sub> level, input<br>voltage on PWMB pin will<br>disable PWM dimming mode | • | 0.85 |      | 1.15 | V    |

| VIHF               | PWMB pin input high voltage                                                         | Above V <sub>IHF</sub> level, input<br>voltage on PWMB pin will<br>enable PWM dimming mode  | • | 1.06 |      | 1.44 | V    |

| Protectio          | n                                                                                   |                                                                                             |   |      |      |      |      |

| $V_{INth(L)}$      | Input over voltage derates V <sub>FB</sub> by 10%                                   | V <sub>VTH</sub> = 2V                                                                       |   | 19.7 | 20.7 | 21.7 | V    |

| VINthd             | Input over voltage derating range (V <sub>IN_180mV</sub> to V <sub>IN_120mV</sub> ) | V <sub>REF</sub> drops from 180mV to 120mV                                                  |   |      | 2.16 |      | V    |

| Vscv               | V <sub>IN</sub> to drain short detect voltage                                       | Measured as (V <sub>IN</sub> - V <sub>DET</sub> )                                           | • | 0.5  | 0.8  | 1.1  | V    |

| Vocv               | Open LED fault detect voltage                                                       | Measured at DET,<br>V <sub>IN</sub> >V <sub>OCVEN</sub>                                     | • | 0.2  | 0.25 | 0.3  | V    |

| Vocven             | Open LED detect enable voltage                                                      | V <sub>VTH</sub> = 2V                                                                       |   |      | 10   |      | V    |

| V <sub>NTC10</sub> | NTC derates V <sub>FB</sub> by 10%                                                  |                                                                                             |   | 1.9  | 2.0  | 2.12 | V    |

| V <sub>NTC90</sub> | NTC derates V <sub>FB</sub> by 90%                                                  |                                                                                             |   |      | 0.43 |      | V    |

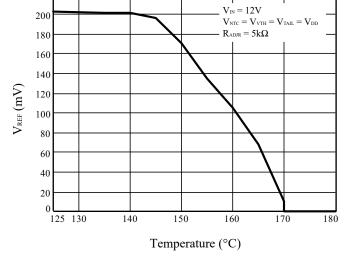

| Тлн                | Thermal rolloff activation temperature (Note 5)                                     | V <sub>FB</sub> derated by 10%                                                              |   |      | 148  |      | °C   |

| TJL                | Thermal rolloff low-current temperature (Note 5)                                    | V <sub>FB</sub> derated by 65%                                                              |   |      | 163  |      | °C   |

| $T_{SD}$           | Over temperature shutdown (Note 5)                                                  | Temperature increasing                                                                      |   |      | 170  |      | °C   |

| T <sub>SDHY</sub>  | Over temperature hysteresis (Note 5)                                                | Recovery= T <sub>SD</sub> -T <sub>SDHY</sub>                                                |   |      | 30   |      | °C   |

$<sup>\</sup>textbf{Note 2:} \ \text{Reference matching is defined as:} \ \left(V_{\text{FB(max)}} - V_{\text{FB(min)}}\right) / \ V_{\text{FB(AVG)}}. \ \text{Where} \ V_{\text{FB(AVG)}} \text{is the average of all } V_{\text{FB}}.$

Note 3: Rise Time to Fall Time Matching is defined as the maximum difference between the rise time and the fall time of the same string.

**Note 4:** Rise Time to Fall Time Mismatch between all strings is defined as the maximum ratio of the difference between either the rise time or the fall time to the average of the rise time or fall times between all strings.

Note 5: Guaranteed by design.

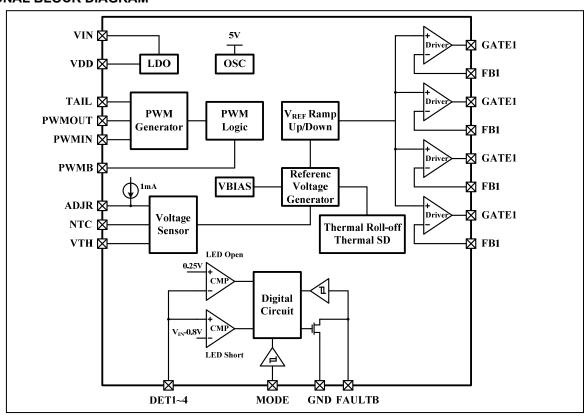

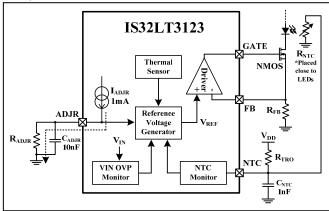

# **FUNCTIONAL BLOCK DIAGRAM**

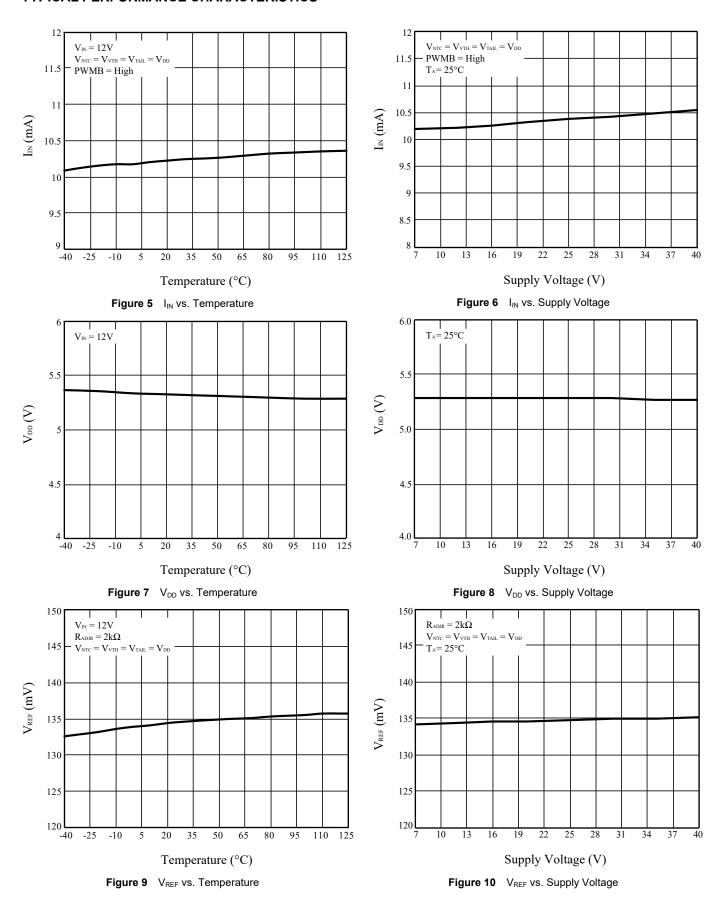

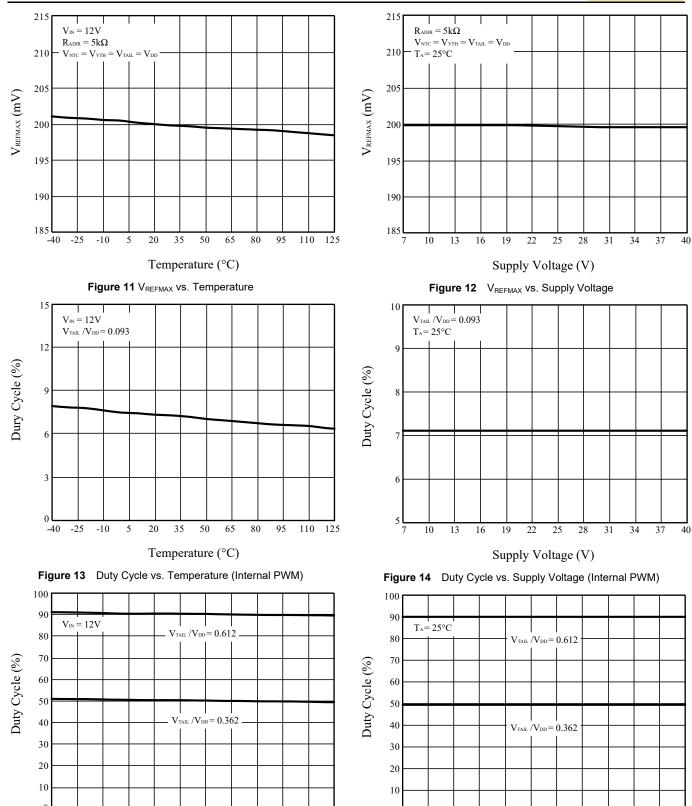

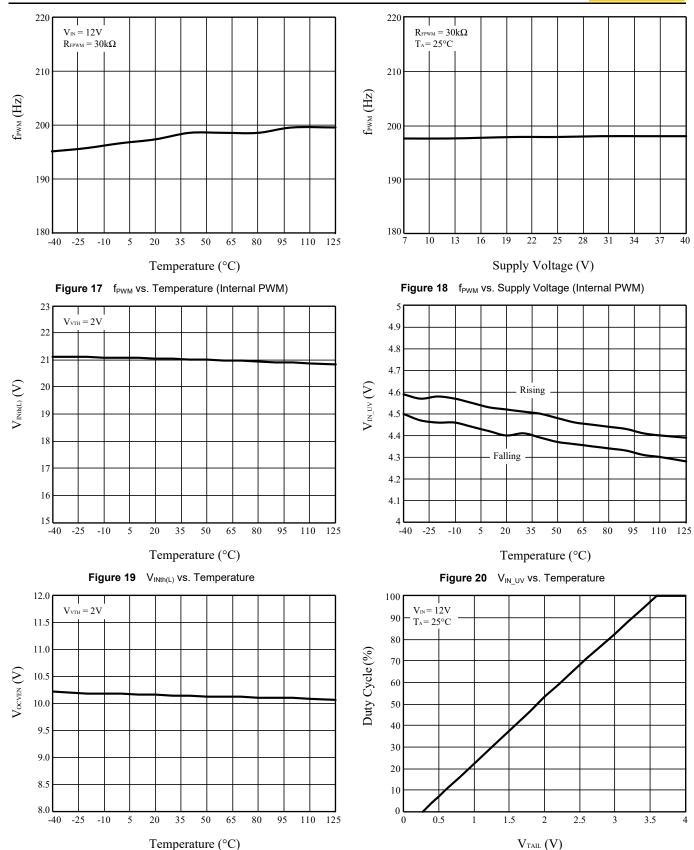

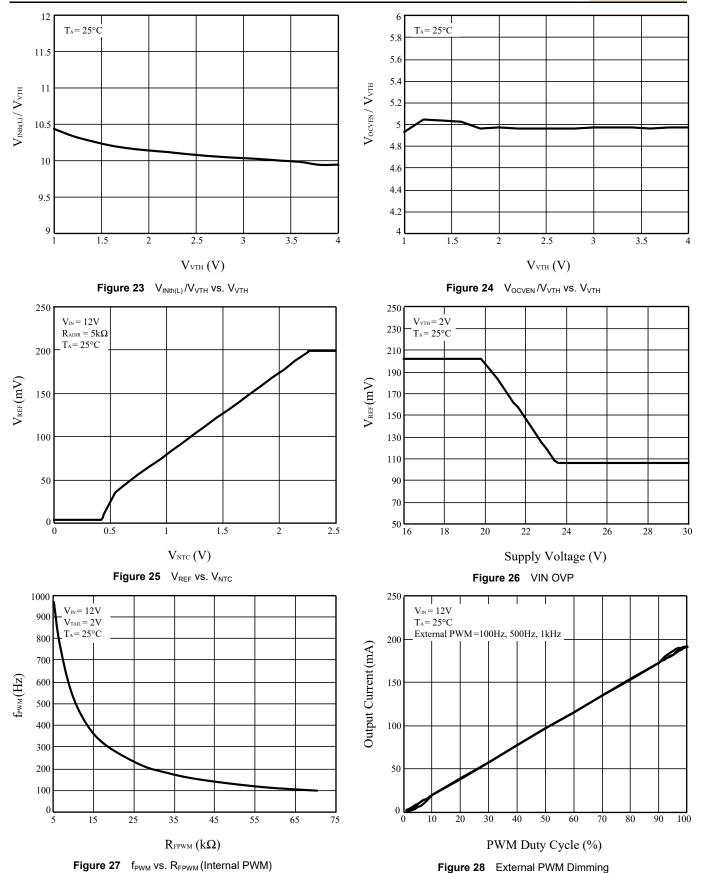

### TYPICAL PERFORMANCE CHARACTERISTICS

110 125

Figure 15 Duty Cycle vs. Temperature (Internal PWM)

Temperature (°C)

Figure 16 Duty Cycle vs. Supply Voltage (Internal PWM)

22 25 28 31

Supply Voltage (V)

10

13 16 19

-25 -10 5 20 35 50

34 37

Figure 21  $V_{\text{OCVEN}}$  vs. Temperature

Figure 22 Duty Cycle vs. V<sub>TAIL</sub> (Internal PWM)

220

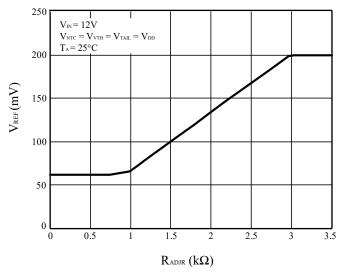

Figure 29  $V_{REF}$  vs.  $R_{ADJR}$

Figure 30 Thermal Rolloff

### **APPLICATION INFORMATION**

The IS32LT3123 is a programmable linear controller capable of regulating high constant current in four LED strings with external NMOS FETs. A dedicated pin (PWMB) is able to switch the output current between full brightness mode (high current) and PWM dimming mode (low current) by an external logic level. In the PWM dimming mode, the PWM dimming can be either the internal PWM generator, whose duty cycle and frequency are programmed by TAIL and PWMIN pins, or an external PWM signal fed on PWMIN pin. Mounting different value resistors on ADJR pin can fine tune the output peak current for binning purpose. With a NTC resistor divider placed close to LED strings, IS32LT3123 can monitor the temperature of the LED strings and realize current derating if the temperature exceeds the setting thermal threshold, which effectively prevents the LED strings from thermal runaway damage. A settable input over voltage detection is provided to sense the input voltage and reduce the output current if the input voltage exceeds the targeted threshold. IS32LT3123 also integrates fault detection and protection circuitry for the LED string open/short and over temperature fault conditions and reports fault conditions by a dedicated pin (FAULTB). In the case of fault conditions, the MODE pin can control the action to be either "one fail all fail" or "one fail all on". The FAULTB pins of multiple devices can be tied together for fault condition sharing to achieve simultaneous "one fail all fail".

#### **UNDER VOLTAGE LOCKOUT (UVLO)**

IS32LT3123 features an under voltage lockout (UVLO) function on the VIN pin to prevent misoperation at too low input voltages. UVLO threshold is an internally fixed value and cannot be adjusted. The device is enabled when the  $V_{\text{IN}}$  voltage exceeds  $V_{\text{IN\_UV}}$  (Typ. 4.5V), and disabled when the  $V_{\text{IN}}$  voltage falls below ( $V_{\text{IN}}$  uv- $V_{\text{IN}}$  uvHy) (Typ. 4.35V).

### LINEAR REGULATOR VDD

The device incorporates a linear regulator (VDD) output with a minimum 14mA current capability to power external circuitry. It requires a low ESR, X7R type ceramic capacitor from VDD pin to GND for proper operation; this capacitor must be placed as close to VDD pin as possible. To drive the external circuitry, the recommended capacitor value is 1µF.

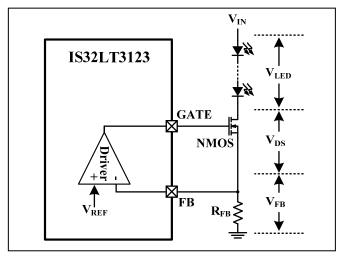

#### **OUTPUT CURRENT SETTING**

The IS32LT3123 provides 4 channels of low-side current drive via 4 external NMOS FETs. The negative feedback loops drive the GATEs of NMOS FETs to maintain the current feedback voltage of FB pins equal to the internal reference voltage, V<sub>REF</sub>. All channels share the same reference voltage source. So V<sub>REF</sub> decides the output current. The regulated maximum LED current of each NMOS FET is individually set by its corresponding feedback resistor (R<sub>FB</sub>). As Figure 31.

V<sub>REF</sub> can be controlled by ADJR resistor (R<sub>ADJR</sub>), NTC thermal rolloff protection, input over voltage protection and thermal rolloff protection actions. If R<sub>ADJR</sub>≥3kΩ and no protection actions, V<sub>REF</sub> is maximum value, V<sub>REFMAX</sub> (Typ. 0.2V). The feedback resistor value can be computed using the following:

$$R_{FB} = \frac{V_{REFMAX}}{I_{OUT \ FULL}} \tag{1}$$

Where  $I_{OUT\_FULL}$  is output current of full brightness mode (without PWM dimming) in Amp and R<sub>FB</sub> is in  $\Omega$ .

It is recommended that  $R_{\text{FB}}$  be a 1% accuracy resistor with good temperature characteristic to ensure stable and precise output current.

When the desired current is high, the power rating also should be considered. The maximum power dissipation on the  $R_{\text{FB}}$  resistor is calculated by:

$$P_{RFB} = V_{REFMAX} \times I_{OUT FULL} \quad (2)$$

A single high wattage resistor or several small wattage resistors in parallel can be used to sustain the power dissipation.

Figure 31 Constant Current Regulation

If any channel is unused, connect its FB pin to GND and leave its GATE pin floating. To avoid false protection triggering, its DET pin must be tied to one of the used channel's DET pin as Figure 32.

Figure 32 Unused Channel (CH1 Used and CH2 Unused)

### **CURRENT ADJUSTMENT BY ADJR**

The ADJR pin is a dedicated pin for output current fine tuning. Connecting a proper range value resistor, RADJR, from this pin to GND can adjust the output current, which can be used for LED binning or output power ranking purpose. As Figure 31, there is a precise constant current source, IADJR (Typ. 1mA), inside ADJR pin. When RADJR is connected, IADJR going through this resistor creates a voltage drop on AJDR pin which is detected by the internal Reference Voltage Generator circuit to generate the internal reference voltage, V<sub>REF</sub>, for output current regulation.

If  $R_{ADJR}$  value is greater than or equal to  $3k\Omega$ , the  $V_{REF}$ is clamped at maximum value, VREFMAX (typ. 0.2V). The output current will be the maximum setting value, I<sub>OUT</sub> FULL in Equation (1).

If R<sub>ADJR</sub> value is between  $1k\Omega$  and  $3k\Omega$ , the V<sub>REF</sub> is decided by:

$$V_{REF} = \left(\frac{R_{ADJR} \times 1mA}{3V}\right) \times 0.2V \quad (3)$$

So the output current can be adjusted by this resistor:

$$I_{OUT\_ADJR} = \frac{\left(\frac{R_{ADJR} \times 1mA}{3V}\right) \times 0.2V}{R_{FB}}$$

(4)

Where  $R_{ADJR}$  is in  $k\Omega$  and  $R_{FB}$  is in  $\Omega$ .

If the  $R_{ADJR}$  value is smaller than or equal to  $1k\Omega$ , the V<sub>REF</sub> is clamped at 0.067V (Typ.). Then the output current will be:

$$I_{OUT\_ADJR} = \frac{0.067V}{R_{FB}}$$

(5)

It is recommended that RADJR be a 1% accuracy resistor with good temperature characteristics to ensure stable and precise output current. RADJR could be placed on LED board and connected to ADJR pin via a long hardness. To prevent external EMI noise interference from the harness, a 10nF X7R type ceramic capacitor, CADJR, must be added and placed as close to ADJR pin as possible to prevent noise interference.

All above equations are apply only if there are no protection actions.

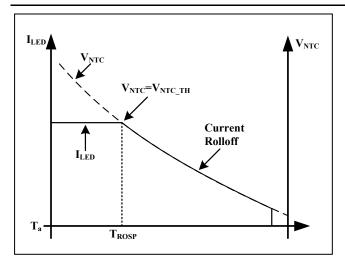

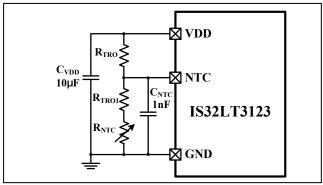

## LED THERMAL ROLLOFF PROTECTION BY NTC

IS32LT3123 is capable to implement LED over temperature current roll off protection in conjunction with an external NTC thermistor placed close to the LEDs. As Figure 31, NTC pin voltage, V<sub>NTC</sub>, is monitored and feedback to the Reference Voltage Generator circuits to adjust the internal reference voltage, V<sub>REF</sub>. V<sub>NTC</sub> will not affect V<sub>REF</sub> until dropping below NTC pin's voltage threshold, V<sub>NTC</sub> TH (typ. 2.2V).

If V<sub>NTC</sub>≥V<sub>NTC</sub> TH, the V<sub>REF</sub> is clamped at the value set by RADJR. Once VNTC VNTC TH, the internal reference voltage is decided by V<sub>NTC</sub>:

$$V_{REF\_NTC} = V_{REF} - \frac{2.2V - V_{NTC}}{10}$$

(6)

Where, VREF is set by RADJR value, as Equation (3) ~ (5). So the output current with NTC pin's adjustment will be:

$$I_{OUT\_NTC} = \frac{V_{REF\_NTC}}{R_{ER}}$$

(7)

In the application, a resistor divider containing a NTC thermistor (R<sub>NTC</sub>) derives a voltage on NTC pin from V<sub>DD</sub>. The NTC pin voltage is:

$$V_{NTC} = \frac{V_{DD} \times R_{NTC}}{R_{TRO} + R_{NTC}} \tag{8}$$

the negative temperature characteristic of the NTC thermistor, the V<sub>NTC</sub> gradually reduces following the temperature ramping up. The output current is constant until V<sub>NTC</sub>=V<sub>NTC</sub> <sub>TH</sub>. As shown in Figure 33, assume that the desired temperature point of current rolloff start is TROSP. With a given NTC thermistor, the NTC resistance (RNTC ROSP) at TROSP temperature point can be found in its datasheet. Put into Equation (8) to decide RTRO value:

$$R_{TRO} = \frac{V_{DD} \times R_{NTC\_ROSP}}{V_{NTC\_TH}} - R_{NTC\_ROSP} \quad (9)$$

Choose a 1% accuracy resistor with good temperature characteristics for R<sub>TRO</sub> to ensure stable and precise temperature threshold.

When the temperature ramps above T<sub>ROSP</sub>, V<sub>NTC</sub>'s reduction gradually derates the output current. The rolloff rate is decided by NTC's characteristics. The output current in rolloff range is:

$$I_{OUT\_TRO} = \frac{V_{REF} + 0.1 \times \frac{V_{DD} \times R_{NTC\_TRO}}{R_{TRO} + R_{NTC\_TRO}} - 0.22V}{R_{ER}}$$

(10)

Where, RNTC TRO is the NTC resistance at the temperature over TROSP which can be found in NTC's datasheet.

The R<sub>NTC</sub> thermistor has to be placed close to LEDs which may be connected to IS32LT3123 driver board via long PCB traces or hardness. To prevent external EMI noise interference from these traces/harness, a 1nF X7R type ceramic capacitor, C<sub>NTC</sub>, must be added and placed close to the NTC pin. If this LED protection is unused, connect the NTC pin to the VDD pin via a  $10k\Omega$  resistor.

Figure 33 LED Thermal Rolloff Protection

If the current rolloff slew rate is too steep for the application, adding an optional resistor,  $R_{TRO1}$ , in series with  $R_{NTC}$  can slow down the slew rate as Figure 34.

Figure 34 R<sub>TRO1</sub> Slows Down Slew Rate

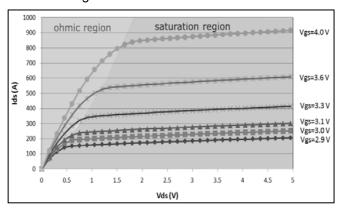

#### **EXTERNAL NMOS FET**

The IS32LT3123 uses the NMOS FETs as constant current sources operating in the "linear mode" as shown in the current saturation region in the output characteristic graph. As shown in the graph, the drain current ( $l_{DS}$ ) is independent of the drain to source voltage ( $V_{DS}$ ) it depends on the  $V_{GS}$  gate voltage of the NMOS FET. Therefore, since the NMOS FET is used as a constant current source, the current flow through the LED string is controlled by the  $V_{GS}$  voltage at the NMOS FET gate.

Figure 35 NMOS FET Operating Mode

The NMOS FET must be chosen with its drain voltage rating greater than the Transient Voltage Suppressor (TVS) clamp voltage of the load dump protection. And its current rating should be greater than the desired maximum current. To ensure constant current regulation, the voltage drop on drain to source (VDS) of NMOS FET must be larger than its saturation voltage of desired current level, VDS\_SAT, which can be found from the "IDS VS. VDS" output characteristic graph in NMOS FET datasheet. Basically, larger current rating NMOS FET gets lower saturating voltage at same current level. As Figure 36. The minimum VIN voltage is decided by:

$$V_{IN MIN} = V_{LED} + V_{DS SAT} + V_{FB}$$

(11)

Where V<sub>LED</sub> is the LED string forward voltage.

So the larger  $V_{\text{DS\_SAT}}$  will slightly affect the minimum VIN voltage.

All NMOS FET datasheets include a Safe Operating Area (SOA) diagram to be used as a tool to show the limits where the NMOS FET can be safely operated in linear mode. The SOA diagram is only valid for a given condition, different conditions require derating calculations.

In addition, because the NMOS FET doesn't have an over temperature protection mechanism, the power rating of the NMOS FET should be carefully considered to sustain the maximum power dissipation on it. When the LED string forward voltage is fixed, a higher input supply voltage will result in a larger  $V_{DS}$  voltage which results in more power dissipation on NMOS FET. Because the NMOS FET is operated in linear mode, the  $R_{DS(on)}$  value of the MOSFET is not used when calculating power dissipation. The power dissipation in the NMOS FET depends only on the voltage drop  $V_{DS}$  and the current flow:  $P_{NMOS} = V_{DS} \times I_{DS}$ . So the maximum power dissipation at full brightness mode can be calculated by:

$$P_{NMOS\_MAX} = (V_{IN\_MAX} - V_{LED\_MIN} - V_{FB}) \times I_{OUT\_FULL}$$

(12)

Where  $V_{\text{IN\_MAX}}$  is the maximum input voltage in the application and  $V_{\text{LED\_MIN}}$  is the LED string minimum forward voltage.

Figure 36 Voltage Drop

After calculating the maximum power dissipation, the junction temperature increase of the NMOS FET can be estimated. Make sure the junction temperature in worst case should not exceed the maximum operating junction temperature of the NMOS FET.

$$(P_{NMOS\_MAX} \times R_{\theta JA\_NMOS} + T_{A\_MAX}) < T_{J(MAX)\_NMOS}$$

(13)

Where, T<sub>J(MAX) NMOS</sub> is the maximum operating junction temperature limit of the NMOS FET. Reja NMOS is the junction to ambient thermal resistance of the NMOS FET. TA\_MAX is the highest operating ambient temperature of the system.

A NMOS FET with a big thermal PAD and low thermal resistance is preferred, such as a SOT-223 or D-PAK package. When designing the Printed Circuit Board (PCB) layout, a double-sided PCB with a large copper area on each side of the board directly under these NMOS FETs must be used. Multiple thermal vias under the exposed pad will help conduct heat from the pad of NMOS FET to the copper on each side of the board. The thermal resistance can be further be reduced by using a metal substrate or by adding a heat sink. To avoid heat buildup, these power components should be spread out on the PCB board with some distance.

# **PWM DIMMING**

IS32LT3123 supports two modes: full brightness mode and PWM dimming mode. When PWMB pin is pulled low, the IS32LT3123 will enable PWM dimming mode, which supports both internal and external PWM dimming modes. If PWMB pin is pulled high, the PWM dimming signal will be overridden to get full brightness mode (100% duty cycle) and its output current is as Equation (1)/(4)/(5). Note that both PWM dimming modes will simultaneously dim all output channels.

### INTERNAL PWM DIMMING MODE

When the TAIL pin is connected to a voltage below 3.7V (typ.), the IS32LT3123 will be in internal PWM dimming mode. As in Figure 1. The integrated PWM

generator is enabled and the voltage on TAIL pin determines the PWM duty cycle. The PWM duty cycle can be calculated as follows:

$$D_{PWM} = 160 \times \frac{V_{TAIL}}{V_{DD}} - 7.9 \quad (14)$$

Where, D<sub>PWM</sub> is PWM duty cycle in %. V<sub>DD</sub> and V<sub>TAIL</sub> are in Volts.

To get better accuracy, recommend to derive V<sub>TAIL</sub> by a precise resistor divider from VDD (as RTAIL1 and RTAIL2 in Figure 1, 1% accuracy resistor is recommended to be used) and the recommended duty cycle setting range is 5%~95%. The lower duty cycle results in lower output current accuracy. A 1nF X7R type ceramic capacitor, C<sub>TAIL</sub>, should be added and placed close to TAIL pin for noise decoupling. The output current is modulated by the PWM duty cycle:

$$I_{OUT\_PWM} = I_{OUT\_FULL} \times D_{PWM} \quad (15)$$

If  $R_{ADJR}$ <3 $K\Omega$ , the output current will be:

$$I_{OUT\ PWM} = I_{OUT\ ADJR} \times D_{PWM} \quad (16)$$

When the duty cycle is set by the TAIL pin, the PWM frequency is programmed by a single resistor, R<sub>FPWM</sub>, connected from PWMIN pin to GND. The PWM frequency can be set in a range of 100Hz~1kHz. Since the output current has slew rate control for EMI consideration, the lower PWM frequency will get better output accuracy. The resistor value can be calculated as follows:

$$R_{FPWM} = \frac{5380}{f_{PWM} - 20.7} \tag{17}$$

Where, f<sub>PWM</sub> is desired PWM frequency in Hz and Repwi is in  $k\Omega$ .

An external voltage on the TAIL pin instead of the resistor divider can be used for analog input PWM dimming. As in Figure 3. The PWM duty cycle and frequency are identical as Equation (14) and (17). A 1nF X7R type ceramic capacitor, C<sub>TAIL</sub>, must be added and placed close to TAIL pin for noise decoupling.

### **EXTERNAL PWM DIMMING MODE**

When the TAIL pin is tied to  $V_{DD}$  directly, the IS32LT3123 will be in external PWM dimming mode. As in Figure 2. The integrated PWM generator is disabled. An external PWM signal on PWMIN pin can modulate the output current based on the duty cycle. The recommended frequency range of the external PWM signal is 100Hz~1kHz and the duty cycle can be from 0 to 100%. Since the output current has slew rate control for EMI consideration, a lower frequency PWM will get better dimming contrast ratio. The calculation of output current is identical as Equation (15) and (16). Note that the PWMIN pin is high impedance input in

external PWM dimming mode.

#### PWM DIMMING SYNCHRONIZATION

When PWMB pin is pulled low (PWM dimming mode), the PWMOUT pin is able to output a PWM signal to drive other slave devices for PWM dimming synchronization. When the device is configured as internal PWM dimming mode (PWMB pin pulled low and  $V_{TAIL}$ <3.7V), the output of the PWMOUT pin is the internal PWM generator. When the device is configured as external PWM dimming mode (PWMB pin pulled low and TAIL pin tied to VDD), the output of the PWMOUT pin is synchronized with the signal on PWMIN pin. For lighting systems with multiple IS32LT3123 controllers, one controller can be configured as internal PWM dimming mode to be a master and output a PWM signal. Other controllers can be configured as external PWM dimming mode to be slaves. Connect all PWMIN pins of the slaves to the PWMOUT pin of the master to implement PWM dimming synchronization. As in Figure 4. If the PWMOUT pin is unused, leave it floating.

#### **FAULT PROTECTION AND REPORTING**

For robust system reliability, the IS32LT3123 integrates the detection circuitry to protect various fault conditions and report the fault conditions on the FAULTB pin which can be monitored by an external host. The fault protections include LED string open/short, VIN over voltage, controller junction thermal rolloff. LED thermal rolloff and thermal shutdown. Refer to Table 1. The FAULTB pin is open drain structure with both input and output function. The FAULTB pin is not allowed to float. An external resistor, RFAULTB, must be added to pull up FAULTB pin above 2V for normal operation. The recommended resistor value is 47kΩ. The FAULTB pin will go low when the device enables fault detection and detects a fault condition.

As an input pin (MODE pin high), externally pulling FAULTB pin low will disable the output. For lighting systems with multiple IS32LT3123 controllers which require the complete lighting system be shut down when a fault is detected, the FAULTB pin can be used in a parallel connection as shown in Figure 4. A fault output by one device will pull low the FAULTB pins of other parallel connected devices simultaneously turn them off. This satisfies the "one fail all fail" operating requirement.

### VIN OVER VOLTAGE CURRENT DERATING **PROTECTION**

According to Equation (12), the input voltage will significantly affect the power dissipation on the NMOS FET. With given LED strings and output current, the higher input voltage the large power dissipation on NMOS FET. In automotive applications, the nominal battery voltage range is about 9V to 16V. However. electrical and radio-frequency disturbance frequently

occur in vehicle environment that results in the supply voltage jumping over 16V. Such as load dump case, it could raise up the supply voltage over 40V. Since the NMOS FET doesn't have over temperature protection mechanism, the IS32LT3123 integrates a power supply over voltage current derating protection to avoid thermal runaway on the NMOS FET.

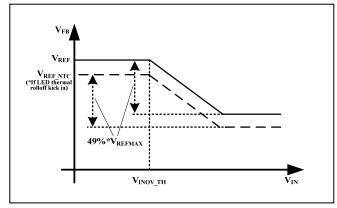

As Figure 31, the VIN voltage is monitored and fedback to the Reference Voltage Generator circuit to adjust the internal reference voltage, V<sub>REF</sub>, thereby the output current is changed accordingly. In case the VIN voltage exceeds a setting over voltage threshold, the device will start to gradually reduce the internal reference voltage (VREF) down by 49%\*VREFMAX, following the increasing  $V_{\text{IN}}$ . The VIN over voltage threshold, V<sub>INOV\_TH</sub>, is set by an external resistor divider (R<sub>TH1</sub> and R<sub>TH2</sub>) from VIN pin connected to VTH pin:

$$V_{INOV\_TH} = 10 \times V_{VTH} = 10 \times \frac{V_{DD} \times R_{TH2}}{R_{TH1} + R_{TH2}}$$

(18)

Where, V<sub>VTH</sub> is VTH pin voltage. Choose proper R<sub>TH1</sub> and R<sub>TH2</sub> to make sure V<sub>VTH</sub> is within 1V to 4V. R<sub>TH1</sub> and R<sub>TH2</sub> must be 1% accuracy resistor with good temperature characteristics to ensure stable and precise voltage threshold.

When VIN>VINOV TH before VREF being reduced by 49%\*V<sub>REFMAX</sub>, the internal reference voltage is decided

$$V_{REF\_OV} = V_{REF} - 0.0286 \times (V_{IN} - V_{INOV\_TH})$$

(19)

$$I_{OUT\_OV} = \frac{V_{REF\_OV}}{R_{FB}} \qquad (20)$$

Where, VREF is set by RADJR value, as Equation (3) and (5). Assume  $V_{VTH}=2V$ , the  $V_{REF}$  will drop down by 49%\*VREFMAX at around VIN=23.4V and stay at this level for higher VIN voltage.

If the NTC thermistor LED thermal rolloff also kicks in, the internal reference voltage would be:

$$V_{REF\_OV} = V_{REF\_NTC} - 0.0286 \times (V_{IN} - V_{INOV\_TH})$$

(21)

Figure 37 V<sub>IN</sub> Over Voltage Protection

VIN over voltage protection won't be reported via FAULTB pin.

#### LED STRING OPEN PROTECTION

The LED string open detection is enabled after VIN voltage rising above a setting threshold,  $V_{\text{INOC\_TH}}$ , which is to prevent insufficient  $V_{\text{IN}}$  falsely triggering LED string open detection. The threshold is programmed by the external resistor divider ( $R_{\text{TH1}}$  and  $R_{\text{TH2}}$ ) from VIN pin connected to VTH pin as well:

$$V_{INOC\_TH} = 5 \times V_{VTH} = 5 \times \frac{V_{DD} \times R_{TH2}}{R_{TH1} + R_{TH2}}$$

(22)

If any LED string is open, the corresponding DET pin connected to NMOS FET's drain is pulled down by NMOS FET. If V<sub>IN</sub>>V<sub>INOC</sub> TH and the DET pin voltage drops below the open LED detect voltage, Vocv, the LED string open protection will be triggered and FAULTB pin will go low to report the fault condition. The MODE pin decides the fault protection mode. If the MODE pin is high, the fault protection mode is "one fail all fail". So that the GATE pins of all normal channels will go low to turn off all LED strings. The GATE pin of the faulty channel will remain high for recovery detection, but the corresponding LED string will be off due to LED open. If the MODE pin is low, the fault protection mode is "one fail all on" which means that all normal channels will keep normal operation, however the LED string of the faulty channel will be off due to LED open. No matter in which fault mode, the device will recover to normal operation and FAULTB pin will go back to high impedance once the open condition is removed.

# LED STRING SHORT PROTECTION

The LED string short condition is detected if the voltage across VIN pin to any one of DET pins is lower

than short detect voltage, V<sub>SCV</sub>. Once short condition occurs, the FAULTB pin will go low to report the fault condition. If the MODE pin is high, the fault protection mode is "one fail all fail". So that the GATE pins of all normal channels will go low to turn off all LED strings. The GATE pin of the faulty channel will remain high for recovery detection, but the corresponding LED string will be off due to LED open. If the MODE pin is low, the fault protection mode is "one fail all on" which means that all normal channels will keep normal operation, however the LED string of the faulty channel will be off due to LED short. No matter in which fault mode, the device will recover to normal operation and FAULTB pin will go back to high impedance once the short condition is removed.

#### **CONTROLLER JUNCTION THERMAL ROLLOFF**

This feature is to protection the controller itself. The output current will be equal to the set value as long as the junction temperature of the controller remains below 145°C (typ.). If the junction temperature exceeds this threshold, the  $V_{\text{REF}}$  of the controller will begin to reduce toward zero at a rate of about -7.34mV/°C following the temperature ramping up. controller thermal rolloff protection won't be reported via FAULTB pin.

### **CONTROLLER THERMAL SHUTDOWN**

In the event that the junction temperature exceeds 170°C, the output channels will go to the 'OFF' state and FAULTB pin will pull low to report the fault condition. At this point, the IC presumably begins to cool off. Any attempt to toggle the channel back to the source condition before the IC cooled to <140°C will be blocked and the IC will not be allowed to restart, and FAULTB pin will recover to high impedance.

**Table 1 Fault Condition**

| Protection                       |                                                                                        |               | MODE=V <sub>DD</sub> (one fail all fail)                                                                                                          |                                                                           |                  | il)                                    |        | MODE=GND (one                                                                                     | fail all or      | 1)                                     |

|----------------------------------|----------------------------------------------------------------------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|------------------|----------------------------------------|--------|---------------------------------------------------------------------------------------------------|------------------|----------------------------------------|

| Type Detect Condition            |                                                                                        | FAULTB        | PWMOUT                                                                                                                                            | Faulty String                                                             | Other<br>Strings | Recover                                | PWMOUT | Faulty String                                                                                     | Other<br>Strings | Recover                                |

| Short<br>LED                     | (V <sub>IN</sub> -V <sub>DETx</sub> ) <v<sub>SCV</v<sub>                               | Pulled<br>low | Pulled<br>low                                                                                                                                     | Keep on with<br>100% duty<br>cycle<br>irrespective of<br>any PWM<br>mode. | Turn<br>off      | Fault<br>condition<br>removed          | Normal | The LEDs will be off due to shorted, however the current in the NMOS FET will be normal.          | Normal           | Fault<br>condition<br>removed          |

|                                  |                                                                                        |               | This fault is detected after all GATEx high and completion of reference ramp. When detected, the fault remains active independent of GATE status. |                                                                           |                  |                                        |        |                                                                                                   |                  |                                        |

| Open<br>LED                      | $V_{\text{IN}} > V_{\text{INOC\_TH}} \text{ and } \\ V_{\text{DETx}} < V_{\text{OCV}}$ | Pulled<br>low | Pulled<br>low                                                                                                                                     | Keep on with<br>100% duty<br>cycle<br>irrespective of<br>any PWM<br>mode. | Turn<br>off      | Fault<br>condition<br>removed          | Normal | The LEDs will be<br>off due to open,<br>however the<br>corresponding<br>GATE pin will be<br>high. | Normal           | Fault<br>condition<br>removed          |

| Controller<br>Thermal<br>Rolloff | T <sub>J</sub> exceeds<br>145°C                                                        | Normal        | Normal                                                                                                                                            | All string current<br>derates based of<br>junction temper                 | on               | T <sub>J</sub> drops<br>below<br>145°C | Normal | All string current derates based on junction temperature.                                         |                  | T <sub>J</sub> drops<br>below<br>145°C |

| V <sub>IN</sub> Over<br>Voltage     | $V_{\text{IN}} > V_{\text{INOV\_TH}}$  | Normal        | Normal        | All string current derates based on supply voltage.  | V <sub>IN</sub> ≤V <sub>INOV_TH</sub>  | Normal | All string current derates based on supply voltage.  | V <sub>IN</sub> ≤V <sub>INOV_TH</sub>  |

|-------------------------------------|----------------------------------------|---------------|---------------|------------------------------------------------------|----------------------------------------|--------|------------------------------------------------------|----------------------------------------|

| Thermal<br>Shutdown                 | T <sub>J</sub> exceeds<br>170°C        | Pulled<br>low | Pulled<br>low | All string turn off                                  | T <sub>J</sub> drops<br>below<br>140°C | Normal | All string turn off                                  | T <sub>J</sub> drops<br>below<br>140°C |

| LED<br>String<br>Thermal<br>Rolloff | V <sub>NTC</sub> <v<sub>NTC_TH</v<sub> | Normal        | Normal        | All string current derates based on NTC pin voltage. | V <sub>NTC</sub> ≥V <sub>NTC_TH</sub>  | Normal | All string current derates based on NTC pin voltage. | V <sub>NTC</sub> ≥V <sub>NTC_TH</sub>  |

#### **CONTROLLER THERMAL CONSIDERATIONS**

The package thermal resistance,  $\theta_{JA}$ , determines the amount of heat that can pass from the silicon die to the surrounding ambient environment. The  $\theta_{JA}$  is a measure of the temperature rise created by power dissipation and is usually measured in degree Celsius per watt (°C/W). The junction temperature,  $T_{J}$ , can be calculated by the rise of the silicon temperature,  $\Delta T$ , the power dissipation,  $P_{D}$ , and the package thermal resistance,  $\theta_{JA}$ , as in Equation (23):

$$P_D = V_{IN} \times I_{IN} \tag{23}$$

and,

$$T_{I} = T_{A} + \Delta T = T_{A} + P_{D} \times \theta_{JA}$$

(24)

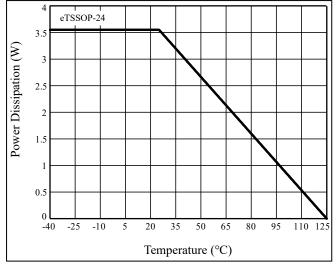

When operating the chip at high ambient temperatures, or when the supply voltage is high, care must be taken to avoid exceeding the package power dissipation limits. The maximum power dissipation can be calculated using the following Equation (25):

$$P_{D(MAX)} = \frac{125^{\circ}C - 25^{\circ}C}{\theta_{D}}$$

(25)

So,

$$P_{D(MAX)} = \frac{125^{\circ}C - 25^{\circ}C}{28.1^{\circ}C/W} \approx 3.56W$$

(26)

for eTSSOP-24 package.

Figure 38, shows the power derating of the IS32LT3123 on a JEDEC boards (in accordance with JESD 51-5 and JESD 51-7) standing in still air.

Figure 38 Dissipation Curve (eTSSOP-24)

When designing the Printed Circuit Board (PCB) layout, double-sided PCB with a large copper area on each side of the board directly under the IS32LT3123. Multiple thermal vias, as shown in Figure 39, will help to conduct heat from the exposed pad of the IS32LT3123 to the copper on each side of the board.

Figure 39 Board Via Layout For Thermal Dissipation

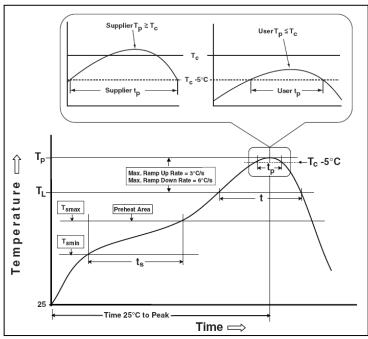

# **CLASSIFICATION REFLOW PROFILES**

| Profile Feature                                                                           | Pb-Free Assembly                 |

|-------------------------------------------------------------------------------------------|----------------------------------|

| Preheat & Soak Temperature min (Tsmin) Temperature max (Tsmax) Time (Tsmin to Tsmax) (ts) | 150°C<br>200°C<br>60-120 seconds |

| Average ramp-up rate (Tsmax to Tp)                                                        | 3°C/second max.                  |

| Liquidous temperature (TL) Time at liquidous (tL)                                         | 217°C<br>60-150 seconds          |

| Peak package body temperature (Tp)*                                                       | Max 260°C                        |

| Time (tp)** within 5°C of the specified classification temperature (Tc)                   | Max 30 seconds                   |

| Average ramp-down rate (Tp to Tsmax)                                                      | 6°C/second max.                  |

| Time 25°C to peak temperature                                                             | 8 minutes max.                   |

Figure 40 Classification Profile

# **PACKAGE INFORMATION**

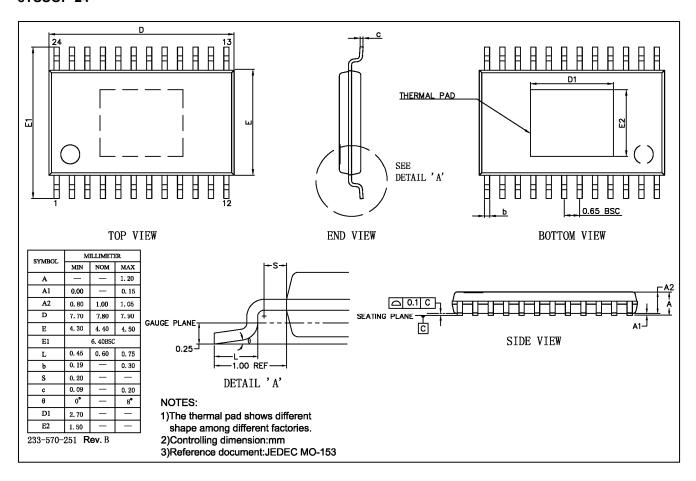

### eTSSOP-24

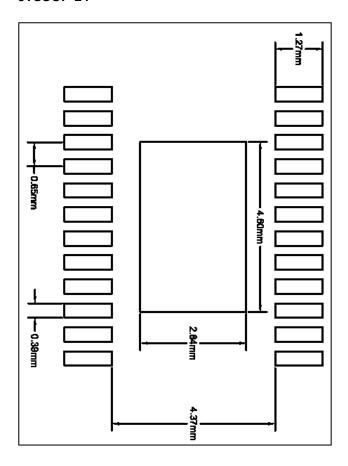

# **RECOMMENDED LAND PATTERN**

# eTSSOP-24

#### Note:

- 1. Land pattern complies to IPC-7351.

- 2. All dimensions in MM.

- 3. This document (including dimensions, notes & specs) is a recommendation based on typical circuit board manufacturing parameters. Since land pattern design depends on many factors unknown (eg. user's board manufacturing specs), user must determine suitability for use.

# **REVISION HISTORY**

| Revision | Detail Information                                                                   | Date       |

|----------|--------------------------------------------------------------------------------------|------------|

| 0C       | Initial release.                                                                     | 2020.03.19 |

| А        | Update EC table     Remove Tube packing                                              | 2020.05.06 |

| В        | 1.Update to new Lumissil logo     2.Add RoHS and update AECQ information in Features | 2024.04.23 |