# QOCVO

## **BENEFITS and FEATURES**

- Wide input voltage range

- Vin = 2.7V to 5.5V

- Complete integrated power solution

- 4A DC/DC Step-Down (Buck) Regulator with Bypass Function

- 4A DC/DC Step-Down (Buck) Regulator

- 2A DC/DC Step-Down (Buck) Regulator

- Two 390mA LDOs

#### • Space Savings

- Fully integrated

- High Fsw = 1.125MHz to 3.3MHz

- Works with 0.47µH Inductor

- Integrated sequencing

- Easy system level design

- Configurable Sequencing

- Multiple Wake up Triggers with GPIOs

- Seamless Sequencing of External Supplies

- Four Programmable GPIOs

- Buck 1 Bypass Mode for 3.3V system level compliance

- Highly configurable

- uP interface for status reporting and controllability

- Programmable Reset and Power Good GPIO's

- Flexible Sequencing Options

- Multiple Sleep Modes

- I<sup>2</sup>C Interface 1MHz

## **APPLICATIONS**

- Solid-State Drives (SSD)

- FPGA

- Computer Vision

- Portable Audio / Video

## **ACT88321** Advanced PMIC with 3 Bucks, 2 LDOs, and Load Bypass Switches

## **GENERAL DESCRIPTION**

The ACT88321 PMIC is an integrated ActiveCiPS<sup>™</sup> power management integrated circuit. It powers a wide range of processors, including solid-state drive applications, video processors, FPGA's, wearables, peripherals, and microcontrollers. The ACT88321 is optimized for SSD and FPGA applications. A similar product, ACT88328, is optimized for video and wearables applications. The ACT88321 is highly flexible and can be reconfigured via I<sup>2</sup>C for multiple applications without the need for PCB changes. The low external component count and high configurability significantly speeds time to market. Examples of configurable options include output voltage, startup time, slew rate, system level sequencing, switching frequency, sleep modes, operating modes etc. ACT88321 is programmed at the factory with a default configuration. These settings can be optimized for a specific design through the I<sup>2</sup>C interface. The ACT88321 is available in several default configuration. Contact the factory for specific default configurations.

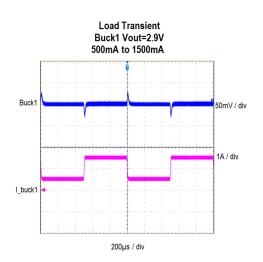

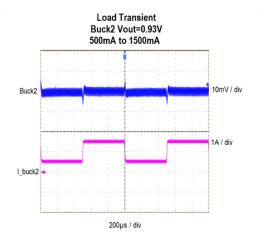

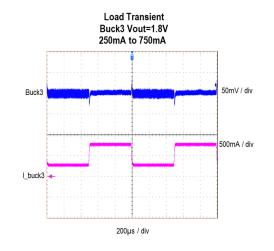

The core of the device includes three DC/DC step down converters using integrated power FETs, two low-dropout regulators (LDOs). Buck1 and LDO1 can be configured as a load switch. Buck1 is a peak current mode, fixed frequency DC-DC step down converter that is optimized for output voltage closes to the input voltage. Buck1 switches at either 1.125MHz or 2.25MHz, requiring only three small components for operation. Buck2 and Buck3 use an asynchronous constant on-time, ACOT, control architecture to optimize the load transient response with smaller output capacitors. The LDOs only require small ceramic capacitors. All outputs are highly configurable via the I<sup>2</sup>C interface.

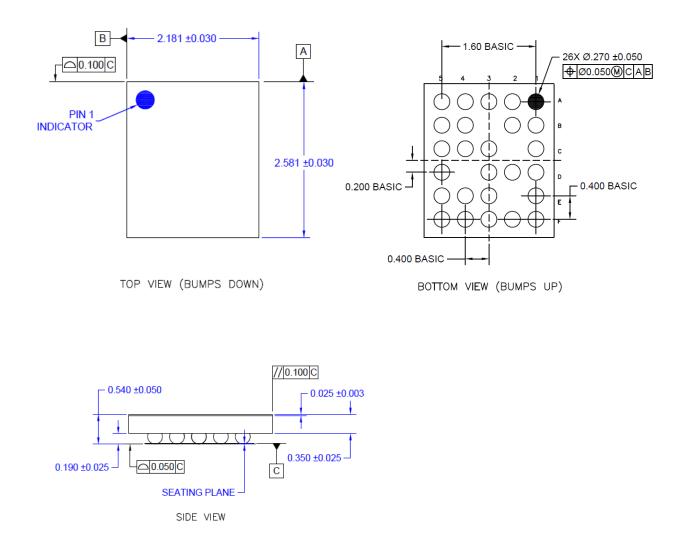

The ACT88321 PMIC is available in a 2.18 x 2.58 mm 30 ball WLCSP package.

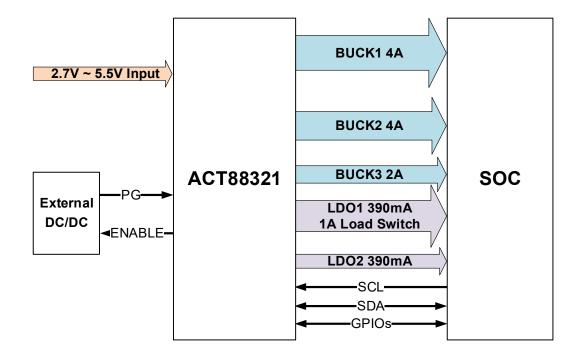

## **TYPICAL APPLICATION DIAGRAM**

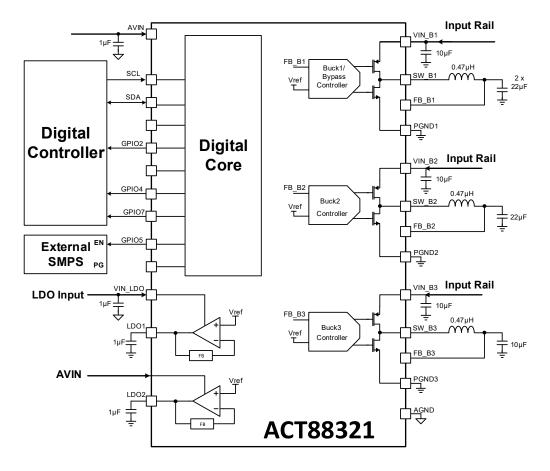

## FUNCTIONAL BLOCK DIAGRAM

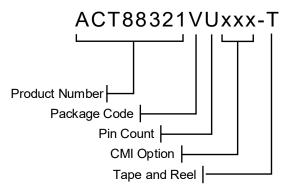

#### **ORDERING INFORMATION**

| PART NUMBER     | VIN  | Vout1     | V <sub>OUT2</sub> | Vоитз    | VLD01 | VLDO2 | 7-bit l <sup>2</sup> C<br>Address | Package      |

|-----------------|------|-----------|-------------------|----------|-------|-------|-----------------------------------|--------------|

| ACT88321VU101-T | 3.3V | 2.9V      | 0.93V             | 1.8V     | LSW   | 1.8V  | 0x25h                             | 30 pin WLCSP |

| ACT88321VU103-T | 3.3V | 2.5V      | 1.2V              | 1.8/1.2V | 1.8V  | 1.8V  | 0x25h                             | 30 pin WLCSP |

| ACT88321VU104-T | 3.3V | 3.0V/2.5V | 0.8V              | 1.2V     | 1.2V  | 1.8V  | 0x25h                             | 30 pin WLCSP |

| ACT88321VU105-T | 3.3V | 2.9V/2.5V | 0.81/0.70V        | 1.2/1.8V | PLSW  | 1.8V  | 0x25h                             | 30 pin WLCSP |

| ACT88321VU106-T | 3.3V | 2.5V      | 0.81/0.71V        | 1.2V     | PLSW  | 1.8V  | 0x25h                             | 30 pin WLCSP |

| ACT88321VU107-T | 3.3V | 2.5V      | 1.15/0.90V        | 1.2/1.8V | PLSW  | 1.8V  | 0x25h                             | 30 pin WLCSP |

| ACT88321VU110-T | 3.3V | 2.6V      | 0.96V             | 1.2V     | PLSW  | 1.8V  | 0x25h                             | 30 pin WLCSP |

| ACT88321VU112-T | 5V   | 3.3V      | 1.2V              | 1.8V     | 3.3V  | 2.5V  | 0x25h                             | 30 pin WLCSP |

Note 1: Standard product options are identified in this table. Contact factory for custom options, minimum order quantity required.

Note 3: Package Code designator. "V" represents CSP.

Note 4: Pin Count designator. "U" represents 30 pins.

Note 5: "xxx" represents the CMI (Code Matrix Index) option The CMI identifies the IC's default register settings.

Note 6: Preliminary. Contact Qorvo for details

## QOUNO

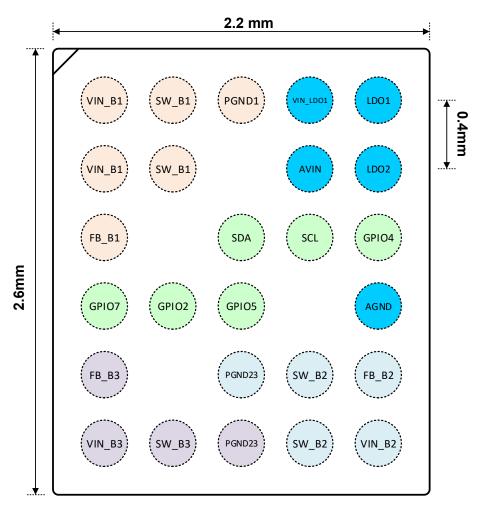

## PIN CONFIGURATION – WLCSP

|   | 1      | 2     | 3      | 4        | 5      |

|---|--------|-------|--------|----------|--------|

| A | VIN_B1 | SW_B1 | PGND1  | VIN_LDO1 | LDO1   |

| В | VIN_B1 | SW_B1 |        | AVIN     | LDO2   |

| С | FB_B1  |       | SDA    | SCL      | GPIO4  |

| D | GPIO7  | GPIO2 | GPIO5  |          | AGND   |

| E | FB_B3  |       | PGND23 | SW_B2    | FB_B2  |

| F | VIN_B3 | SW_B3 | PGND23 | SW_B2    | VIN_B2 |

Figure 1: Pin Configuration – Top View (bumps down) – WLCSP- 30

## QOUAD

#### **PIN DESCRIPTIONS**

| Ball (CSP) | NAME    | DESCRIPTION                                                                                                                                                 |

|------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A3         | PGND1   | Dedicated Power Ground for Buck1 Regulator.                                                                                                                 |

| B3         | n/a     | B3 is unused and does not have a package bump that can be soldered to the PCB                                                                               |

| E3, F3     | PGND23  | Dedicated Power Ground for Buck2 and Buck3 Regulators                                                                                                       |

| E4, F4     | SW_B2   | Switch Pin for Buck2 Regulator.                                                                                                                             |

| F5         | VIN_B2  | Dedicated VIN power input for Buck 2 Regulator.                                                                                                             |

| E5         | FB_B2   | Feedback for Buck2 Regulator. Connect to the Buck2 output capacitor.                                                                                        |

| A5         | LDO1    | Output for LDO1 Regulator (Leave unconnected if LDO1 is not used and disabled).                                                                             |

| A4         | VIN_LDO | Dedicated VIN power input for LDO1 Regulator.                                                                                                               |

| C4         | SCL     | I <sup>2</sup> C Clock Input.                                                                                                                               |

| C3         | SDA     | I <sup>2</sup> C Data Input and Output.                                                                                                                     |

| D5         | AGND    | Analog Ground. Kelvin connect to the other ground pins on the IC.                                                                                           |

| B5         | LDO2    | Output for LDO2 Regulator (Leave unconnected if LDO2 is not used and disabled).                                                                             |

| E1         | FB_B3   | Feedback for Buck3 Regulator. Connect to the Buck3 output capacitor.                                                                                        |

| F1         | VIN_B3  | Dedicated VIN power input for Buck3 Regulator.                                                                                                              |

| F2         | SW_B3   | Switch Pin for Buck3 Regulator.                                                                                                                             |

| E2         | n/a     | E2 is unused and does not have a package bump that can be soldered to the PCB                                                                               |

| D2         | GPIO2   | Configurable general-purpose input/open drain output.                                                                                                       |

| C2         | n/a     | C2 is unused and does not have a package bump that can be soldered to the PCB                                                                               |

| C5         | GPIO4   | Configurable general-purpose input/open drain output.                                                                                                       |

| D3         | GPIO5   | Configurable general-purpose input/open drain output.                                                                                                       |

| D4         | n/a     | D4 is unused and does not have a package bump that can be soldered to the PCB                                                                               |

| D1         | GPIO7   | Configurable general-purpose input/open drain output.                                                                                                       |

| C1         | FB_B1   | Feedback for Buck1 Regulator. Connect to the Buck1 output capacitor.                                                                                        |

| B4         | AVIN    | Analog Input supply and power input for LDO2. This is also the pin that is monitored for VIN OV and UV. AVIN must be the highest voltage applied to the IC. |

| A1, B1     | VIN_B1  | Dedicated VIN power input for Buck1 Regulator.                                                                                                              |

| A2, B2     | SW_B1   | Switch pin for Buck1 Regulator.                                                                                                                             |

### **ABSOLUTE MAXIMUM RATINGS (NOTE1)**

| PARAMETER                                           | VALUE                 | UNIT |

|-----------------------------------------------------|-----------------------|------|

| All Power pins except PGND1, PGND2, PGND3, AGND     | -0.3 to 6             | V    |

| SDA, SCL, GPIOx, FBx, & LDOx                        | -0.3 to 5.7           | V    |

| Grounds: Any PGND referenced to AGND                | -0.3 to +0.3          | V    |

| SW_Bx to PGNDx                                      | -1 to VIN_Bx + 1      | V    |

| FB_Bx to PGNDx                                      | -0.3 to AVIN + 0.3    | V    |

| LDO1 to AGND                                        | -0.3 to VIN_LDO + 0.3 | V    |

| LDO2 to AGND                                        | -0.3 to AVIN + 0.3    | V    |

| Junction to Ambient Thermal Resistance, CSP (Note2) | 47                    | °C/W |

| Junction to Case Thermal Resistance, CSP (Note 2)   | 0.53                  | °C/W |

| Operating Junction Temperature                      | -40 to 150            | °C   |

| Storage Temperature                                 | -55 to 150            | °C   |

| HBM ESD                                             | 2000                  | V    |

| MSL Rating                                          | 1                     |      |

Note1: Do not exceed these limits to prevent damage to the device. Exposure to absolute maximum rating conditions for long periods may affect device reliability.

Note2: Measured on Qorvo Evaluation Kit.

### **RECOMMENDED OPERATING CONDITIONS**

| PARAMETER                            | TEST CONDITIONS | MIN  | TYP | MAX  | UNIT |

|--------------------------------------|-----------------|------|-----|------|------|

| AVIN, VIN_B1, VIN_B2, VIN_B3 (Note1) |                 | 2.7  |     | 5.5  | V    |

|                                      | LDO Mode        | 1.62 |     | 5.5  | V    |

| VIN_LDO                              | NLSW Mode       | 0.4  |     | 3    | V    |

|                                      | PLSW Mode       | 1.62 |     | AVIN | V    |

| Operating Junction Temperature       |                 | -40  |     | 125  | °C   |

Note1: AVIN must always be the highest input voltage to the IC.

## **DIGITAL I/O ELECTRICAL CHARACTERISTICS**

(AVIN = 3.3V,  $T_j$  = -40°C to +125°C, unless otherwise specified.)

| PARAMETER                     | TEST CONDITIONS | MIN  | TYP | MAX  | UNIT |

|-------------------------------|-----------------|------|-----|------|------|

| GPIOs Leakage Current         | Output = 5V     |      |     | 1    | μA   |

| GPIOs Output Low (Open Drain) | IOL = 1mA       |      |     | 0.35 | V    |

| GPIOs Input Low               |                 |      |     | 0.35 | V    |

| GPIOs Input High              |                 | 1.25 |     |      | V    |

| GPIOs Delay Times             |                 |      | 0   |      |      |

|                               |                 |      | 1   |      |      |

|                               |                 |      | 5   |      | ms   |

|                               |                 |      | 10  |      |      |

| GPIOs Deglitch Time           |                 | 10   |     | 40   | μs   |

### SYSTEM CONTROL ELECTRICAL CHARACTERISTICS

(AVIN = 3.3V,  $T_j$  = -40°C to +125°C, unless otherwise specified.)

| PARAMETER                                                                                                              | TEST CONDITIONS                                                | MIN  | ТҮР       | MAX                           | UNIT |

|------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|------|-----------|-------------------------------|------|

| Supply Inputs Voltage Range:<br>VIN_B1 referenced to PGND1<br>VIN_B2 referenced to PGND2<br>VIN_B3 referenced to PGND3 |                                                                | 2.7  |           | 5.5                           | V    |

|                                                                                                                        | LDO Mode                                                       | 1.62 |           | 5.5                           |      |

| VIN_LDO referenced to AGND                                                                                             | NLSW Mode                                                      | 0.4  |           | Min of<br>(AVIN-1<br>or 3.6V) | V    |

|                                                                                                                        | PLSW Mode                                                      | 1.62 |           | AVIN                          |      |

| LIV/LO Threshold Folling (Note 1)                                                                                      | VIN_LVL=0                                                      | 2.5  | 2.6       | 2.7                           | V    |

| UVLO Threshold Falling (Note 1)                                                                                        | VIN_LVL=1                                                      | 3.35 | 3.5       | 3.65                          | V    |

|                                                                                                                        | VIN_LVL=0                                                      | 50   | 100       | 150                           | mV   |

| UVLO Hysteresis (Note 1)                                                                                               | VIN_LVL=1                                                      | 250  | 300       | 350                           | mV   |

| OV Threshold Rising – VIN_OV (Note 1)                                                                                  | From 3.7V to 5.8V with 0.3V steps. See details in VIN_OV table | -3.5 | SET POINT | 3.5                           | %    |

| OV Hysteresis (Note 1)                                                                                                 |                                                                | 100  | 200       | 300                           | mV   |

| POK OV Interrupt Threshold Rising                                                                                      | From 3.5V to 5.6V with 0.3V steps. See details on POK_OV table | -3.5 | SET POINT | 3.5                           | %    |

| POK OV Interrupt Threshold Hysteresis                                                                                  |                                                                | 100  | 200       | 300                           | mV   |

| POK Deglitch Time OV or UV                                                                                             |                                                                |      | 5         |                               | μs   |

| Operating Supply Consent                                                                                               | All Regulators Disabled<br>nSaveIQQ=1                          |      | 42        |                               | μA   |

| Operating Supply Current                                                                                               | All Regulators Disabled<br>nSaveIQQ=0                          |      | 10        |                               | μA   |

| Operating Supply Current                                                                                               | All Regulators Enabled – No load                               |      | 260       |                               | μA   |

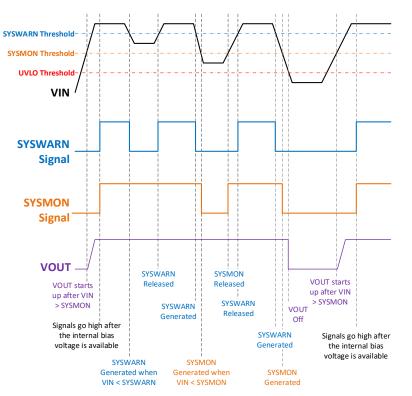

| System Monitor (SYSMON) Programma-<br>ble Range – Rising Threshold                                                     | In 100mV steps                                                 | 2.7  |           | 4.8                           | V    |

| System Monitor (SYSMON) Accuracy                                                                                       |                                                                | -3.5 | SET POINT | 3.5                           | %    |

| System Warning (SYSWARN) Program-<br>mable Range – Rising Threshold                                                    | In 100mV steps                                                 | 2.7  |           | 5.7                           | V    |

| System Warning (SYSWARN) Accuracy                                                                                      | In 100mV steps                                                 | -3.5 | SET POINT | 3.5                           | %    |

| SYSWARN and SYSMON Hysteresis                                                                                          |                                                                | 50   | 100       | 150                           | mV   |

| VIN Deglitch Time UV                                                                                                   | Falling, enter UV                                              |      | 5         |                               | μs   |

| VIN Deglitch Time UV                                                                                                   | Rising, exit UV                                                |      | 100       |                               | μs   |

| VIN Deglitch Time OV                                                                                                   | Rising, enter OV                                               |      | 5         |                               | μs   |

| VIN Deglitch Time OV                                                                                                   | Falling, exit OV                                               |      | 200       |                               | μs   |

| Thermal Shutdown Temperature<br>TSD_SHUTDWN                      | Temperature rising                                                                                                                                  | 155                                      |      | °C |

|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|------|----|

| Thermal Shutdown Hysteresis                                      |                                                                                                                                                     | 30                                       |      | °C |

| Startup Dolov offer initial AV/IN                                | Time from AVIN > UVLO threshold to<br>start of first regulator turning On. (zero<br>turn on delay setting)<br>nSavelQQ=1                            | 620                                      | 750  | μs |

| Startup Delay after initial AVIN                                 | Time from AVIN > UVLO threshold to<br>start of first regulator turning On. (zero<br>turn on delay setting)<br>nSavelQQ=0                            | 920                                      | 1150 | μs |

| Thermal Interrupt Threshold, TSD_ALERT                           | Temperature rising - Referenced to TSD_SHUTDWN                                                                                                      | TSD_SHUTDWN<br>- 30                      |      | °C |

| Thermal Interrupt Hysteresis                                     |                                                                                                                                                     | 20                                       |      | °C |

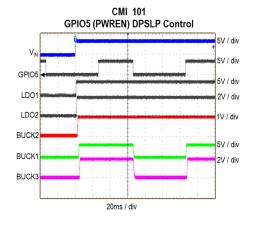

| Transition time from Deep Sleep (DPSLP)<br>State to Active State | Time from PWREN pin low to high tran-<br>sition to time when the first regulator<br>turns ON with minimum turn on delay<br>configuration.           | 224                                      | 500  | μs |

|                                                                  | Using I <sup>2</sup> C                                                                                                                              | 84                                       |      | μs |

| Transition time from Active State to Deep<br>Sleep (DPSLP) State | Time from PWREN pin high to low tran-<br>sition to time when the first regulator<br>turns OFF with minimum turn on delay<br>configuration.          | 224                                      | 500  | μs |

|                                                                  | Using I <sup>2</sup> C                                                                                                                              | 84                                       |      | μs |

| Transition time from Sleep State (SLEEP) to Active State         | Time from I <sup>2</sup> C command to clear sleep<br>mode to time when the first regulator<br>turns ON with minimum turn on delay<br>configuration. | 84                                       |      | μs |

| Time to first power rail turn off                                | Time from turn Off command to when<br>the first power rail turns off with mini-<br>mum turn off delay configuration                                 | 180                                      |      | μs |

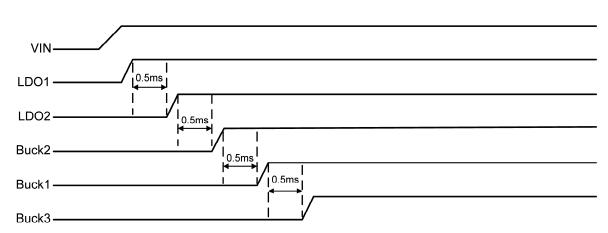

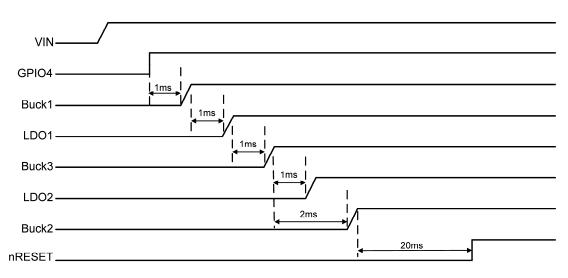

| Startup Delay Programmable Range                                 | ONDLY=000<br>ONDLY=001<br>ONDLY=010<br>ONDLY=011<br>ONDLY=100<br>ONDLY=101<br>ONDLY=110<br>ONDLY=111                                                | 0<br>0.5<br>1<br>2<br>4<br>8<br>16<br>32 |      | ms |

| Turn Off Delay Programmable Range                                | OFFDLY=000<br>OFFDLY=001<br>OFFDLY=010<br>OFFDLY=011<br>OFFDLY=100<br>OFFDLY=101<br>OFFDLY=110<br>OFFDLY=111                                        | 0<br>0.5<br>1<br>2<br>4<br>8<br>16<br>32 |      | ms |

## QOULO

## ACT88321 Advanced PMIC with 3 Bucks, 2 LDOs, and Load Bypass Switches

| nRESET Programmable Range      | TRST_DLY=000<br>TRST_DLY=001<br>TRST_DLY=010<br>TRST_DLY=011<br>TRST_DLY=100<br>TRST_DLY=101<br>TRST_DLY=110<br>TRST_DLY=111 | 0.5<br>1<br>2.5<br>5<br>10<br>20<br>50<br>100 | ms |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|----|

| GPIOs Delay Programmable Range | IOx_DLY=00<br>IOx_DLY=01<br>IOx_DLY=10<br>IOx_DLY=11                                                                         | 0<br>1<br>5<br>10                             | ms |

Note1: All Under-voltage Lockout, Overvoltage measurements are referenced between AVIN and AGND pin.

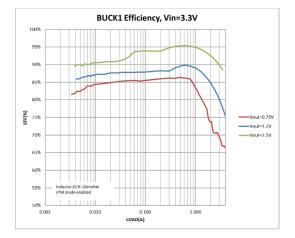

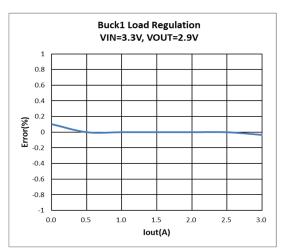

## **BUCK1 ELECTRICAL CHARACTERISTICS, REGULATOR:**

(VIN\_B1 = 3.3V,  $T_j$  = -40°C to +125°C, unless otherwise specified.)

| PARAMETER                                                         | CONDITIONS                                                                                                | MIN  | TYP              | MAX   | UNIT              |

|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|------|------------------|-------|-------------------|

| Operating Voltage Range                                           |                                                                                                           | 2.7  |                  | 5.5   | V                 |

| Output Voltage Range                                              | Configured for 25mV steps                                                                                 | 0.6  |                  | 3.775 | V                 |

| Maximum Output Current (Note1)                                    |                                                                                                           | 4    |                  |       | A                 |

| Maximum Operation Duty Cycle                                      |                                                                                                           | 99   |                  |       | %                 |

|                                                                   | Low Power Mode Enabled<br>Regulator Only, No Load (VOUT = VSET*1.05)                                      |      | 40               |       | μA                |

| Supply Current, Standby                                           | ULPM Mode Enabled<br>Regulator Only, No Load (VOUT =<br>VSET*1.05), IC is in SLEEP or DEEP SLEEP<br>Mode. |      | 10               |       | μΑ                |

| Supply Current Shutdown                                           | Regulator Disabled (Note2)                                                                                |      | 0.1              | 1     | μA                |

| Supply Current, Shutdown                                          | Regulator Disabled                                                                                        |      | 0.1              | 7.5   | uA                |

| Output Voltage Accuracy – PWM (Note2)                             | Default output voltage, I <sub>OUT</sub> = 2A                                                             | -1   | V <sub>NOM</sub> | 1     | %                 |

| Output Voltage Accuracy – PWM                                     | Default output voltage, I <sub>OUT</sub> = 2A                                                             | -1.5 | V <sub>NOM</sub> | 1.5   | %                 |

| Output Voltage Accuracy – PFM (Note2)                             | Default output voltage, I <sub>OUT</sub> = 1mA, Average<br>Ripple Voltage                                 | -1   | VNOM             | 1     | %                 |

| Output Voltage Accuracy – PFM                                     | Default output voltage, I <sub>OUT</sub> = 1mA, Average<br>Ripple Voltage                                 | -1.5 | VNOM             | 1.5   | %                 |

| Line Regulation                                                   | Default output voltage, $V_{IN_B1}$ = 3.3V to 5.5V, PWM mode                                              |      | 0.05             |       | %/V               |

| Load Regulation                                                   | Default output voltage, PWM Mode                                                                          |      | 0.05             |       | %/A               |

| Power Good Threshold                                              | Vout_B1 Rising                                                                                            | 90   | 93               | 96    | %V <sub>NOM</sub> |

| Power Good Hysteresis                                             | Vout_B1 Falling                                                                                           |      | 3                |       | %V <sub>NOM</sub> |

| Overvoltage Fault Threshold                                       | Vout_B1 Rising                                                                                            | 107  | 110              | 113   | %V <sub>NOM</sub> |

| Overvoltage Fault Hysteresis                                      | Vout_B1 Falling                                                                                           |      | 3                |       | %V <sub>NOM</sub> |

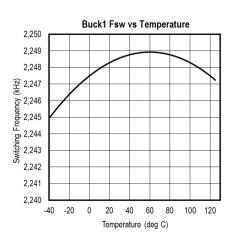

|                                                                   |                                                                                                           | 2.00 | 2.25             | 2.36  | MHz               |

| Switching Frequency                                               |                                                                                                           | 1.00 | 1.125            | 1.18  | MHz               |

| Soft-Start Period – Programmable                                  | 10% to 90% V <sub>NOM</sub>                                                                               |      | 250<br>500       |       | μs                |

| Soft-Start Period                                                 | Variation from set point                                                                                  | -40  |                  | 40    | %                 |

| Internal High Side Peak Current<br>Limit (Cycle-by-Cycle) ILIMSET | B1_ILIMSET=0<br>B1_ILIMSET=1                                                                              |      | 3.8<br>5.0       |       | А                 |

| Internal High Side Peak Current                                   | At default ILIMSET                                                                                        | -25  | ILIMSET          | 25    | %                 |

| Limit (Cycle-by-Cycle) Tolerance                                  | At other set points                                                                                       | -30  | ILIMSET          | 30    | 1                 |

| Internal High Side Peak Current<br>Limit, Shutdown Level          | Above ILIMSET = all settings                                                            | 10 | 25                                     | 40                                                                         | %    |

|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----|----------------------------------------|----------------------------------------------------------------------------|------|

| Low Side Peak Current Limit (Cy-<br>cle-by-Cycle) ILIMSET (Note3) | B1_ILIMSET=0<br>B1_ILIMSET=1                                                            |    | 3.8<br>5.0                             |                                                                            | А    |

| PMOS On-Resistance                                                | Isw = -1A, VIN_B1 = 3.3V                                                                |    | 30                                     |                                                                            | mΩ   |

| NMOS On-Resistance                                                | Isw = 1A, VIN_B1 = 3.3V                                                                 |    | 40                                     |                                                                            | mΩ   |

|                                                                   | V <sub>IN_B1</sub> = 5V, V <sub>SW</sub> = 5V (Note2)                                   |    | 0.1                                    | 1                                                                          | μA   |

| SW Leakage Current – NMOS                                         | V <sub>IN_B1</sub> = 5V, V <sub>SW</sub> = 5V                                           |    | 0.1                                    | .0<br>.0<br>.0<br>.1 1<br>.1 1.5<br>.1 2.5<br>.1 9.0<br>2/2<br>1.9<br>'1.8 | uA   |

| SW/Leekere Current DMOS                                           | V <sub>IN_B1</sub> = 5V, V <sub>SW</sub> = 0V (Note2)                                   |    | 0.1                                    | 2.5                                                                        | μA   |

| SW Leakage Current – PMOS                                         | V <sub>IN_B1</sub> = 5V, V <sub>SW</sub> = 0V                                           |    | 0.1                                    | 1<br>1.5<br>2.5                                                            | uA   |

| Switching Rise / Fall Times                                       | V <sub>IN_B1</sub> = 5V<br>B1_DRVADJ=00<br>B1_DRVADJ=01<br>B1_DRVADJ=10<br>B1_DRVADJ=11 |    | 2.2/2<br>1.9/1.9<br>1.7/1.8<br>1.6/1.7 |                                                                            | ns   |

| Output Pull Down Resistance                                       | Enabled when regulator disabled                                                         |    | 4.4                                    |                                                                            | Ohms |

Note1: There are two balls for VIN\_B1 and SW\_B1 which is good for 4A average lifetime rating at 105 deg C junction. Note2:  $T_A = +25^{\circ}C$

Note3: LSILIM is used for current run-away protection. It is only enabled when the top FET on-time is less than 120ns.

## **BUCK1 ELECTRICAL CHARACTERISTICS, REGULATOR: – BYPASS MODE OPTION**

(VIN\_B1 = 3.3V,  $T_j$  = -40°C to +125°C, unless otherwise specified.)

| PARAMETER                                        | CONDITIONS                                                | MIN | ТҮР | MAX | UNIT  |

|--------------------------------------------------|-----------------------------------------------------------|-----|-----|-----|-------|

| Bypass Mode                                      |                                                           |     |     |     |       |

| Input Voltage Range for By-Pass<br>Mode          |                                                           | 2.7 | 3.3 | 3.7 | V     |

| PMOS On-Resistance                               | I <sub>SW</sub> = -1A, VIN = 3.3V                         |     | 30  |     | mΩ    |

| Internal PMOS Current Detection                  | Triggers Interrupt on IRQ Pin                             | 1.6 | 2.5 | 3.6 | Α     |

| Internal PMOS Current Detection<br>Deglitch Time |                                                           |     | 10  |     | μs    |

| Internal PMOS Current Shutdown (Note1)           | Shuts down after deglitch time and stays off for Off Time | 3.1 | 4.5 | 5.8 | А     |

| Internal PMOS Current Shutdown<br>Deglitch Time  |                                                           |     | 10  |     | μs    |

| Internal PMOS Current Shutdown<br>Off time       |                                                           |     | 14  |     | ms    |

| Internal PMOS Softstart                          | Only used with 3.3V Input                                 |     | 6.6 |     | mV/us |

| Overvoltage Protection Threshold                 |                                                           |     | 3.8 |     | V     |

| OV Deglitch Time                                 |                                                           |     | 10  |     | μs    |

Note1: There are two balls for VIN\_B1 and SW\_B1 which is good for 4A average lifetime rating at 105 deg C junction.

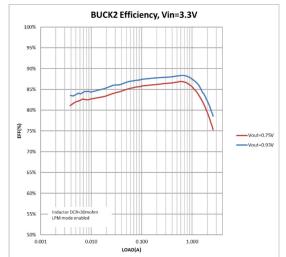

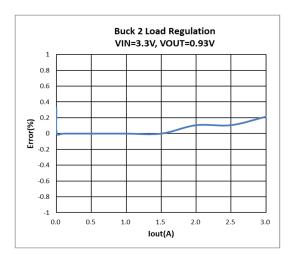

## **BUCK2 ELECTRICAL CHARACTERISTICS, REGULATORS:**

(VIN\_B2 = 3.3V,  $T_j$  = -40°C to +125°C, unless otherwise specified.)

| PARAMETER                                                         | CONDITIONS                                                                                           | MIN | ТҮР                      | MAX  | UNIT              |

|-------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-----|--------------------------|------|-------------------|

| Operating Voltage Range                                           |                                                                                                      | 2.7 |                          | 5.5  | V                 |

| Output Voltage Range                                              | Configured for 10mV steps                                                                            | 0.5 |                          | 1.77 | v                 |

| Maximum Output Current<br>(Note1)                                 |                                                                                                      | 4   |                          |      | A                 |

| Sumply Current Standby                                            | Ultra Low Power Mode Enabled,<br>Regulator Current Only, No Switching<br>(VFB_B2 = VSET*1.05)        |     | 12                       |      | μΑ                |

| Supply Current, Standby                                           | Low Power Mode Enabled,<br>Regulator Current Only, No Switching<br>(VFB_B2 = VSET*1.05)              |     | 38                       |      | μΑ                |

| Supply Current Shutdown                                           | Regulator Disabled (Note2)                                                                           |     | 0.1                      | 1    | μA                |

| Supply Current, Shutdown                                          | Regulator Disabled                                                                                   |     | 0.1                      | 5.5  | μA                |

| Output Voltage Accuracy –<br>CCM (Note2)                          | Default output voltage, Iout = 1A                                                                    | -1  | V <sub>NOM</sub>         | 1    | %                 |

| Output Voltage Accuracy –<br>CCM                                  | Default output voltage, I <sub>OUT</sub> = 1A                                                        | -2  | V <sub>NOM</sub>         | 2    | %                 |

| Output Voltage Accuracy –<br>DCM(Note2)                           | Default output voltage, I <sub>OUT</sub> = 1mA,<br>Average Ripple Voltage                            | -1  | V <sub>NOM</sub> + 3%    | 1    | %                 |

| Output Voltage Accuracy –<br>DCM                                  | Default output voltage, I <sub>OUT</sub> = 1mA,<br>Average Ripple Voltage, Low Power Mode<br>Enabled | -2  | V <sub>NOM</sub> + 3%    | 2    | %                 |

| Line Regulation                                                   | Default output voltage, $V_{IN_B2}$ = 3.3V to 5.5V, CCM mode                                         |     | 0.05                     |      | %/V               |

| Load Regulation                                                   | Default output voltage, CCM Mode                                                                     |     | 0.05                     |      | %/A               |

| Power Good Threshold                                              | Vout_b2 Rising                                                                                       | 90  | 93                       | 96   | %V <sub>NOM</sub> |

| Power Good Hysteresis                                             | V <sub>OUT_B2</sub> Falling                                                                          |     | 3                        |      | %V <sub>NOM</sub> |

| Overvoltage Fault Threshold                                       | Vout_b2 Rising                                                                                       | 107 | 110                      | 113  | %V <sub>NOM</sub> |

| Overvoltage Fault Hysteresis                                      | Vout_b2 Falling                                                                                      |     | 3                        |      | %V <sub>NOM</sub> |

| Emulated Switching Frequency                                      | FSET=00<br>FSET=01<br>FSET=10<br>FSET=11                                                             |     | 1.5<br>2.0<br>2.5<br>3.3 |      | MHz               |

| Soft-Start Period – Programma-<br>ble                             | 10% to 90% V <sub>NOM</sub>                                                                          |     | 50<br>100<br>250<br>500  |      | μs                |

| Soft-Start Period                                                 | Variation from set point                                                                             | -40 |                          | 40   | %                 |

| Internal High Side Peak Current<br>Limit (Cycle-by-Cycle) ILIMSET | B2_ILIMSET=0<br>B2_ILIMSET=1                                                                         |     | 3.8<br>5.0               |      | А                 |

|                                                                   | At default ILIMSET                                                                                   | -15 | ILIMSET                  | 15   | %                 |

| Internal High Side Peak Current<br>Limit (Cycle-by-Cycle) Toler-<br>ance | At other set points                                                                     | -20 | ILIMSET                                  | 20  | %     |

|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----|------------------------------------------|-----|-------|

| Low Side Peak Current Limit<br>(Cycle-by-Cycle) ILIMSET<br>(Note3)       | B2_ILIMSET=0<br>B2_ILIMSET=1                                                            |     | 3.8<br>5.0                               |     | A     |

| PMOS On-Resistance                                                       | I <sub>SW</sub> = -500mA, VIN_B2 = 3.3V                                                 |     | 50                                       |     | mΩ    |

| NMOS On-Resistance                                                       | Isw = 500mA, VIN_B2 = 3.3V                                                              |     | 22                                       |     | mΩ    |

| SW Leakage Current – NMOS                                                | V <sub>IN_B2</sub> = 5V, V <sub>SW</sub> = 5V (Note2)                                   |     | 0.1                                      | 1   | μA    |

|                                                                          | V <sub>IN_B2</sub> = 5V, V <sub>SW</sub> = 5V                                           |     | 0.1                                      | 2   | μA    |

|                                                                          | V <sub>IN_B2</sub> = 5V, V <sub>SW</sub> = 0V (Note2)                                   |     | 0.1                                      | 1.5 | μA    |

| SW Leakage Current – PMOS                                                | V <sub>IN_B2</sub> = 5V, V <sub>SW</sub> = 0V                                           |     | 0.1                                      | 6   | μA    |

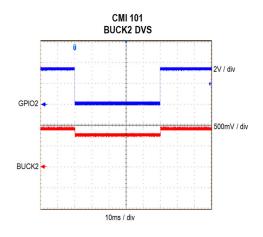

| Dynamic Voltage Scaling Rate                                             | B2_SLEW=00<br>B2_SLEW=01<br>B2_SLEW=10<br>B2_SLEW=11                                    |     | 22.5<br>11.25<br>5.625<br>2.8125         |     | mV/µs |

| Switching Rise / Fall Times                                              | V <sub>IN_B2</sub> = 5V<br>B2_DRVADJ=00<br>B2_DRVADJ=01<br>B2_DRVADJ=10<br>B2_DRVADJ=11 |     | 1.4/1.4<br>1.2/1.3<br>1.1/1.2<br>1.0/1.1 |     | ns    |

| Output Pull Down Resistance                                              | Enabled when regulator disabled                                                         |     | 9.40                                     |     | Ohms  |

Note1: There is one ball for VIN\_B2 and two balls for SW\_B2 which is good for 2A and 4A average lifetime rating at 105 deg C junction. Note2:  $T_A = 25^{\circ}C$

Note3: LSILIM is used for current run-away protection. It is only enabled when the top FET on-time is less than 120ns.

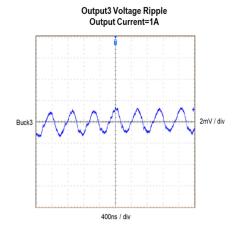

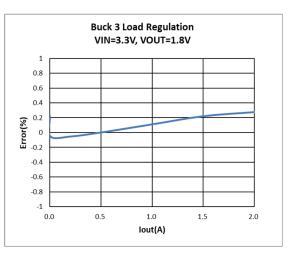

## **BUCK3 ELECTRICAL CHARACTERISTICS, REGULATORS:**

(VIN\_B3 = 3.3V,  $T_j$  = -40°C to +125°C, unless otherwise specified.)

| PARAMETER                                                         | CONDITIONS                                                                                    | MIN | ТҮР                      | MAX | UNIT              |

|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----|--------------------------|-----|-------------------|

| Operating Voltage Range                                           |                                                                                               | 2.7 |                          | 5.5 | V                 |

| Output Voltage Range                                              | Configured for 100mV steps                                                                    | 0.5 |                          | 3.6 | V                 |

| Maximum Output Current (Note1)                                    |                                                                                               | 2   |                          |     | А                 |

|                                                                   | Ultra Low Power Mode Enabled,<br>Regulator Current Only, No Switching<br>(VFB_B3 = VSET*1.05) |     | 12                       |     | μA                |

| Supply Current, Standby                                           | Low Power Mode Enabled,<br>Regulator Current Only, No Switching<br>(VFB_B3 = VSET*1.05)       |     | 38                       |     | μA                |

| Supply Current Shutdown                                           | Regulator Disabled (Note2)                                                                    |     | 0.1                      | 1   | μA                |

| Supply Current, Shutdown                                          | Regulator Disabled                                                                            |     | 0.1                      | 4.5 | μA                |

| Output Voltage Accuracy – CCM (Note2)                             | Default output voltage, I <sub>OUT</sub> = 1A                                                 | -1  | VNOM                     | 1   | %                 |

| Output Voltage Accuracy – CCM                                     | Default output voltage, I <sub>OUT</sub> = 1A                                                 | -2  | V <sub>NOM</sub>         | 2   | %                 |

| Output Voltage Accuracy – DCM<br>(Note2)                          | Default output voltage, I <sub>OUT</sub> = 1mA,<br>Average Ripple Voltage                     | -1  | V <sub>NOM</sub> + 3%    | 1   | %                 |

| Output Voltage Accuracy – DCM                                     | Default output voltage, I <sub>OUT</sub> = 1mA,<br>Average Ripple Voltage                     | -2  | V <sub>NOM</sub> + 3%    | 2   | %                 |

| Line Regulation                                                   | Default output voltage, $V_{IN_{B3}}$ = 3.3V to 5.5V, CCM mode                                |     | 0.05                     |     | %/V               |

| Load Regulation                                                   | Default output voltage, CCM Mode                                                              |     | 0.05                     |     | %/A               |

| Power Good Threshold                                              | V <sub>OUT_B3</sub> Rising                                                                    | 90  | 93                       | 96  | %V <sub>NOM</sub> |

| Power Good Hysteresis                                             | Vout_B3 Falling                                                                               |     | 3                        |     | %V <sub>NOM</sub> |

| Overvoltage Fault Threshold                                       | VOUT_B3 Rising                                                                                | 107 | 110                      | 113 | %V <sub>NOM</sub> |

| Overvoltage Fault Hysteresis                                      | Vout_B3 Falling                                                                               |     | 3                        |     | %V <sub>NOM</sub> |

| Emulated Switching Frequency                                      | FSET=00<br>FSET=01<br>FSET=10<br>FSET=11                                                      |     | 1.5<br>2.0<br>2.5<br>3.3 |     | MHz               |

| Soft-Start Period – Programmable<br>Range                         | 10% to 90% V <sub>NOM</sub>                                                                   |     | 50<br>100<br>250<br>500  |     | μs                |

| Soft-Start Period                                                 | Variation from set point                                                                      | -40 |                          | 40  | %                 |

| Internal High Side Peak Current<br>Limit (Cycle-by-Cycle) ILIMSET | B3_ILIMSET=0<br>B3_ILIMSET=1                                                                  |     | 2.0<br>3.0               |     | А                 |

| Internal High Side Peak Current                                   | At default ILIMSET                                                                            | -15 | ILIMSET                  | 15  | %                 |

| Limit (Cycle-by-Cycle) Tolerance                                  | At other set points                                                                           | -20 | ILIMSET                  | 20  | %                 |

| Low Side Peak Current Limit (Cy-<br>cle-by-Cycle) ILIMSET (Note3) | B3_ILIMSET=0<br>B3_ILIMSET=1                                                                  |     | 2.0<br>3.0               |     | А                 |

## QOUND

### ACT88321 Advanced PMIC with 3 Bucks, 2 LDOs, and Load Bypass Switches

| PMOS On-Resistance          | I <sub>SW</sub> = -500mA, VIN_B3 = 3.3V                               | 75                                       | mΩ   |

|-----------------------------|-----------------------------------------------------------------------|------------------------------------------|------|

| NMOS On-Resistance          | I <sub>SW</sub> = 500mA, VIN_B3 = 3.3V                                | 70                                       | mΩ   |

| SW Leakage Current – NMOS   | V <sub>IN_B3</sub> = 5V, V <sub>SW</sub> = 5V                         | 0.1 1                                    | μA   |

|                             | V <sub>IN_B3</sub> = 5V, V <sub>SW</sub> = 0V (Note2)                 | 0.1 1                                    | μA   |

| SW Leakage Current – PMOS   | V <sub>IN_B3</sub> = 5V, V <sub>SW</sub> = 0V                         | 0.1 4.5                                  | μA   |

| Switching Rise / Fall Times | $V_{IN\_B3} = 5V$ B3_DRVADJ=00 B3_DRVADJ=01 B3_DRVADJ=10 B3_DRVADJ=11 | 1.2/1.3<br>1.1/1.2<br>1.0/1.1<br>0.9/1.0 | ns   |

| Output Pull Down Resistance | Enabled when regulator disabled                                       | 9.40                                     | Ohms |

Note1: There is one ball for VIN\_B3 and SW\_B3 which is good for 2A average lifetime rating at 105 deg C junction.

Note2:  $T_A = +25^{\circ}C$

Note3: LSILIM is used for current run-away protection. It is only enabled when the top FET on-time is less than 120ns.

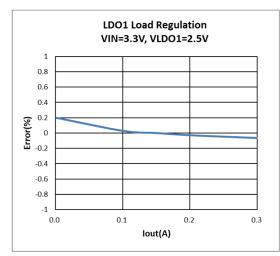

## LDO1 ELECTRICAL CHARACTERISTICS

(VIN\_LDO1 = 3.3V,  $T_j$  = -40°C to +125°C, unless otherwise specified.)

| PARAMETER                          | TEST CONDITIONS                                                                               | MIN        | TYP              | MAX  | UNIT              |

|------------------------------------|-----------------------------------------------------------------------------------------------|------------|------------------|------|-------------------|

| Operating Voltage Range            |                                                                                               | 1.62       |                  | 5.5  | V                 |

| Output Voltage Range               | Configurable in 50mV steps                                                                    | 0.6        |                  | 3.75 | V                 |

| Output Current                     | VIN_LDO1 = 1.62V to 5.5V, LDO1_ILIM=1                                                         | 0.39       |                  |      | А                 |

| Output Voltage Accuracy<br>(Note1) | At default output voltage setting<br>V <sub>IN_LDO</sub> - V <sub>LDO1</sub> > 0.4V           | -1         | VNOM             | 1    | %                 |

| Output Voltage Accuracy            | At default output voltage setting<br>V <sub>IN_LDO -</sub> V <sub>LDO1</sub> > 0.4V           | -1.5       | V <sub>NOM</sub> | 1.5  | %                 |

| Line Regulation                    | $V_{IN\_LDO} \cdot V_{LDO1} > 0.4V$<br>$V_{IN\_LDO} = 2.7V$ to 5.5V<br>$I_{LDO1} = 1mA$       |            | 0.01             |      | % / V             |

| Load Regulation                    | $I_{LDO1}$ = 1mA to 390mA, ILIM_SCL_LDO1=1 $V_{IN\_LDO}$ . $V_{LDO1}$ > 0.4V                  |            | 0.025            |      | % / A             |

| Sumply Current                     | Regulator Enabled No Load                                                                     |            | 14               | 30   | μA                |

| Supply Current                     | Regulator Disabled                                                                            |            | 0                | 1    | μA                |

| Soft-Start Period                  | LDO1_SS = 0. V <sub>LDO1</sub> = 10% to 90%<br>LDO1_SS = 1. V <sub>LDO1</sub> = 10% to 90%    |            | 200<br>360       |      | μs                |

| Power Good Threshold               | V <sub>LDO1</sub> Rising                                                                      | 90         | 93               | 96   | %V <sub>NOM</sub> |

| Power Good Hysteresis              | V <sub>LD01</sub> Falling                                                                     |            | 3                |      | %V <sub>NOM</sub> |

| Overvoltage Fault Threshold        | V <sub>LD01</sub> Rising                                                                      | 107        | 110              | 113  | %V <sub>NOM</sub> |

| Overvoltage Fault Hysteresis       | V <sub>LDO1</sub> Falling                                                                     |            | 3                |      | %V <sub>NOM</sub> |

|                                    | I <sub>LDO1</sub> = 200mA, V <sub>IN_LDO</sub> > 2.7V, LDO1_ILIM=0                            |            |                  | 200  | mV                |

|                                    | I <sub>LDO1</sub> = 400mA, V <sub>IN_LDO</sub> > 2.7V, LDO1_ILIM=1                            |            |                  | 400  | mV                |

| Dropout Voltage                    | $I_{LDO1}$ = 200mA, $V_{IN\_LDO}$ = 1.6V, LDO1_ILIM=0                                         |            | 225              |      | mV                |

|                                    | I <sub>LDO1</sub> = 400mA, V <sub>IN_LDO</sub> = 1.6V, LDO1_ILIM=1                            |            | 670              |      | mV                |

| Discharge Resistance               | Enabled when regulator disabled                                                               | 10         | 20               | 35   | Ω                 |

| Output Current Limit               | $V_{IN\_LDO}$ = 2.7V to 5.5V, $V_{IN\_LDO}$ - $V_{LDO1}$ > 0.4V<br>LDO1_ILIM=0<br>LDO1_ILIM=1 | 310<br>390 | 400<br>500       |      | mA                |

| Short Output Foldback Current      |                                                                                               |            | 35               |      | %                 |

Note1:  $T_A = 25^{\circ}C$

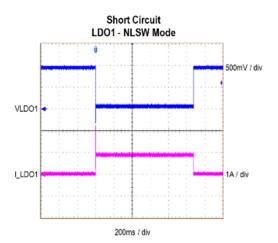

## LDO1 ELECTRICAL CHARACTERISTICS – LOAD SWITCH

(VIN\_LDO1 = 3.3V,  $T_j$  = -40°C to +125°C, unless otherwise specified.)

| PARAMETER                         | TEST CONDITIONS                                                                                                | MIN                          | TYP                         | MAX                                    | UNIT |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------|------------------------------|-----------------------------|----------------------------------------|------|

| Load Switch Operation Range       | NLSW Mode, Input Voltage Range of VIN_LDO                                                                      | 0.4                          |                             | Mini-<br>mum of<br>(AVIN-1<br>or 3.6V) | V    |

|                                   | PLSW Mode, Input Voltage Range of VIN_LDO                                                                      | 1.62                         |                             | AVIN                                   | V    |

|                                   | NLSW Mode, V <sub>LD01_IN</sub> = 0.4V I <sub>LD01</sub> = 100mA                                               |                              | 55                          |                                        | mΩ   |

| Load Switch On-Resistance         | NLSW Mode, V <sub>LD01_IN</sub> = 3.3V I <sub>LD01</sub> = 100mA                                               |                              | 310                         |                                        | mΩ   |

|                                   | PLSW Mode, V <sub>LD01_IN</sub> = 3.3V I <sub>LD01</sub> = 100mA                                               |                              | 380                         |                                        | mΩ   |

|                                   | NLSW Mode. Load Switch Enabled. No Load                                                                        |                              | 16                          |                                        |      |

| Load Switch Supply Current        | PLSW Mode. Load Switch Enabled. No Load                                                                        |                              | 20                          |                                        | μA   |

|                                   | Load Switch Disabled                                                                                           |                              | 0                           | 1                                      |      |

|                                   | NLSW Mode                                                                                                      |                              | 200                         |                                        | μs   |

| Soft-Start Period                 | PLSW Mode. Load Switch Uses Current Limit to accomplish softstart                                              |                              | N/A                         |                                        |      |

| Output Current Limit              | NLSW Mode: NLSW1_ILIM = 0<br>NLSW Mode: NLSW1_ILIM = 1<br>PLSW Mode: LDO1_ILIM = 0<br>PLSW Mode: LDO1_ILIM = 1 | 0.49<br>0.84<br>0.31<br>0.39 | 0.65<br>1.1<br>0.33<br>0.48 |                                        | mA   |

| Over Voltage Protection Threshold |                                                                                                                |                              | 3.8                         |                                        | V    |

| OV Deglitch Time                  |                                                                                                                |                              | 10                          |                                        | μs   |

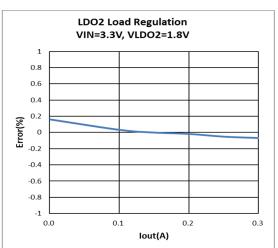

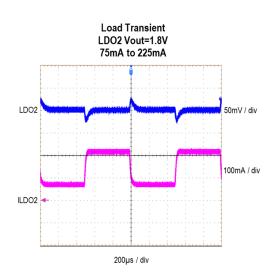

### LDO2 ELECTRICAL CHARACTERISTICS

(AVIN = 3.3V,  $T_j$  = -40°C to +125°C, unless otherwise specified.)

| PARAMETER                       | TEST CONDITIONS                                                                                            | MIN        | TYP              | MAX        | UNIT              |

|---------------------------------|------------------------------------------------------------------------------------------------------------|------------|------------------|------------|-------------------|

| Operating Voltage Range         |                                                                                                            | 2.7        |                  | 5.5        | V                 |

| Output Voltage Range            | Configurable in 50mV steps                                                                                 | 0.6        |                  | 3.75       | v                 |

| Output Current                  | AVIN = 2.7V to 5.5V, LDO2_ILIM=1                                                                           | 0.39       |                  |            | А                 |

| Output Voltage Accuracy (Note1) | At default output voltage setting<br>AVIN - V <sub>LDO2_OUT</sub> > 0.4V                                   | -1         | $V_{\text{SET}}$ | 1          | %                 |

| Output Voltage Accuracy         | At default output voltage setting<br>AVIN - V <sub>LDO2_OUT</sub> > 0.4V                                   | -1.5       | VSET             | 1.5        | %                 |

| Line Regulation                 | AVIN - V <sub>LDO2_OUT</sub> > 0.4V<br>AVIN = 2.7V to 5.5V<br>I <sub>LDO2_OUT</sub> = 1mA                  |            | 0.01             |            | % / V             |

| Load Regulation                 | I <sub>LDO2_OUT</sub> = 1mA to 390mA, LDO2_ILIM=1<br>AVIN - V <sub>LDO2_OUT</sub> > 0.4V                   |            | 0.025            |            | %/A               |

| Querra la Querra at             | Regulator Enabled, No Load                                                                                 |            | 14               | 30         | μA                |

| Supply Current                  | Regulator Disabled                                                                                         |            | 0                | 1          | μA                |

| Soft-Start Period               | LDO2_SS = 0. V <sub>LDO1</sub> = 10% to 90%<br>LDO2_SS = 1. V <sub>LDO1</sub> = 10% to 90%                 |            | 200<br>360       |            | μs                |

| Power Good Threshold            | VLD02_OUT Rising                                                                                           | 90         | 93               | 96         | %V <sub>NOM</sub> |

| Power Good Hysteresis           | VLD02_OUT Falling                                                                                          |            | 3                |            | %V <sub>NOM</sub> |

| Overvoltage Fault Threshold     | V <sub>LD02_OUT</sub> Rising                                                                               | 107        | 110              | 113        | %V <sub>NOM</sub> |

| Overvoltage Fault Hysteresis    | VLD02_OUT Falling                                                                                          |            | 3                |            | %V <sub>NOM</sub> |

|                                 | I <sub>LDO2</sub> = 200mA, AVIN > 2.7V, LDO2_ILIM=0<br>I <sub>LDO2</sub> = 400mA, AVIN > 2.7V, LDO2_ILIM=1 |            |                  | 200<br>400 | mV                |

| Dropout Voltage                 | I <sub>LDO1</sub> = 200mA, V <sub>IN_LDO</sub> = 1.6V, LDO1_ILIM=0                                         |            | 225              |            | mV                |

|                                 | I <sub>LDO1</sub> = 400mA, V <sub>IN_LDO</sub> = 1.6V, LDO1_ILIM=1                                         |            | 670              |            | mV                |

| Discharge Resistance            | Enabled when regulator disabled                                                                            | 10         | 20               | 35         | Ω                 |

| Output Current Limit            | AVIN = 2.7V to 5.5V, AVIN – $V_{LDO1} > 0.4V$<br>LDO2_ILIM=0<br>LDO2_ILIM=1                                | 310<br>390 | 400<br>500       | 500<br>600 | mA                |

| Short Output Foldback Current   |                                                                                                            |            | 35               |            | %                 |

## I<sup>2</sup>C INTERFACE ELECTRICAL CHARACTERISTICS

(AVIN = 3.3V,  $T_j$  = -40°C to +125°C, unless otherwise specified.)

| PARAMETER                                               | TEST CONDITIONS       | MIN  | TYP | MAX  | UNIT |

|---------------------------------------------------------|-----------------------|------|-----|------|------|

| SCL, SDA Input Low                                      | AVIN = 3.3V           |      |     | 0.4  | V    |

| SCL, SDA Input High                                     | AVIN = 3.3V           | 1.25 |     |      | V    |

| SDA Leakage Current                                     | SDA=5V                |      |     | 1    | μA   |

| SDA Output Low                                          | I <sub>OL</sub> = 5mA |      |     | 0.35 | V    |

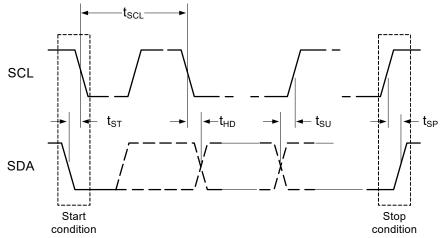

| SCL Clock Frequency, f <sub>SCL</sub>                   |                       | 0    |     | 1000 | kHz  |

| SCL Low Period, t <sub>LOW</sub>                        |                       | 0.5  |     |      | μs   |

| SCL High Period, t <sub>HIGH</sub>                      |                       | 0.26 |     |      | μs   |

| SDA Data Setup Time, t <sub>su</sub>                    |                       | 50   |     |      | ns   |

| SDA Data Hold Time, t <sub>HD</sub>                     | (Note1)               | 0    |     |      | ns   |

| Start Setup Time, t <sub>ST</sub>                       | For Start Condition   | 260  |     |      | ns   |

| Stop Setup Time, t <sub>SP</sub>                        | For Stop Condition    | 260  |     |      | ns   |

| Capacitance on SCL or SDA Pin                           |                       |      |     | 10   | pF   |

| SDA Fall Time SDA, T <sub>of</sub>                      | Device requirement    |      |     | 120  | ns   |

| Pulse Width of spikes must be suppressed on SCL and SDA |                       | 0    |     | 50   | ns   |

Note1: Comply to I<sup>2</sup>C timings for 1MHz operation - "Fast Mode Plus".

Note2: No internal timeout for  $I^2C$  operations, however,  $I^2C$  communication state machine will be reset when entering RESET, IDLE, OVUVFLT, and THERMAL states to clear any transactions that may have been occurring when entering the above states.

Note3: This is an I<sup>2</sup>C system specification only. Rise and fall time of SCL & SDA not controlled by the device.

Note4: Device Address is 7'h5A

Figure 2: I<sup>2</sup>C Data Transfer

## SYSTEM CONTROL INFORMATION

#### General

The ACT88321 is a single-chip integrated power management solution designed to power many processors. It integrates three highly efficient buck regulators, and two LDOs. Its high integration and high switching frequency result in an extremely small footprint and lowcost power solution. It contains a master controller that manages startup sequencing, timing, voltages, slew rates, sleep states, and fault conditions. I<sup>2</sup>C configurability allows system level changes without the need for costly PCB changes. The built-in load bypass switch enables full sequencing configurability in 3.3V systems.

The ACT88321 master controller monitors all outputs and reports faults via  $l^2C$  and hardwired status signals. Faults can be masked, and fault levels and responses are configurable via  $l^2C$ .

Many of the ACT88321 GPIOs and functions are configurable. The IC's default functionality is defined by the default CMI (Code Matrix Index), but much of this functionality can be changed via I<sup>2</sup>C. The first part of the datasheet describes basic IC functionality and default pin functions. The last section of the datasheet provides the configuration and functionality specific to each CMI version. Contact <u>sales@gorvo.com</u> for additional information about other configurations.

#### I<sup>2</sup>C Serial Interface

To ensure compatibility with a wide range of systems, the ACT88321 uses standard I<sup>2</sup>C commands. The ACT88321 always operates as a slave device and is addressed using a 7-bit slave address followed by an eighth bit, which indicates whether the transaction is a read-operation or a write-operation. Refer to each specific CMI for the IC's slave address

There is no timeout function in the  $l^2C$  packet processing state machine, however, any time the  $l^2C$  state machine receives a start bit command, it immediately resets the packet processing, even if it is in the middle of a valid packet.

I<sup>2</sup>C commands are communicated using the SCL and SDA pins. SCL is the I<sup>2</sup>C serial clock input. SDA is the data input and output. SDA is open drain and must have a pullup resistor. Signals on these pins must meet timing requirements in the Electrical Characteristics Table.

#### Table 1: ACT88321 I<sup>2</sup>C Addresses

| 7-Bit Slav | e Address | 8-Bit Write<br>Address | 8-Bit Read<br>Address |

|------------|-----------|------------------------|-----------------------|

| 0x25h      | 010 0101b | 0x4Ah                  | 0x4Bh                 |

| 0x27h      | 010 0111b | 0x4Eh                  | 0x4Fh                 |

| 0x67h      | 110 0111b | 0xCEh                  | 0xCFh                 |

| 0x6Bh      | 110 1011b | 0xD6h                  | 0xD7h                 |

#### **I2C Registers**

The ACT88321 has an array of internal registers that contain the IC's basic instructions for setting up the IC configuration, output voltages, switching frequency, fault thresholds, fault masks, etc. These registers give the IC its operating flexibility. The two types of registers are described below.

Basic Volatile – These are R/W (Read and Write) and RO (Read only). After the IC is powered, the user can modify the R/W register values to change IC functionality. Changes in functionality include things like masking certain faults. The RO registers communicate IC status such as fault conditions. Any changes to these registers are lost when power is recycled. The default values are fixed and cannot be changed by the factory or the end user.

Basic Non-Volatile – These are R/W and RO. After the IC is powered, the user can modify the R/W register values to change IC functionality. Changes in functionality include things like output voltage settings, startup delay time, and current limit thresholds. Any changes to these registers are lost when power is recycled. The default values can be modified at the factory to optimize IC functionality for specific applications. Please contact Qorvo for custom options and minimum order quantities.

When modifying only certain bits within a register, take care to not inadvertently change other bits. Inadvertently changing register contents can lead to unexpected device behavior.

#### **State Machine**

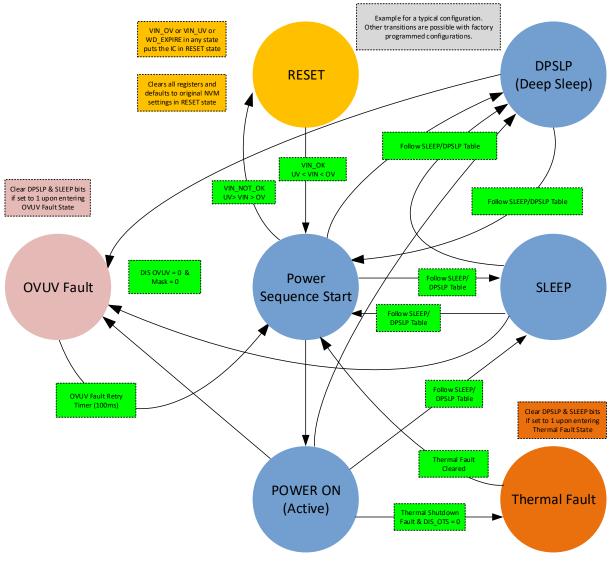

The ACT88321 contains an internal state machine with five internal states.

#### **RESET State**

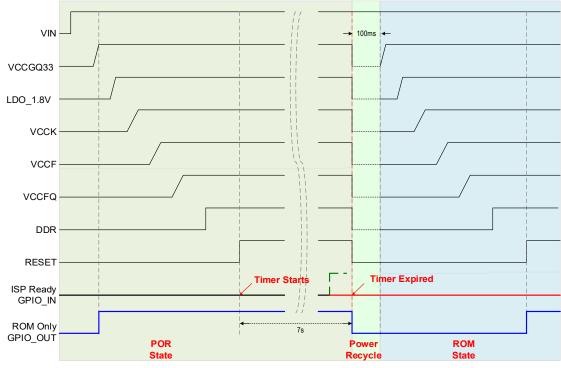

In the RESET, or "cold" state, the ACT88321 is waiting for the input voltage on AVIN to be within a valid range defined by the UVLO and VIN\_OV thresholds. All volatile registers are reset to defaults and Non-Volatile registers are reset to programmed defaults. The IC transitions from RESET to POWER SEQUENCE START when the input voltage enters the valid range. The IC transitions from any other state to RESET if the input voltage drops below the UVLO threshold voltage. It is

## QOULO

important to note any transition to RESET returns all volatile and non-volatile registers to their default states

#### POWER SEQUENCE START State

The POWER SEQUENCE START state is a transitional state while the regulators are starting. The outputs are enabled and are starting up in this state. The IC immediately transitions to the POWER ON or SLEEP states when the regulators go into regulation. The ACT88321 fault mask bits ILIM\_FLTMSK, ILIM\_WARN\_FLTMSK, OV\_FLTMSK and UV\_FLTMSK default to 1 at startup, so if one regulator has a fault at startup, all other regulators will turn on. After a successful power up, these bits are cleared to 0 so that faults are detected. Any faults after this time result in standard hiccup mode functionality.

#### **POWER ON (Active) State**

The ACTIVE state is the normal operating state when the input voltage is within the allowable range, all outputs are turned on, and no faults are present. The IC only enters the ACTIVE State from the POWER SE-QUENCE START State.

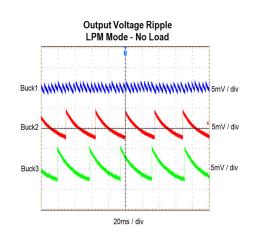

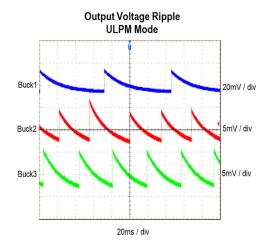

#### **SLEEP State**

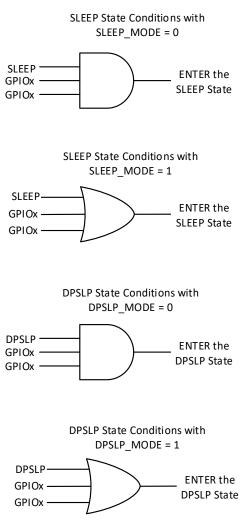

The SLEEP state is a configurable low power state. Based on the system's low power operational requirements, the user can configure the SLEEP state by defining which internal and external regulators are kept on or turned off during the SLEEP state. Each individual regulator output can be programmed to be either on or off in the SLEEP state. Buck2 can also be programmed to regulate to its VSET0 voltage, VSET1 voltage (DVS), or be turned off in the SLEEP state. Note that no other regulators can be programmed to change between VSET0 and VSET1 when the IC enters the SLEEP State. The regulators follow their programmed sequencing delay times when turning on or off as they exit or enter the SLEEP state. The IC can enter SLEEP state via the I<sup>2</sup>C register SLEEP bit or by a GPIO input. Figure 3 shows how the NVM SLEEP MODE factory bit sets the I<sup>2</sup>C and GPIO requirements to enter and exit the SLEEP state.

When the I<sup>2</sup>C bit SLEEP\_MODE = 0, the IC enters SLEEP State with the logical AND of the I<sup>2</sup>C SLEEP bit and the GPIOs. If more than one GPIO is configured as a SLEEP State input, then all the GPIOs must be asserted. If no GPIOs are configured to control the SLEEP State, then only the SLEEP bit controls SLEEP State entry and exit. The IC immediately exits the SLEEP State when the SLEEP bit or a GPIO is de-asserted.

When the I<sup>2</sup>C bit SLEEP\_MODE = 1, the IC enters SLEEP State with the logical OR of the I<sup>2</sup>C SLEEP bit and the GPIOs. If no GPIOs are configured to control the SLEEP state, then only the SLEEP bit controls the SLEEP State. The IC exits SLEEP State when both I<sup>2</sup>C and GPIO are de-asserted.

Figure 3. SLEEP and DPSLP State Truth Tables

#### **DPSLP State**

The DPSLP State is another low power operating mode for the operating system. It is intended to be used in a lower power configuration than the SLEEP state. It is similar with the SLEEP state, but DPSLP uses slightly different configurations to enter and exit this mode. Each output can be programmed to be on or off in the DPSLP state. Buck2 can also be programed to operate

## QOUO