#### Is Now Part of

## ON Semiconductor®

## To learn more about ON Semiconductor, please visit our website at www.onsemi.com

Please note: As part of the Fairchild Semiconductor integration, some of the Fairchild orderable part numbers will need to change in order to meet ON Semiconductor's system requirements. Since the ON Semiconductor product management systems do not have the ability to manage part nomenclature that utilizes an underscore (\_), the underscore (\_) in the Fairchild part numbers will be changed to a dash (-). This document may contain device numbers with an underscore (\_). Please check the ON Semiconductor website to verify the updated device numbers. The most current and up-to-date ordering information can be found at <a href="www.onsemi.com">www.onsemi.com</a>. Please email any questions regarding the system integration to Fairchild <a href="guestions@onsemi.com">guestions@onsemi.com</a>.

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officer

November 2014

# FAN54020 USB-Compliant 1.5 A Single-Cell Li-Ion Switching Charger with DBP and OTG Boost

#### **Features**

- Fully Integrated, High-Efficiency Charger for Single-Cell Li-Ion and Li-Polymer Battery Packs

- Faster Charging / Less Dissipation than Linear Charger

- Charge Voltage Accuracy:

- ±0.5% at 25°C

- ±1% from -30°C to 125°C

- ±10% Charge Current Regulation Accuracy

- 28 V Absolute Maximum Input Voltage

- 1.5 A Maximum Charge Current

- Support for Dead Battery Provision (DBP) of USB Battery Charging Specification 1.2

- Programmable through I<sup>2</sup>C Interface with Fast Mode (400 kHz) Compatibility

- Input Current

- Fast-Charge / Termination Current

- Charger (Float) Voltage

- Safety Timer with Reset Control

- Dynamic Input Voltage Control Automatically Reduces Charging Current with Weak Input Sources

- Low Reverse Leakage Prevents Battery Drain to V<sub>BUS</sub>

- Small Footprint 1µH External Inductor

- 3.3 V Regulated Output from V<sub>BUS</sub> for Auxiliary Circuits

- 5 V, 500 mA Boost Mode for USB OTG for 3.0 to 4.5 V Battery Input

- Attachment Detect Protocol (ADP) Support per On-The-Go and Embedded Host Supplement to the USB Rev. 2.0 Specification

## **Applications**

- Cell Phones. Smart Phones

- Tablet, Portable Media Players

- Gaming Device, Digital Cameras

## Description

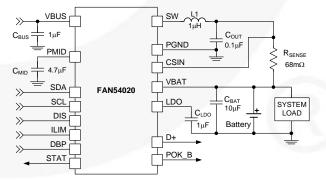

The FAN54020 combines a highly integrated switch-mode charger, to minimize single-cell Li-lon charging time from a USB power source, and a boost regulator to power a USB peripheral from the battery.

The charging parameters and operating modes are programmable through an I2C interface. The charger and boost regulator switch at 3 MHz and utilize the same external components to minimize size.

The FAN54020 supports battery charging in three modes: pre-charge, constant current fast charger, and constant voltage float charge.

To ensure USB compliance and minimize charging time, the input current limit can be changed via I2C by the host processor. Charge termination is determined by a programmable minimum current level. A safety timer with reset control provides a safety back-up for the I2C host. Charge status is reported to the host using the I2C port.

The FAN54020 automatically restarts the charge cycle when the battery falls below an internal threshold. Charge current is reduced when die temperature reaches a programmable level, preventing damage.

The FAN54020 can operate as a boost regulator on command from the system. The boost regulator includes a soft-start that limits inrush current from the battery.

The FAN54020 includes Dead Battery Provision (DBP) from the BC1.2 specification, including a 30 minute timer.

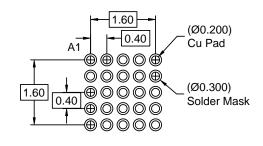

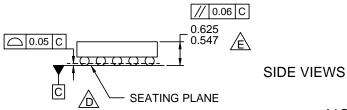

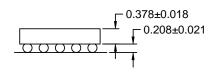

The FAN54020 is available in a 25-bump, 0.4 mm pitch, Wafer-Level Chip-Scale Package (WLCSP).

Figure 1. Typical Application

## **Ordering Information**

| Part Number | PN R0[4:3] | Temperature Range | Package                                                  | Packing Method |

|-------------|------------|-------------------|----------------------------------------------------------|----------------|

| FAN54020UCX | 01         | -40 to 85°C       | 25-Bump, Wafer-Level Chip-Scale<br>(WLCSP), 0.4 mm Pitch | Tape and Reel  |

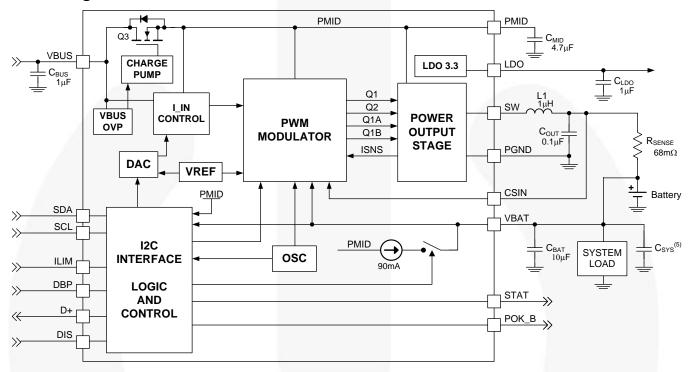

## **Block Diagram**

Figure 2. IC and System Block Diagram

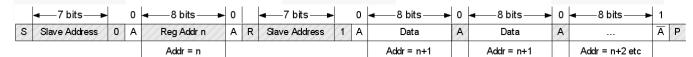

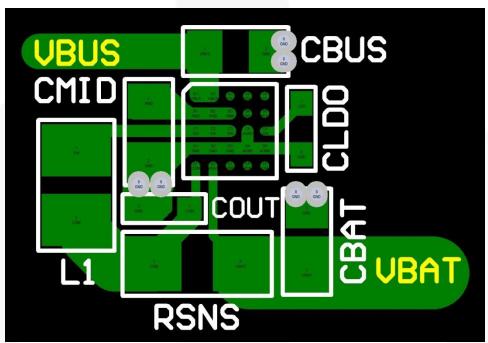

#### Table 1. Recommended External Components

| Component          | Description                           | Vendor                                        | Parameter | Min. | Typ. <sup>(1)</sup> | Unit |

|--------------------|---------------------------------------|-----------------------------------------------|-----------|------|---------------------|------|

|                    | Charge Currents to 1 A:               | Murata: LQM2MPN1R0NG0L                        | L         | 0.5  | 1.0                 | μΗ   |

| L1                 | 1 μH, 30%, 1.3 A, 2016                | Mulata. EQIMZIMFINTRUNGUL                     | DCR       |      | 85                  | mΩ   |

| LI                 | Charge Currents above 1 A:            | Murata: LOMOUDNIADOMOO                        | L         | 0.5  | 1.0                 | μΗ   |

|                    | 1 μH, 20%, 1.6 A, 2520                | Murata: LQM2HPN1R0MG0                         | DCR       |      | 55                  | mΩ   |

| C <sub>BUS</sub>   | 1.0 μF, 10%, 16 V, X5R, 0603          | Murata GRM188R61E105K<br>TDK:C1608X5R1E105K   | С         | 0.5  | 1.0                 | μF   |

| Сват               | 10 μF, 20%, 6.3 V, X5R, 0603          | Murata: GRM188R60J106M<br>TDK: C1608X5R0J106M | С         | 3.7  | 10.0                | μF   |

| Смір               | 4.7 μF, 10%, 10 V, X5R, 0603          | Murata: GRM188R61A475K<br>TDK: C1608X5R1A475K | С         | 2.0  | 4.7                 | μF   |

| C <sub>LDO</sub>   | 1.0 μF, 10%, 6.3 V, X5R, 0402         | Murata GRM155R60J105M                         | С         | 0.35 | 1.00                | μF   |

| C <sub>OUT</sub>   | 0.1 μF, 10%, 6.3 V, X5R, 0201         | Murata GRM033R60J104K                         | С         | 0.07 | 0.10                | μF   |

| R <sub>SENSE</sub> | 68 mΩ, 1%, 0603, $I_{CHG} \le 900$ mA |                                               | R         |      | 68                  | mΩ   |

#### Note:

1. Does not reflect effects of bias, tolerance, and temperature.

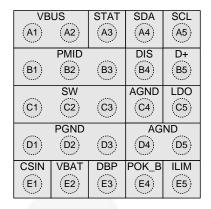

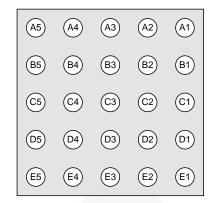

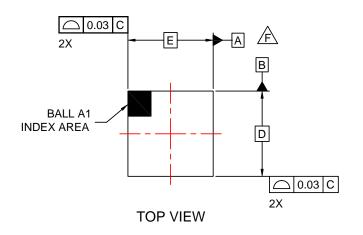

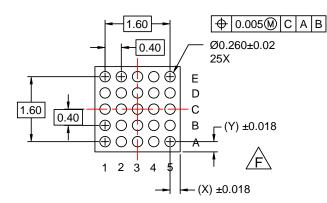

## **Pin Configuration**

**Top View**

**Bottom View**

Figure 4. WLCSP-25 Pin Assignments

## **Pin Definitions**

| Pin #      | Name  | Description                                                                                                                                                                                                                                                                                                                |

|------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1, A2     | VBUS  | Charger Input Voltage. Bypass with a 1 μF capacitor to PGND.                                                                                                                                                                                                                                                               |

| A3         | STAT  | Status/Interrupt. Open-drain output indicating charge status. The IC pulls this pin LOW when charge is in process. It is high impedance when charging is done or the charger is disabled. It is also used as a system interrupt. 128 $\mu$ s pulse, then high impedance indicates to the system that a fault has occurred. |

| A4         | SDA   | I <sup>2</sup> C Interface Serial Data.                                                                                                                                                                                                                                                                                    |

| A5         | SCL   | I <sup>2</sup> C Interface Serial Clock.                                                                                                                                                                                                                                                                                   |

| B1-B3      | PMID  | Power Input Voltage. Power input to the charger regulator, bypass point for the input current sense, and high-voltage input switch. Bypass with a minimum of 4.7 $\mu$ F, 6.3 V capacitor to PGND.                                                                                                                         |

| B4         | DIS   | Disable. When pulled HIGH, the charger is disabled. Internal pull-down resistor.                                                                                                                                                                                                                                           |

| B5         | D+    | Connect to the USB connector D+ pin. Charger IC sources 0.6 V on this pin whenever the IC is charging and the DBP pin is LOW. In all other conditions, the pin is tri-stated.                                                                                                                                              |

| C1-C3      | SW    | Switching Node. Connect to the output inductor.                                                                                                                                                                                                                                                                            |

| C4, D4, D5 | AGND  | Analog Ground. All analog signals are referenced to this pin. This pin can be tied to PGND under the IC.                                                                                                                                                                                                                   |

| C5         | LDO   | 3.3 V LDO. 3.3 V regulator output.                                                                                                                                                                                                                                                                                         |

| D1-D3      | PGND  | Power Ground. Power return for gate drive and power transistors.                                                                                                                                                                                                                                                           |

| E1         | CSIN  | Current-Sense Input. Connect to the sense resistor in series with the battery. The IC uses this node to sense current into the battery. Bypass this pin with a 0.1 $\mu$ F capacitor to PGND.                                                                                                                              |

| E2         | VBAT  | Battery Voltage. Connect to the positive (+) terminal of the battery pack. Bypass with a 10 $\mu$ F capacitor to PGND if the battery is separated from other system bypass capacitance by long traces.                                                                                                                     |

| E3         | DBP   | Dead Battery Provision Disable. Pull HIGH to disable charger D+ output. Internal pull-down resistor.                                                                                                                                                                                                                       |

| E4         | POK_B | $V_{\text{BUS}}$ Power OK Monitor. Open-drain output that is internally pulled LOW when VBUS is greater than the $V_{\text{BUS}}$ validation threshold and lower than $V_{\text{BUS}}$ OVP. It is high impedance when outside this range.                                                                                  |

| E5         | ILIM  | Input Current Limit. This pin sets the input current limit for t <sub>30MIN</sub> charging. Internal pull-down resistor.                                                                                                                                                                                                   |

## **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol                                     |                                          | Parameter                                       |                   |      | Unit |

|--------------------------------------------|------------------------------------------|-------------------------------------------------|-------------------|------|------|

| V <sub>BUS</sub>                           | VBUS Voltage                             |                                                 | -2 <sup>(2)</sup> | 28   | V    |

| VI                                         | PMID, SW Voltage                         |                                                 | -0.3              | 6.5  | V    |

| Vo                                         | Voltage on Other Pins                    |                                                 | -0.3              | (3)  | V    |

| $\frac{\text{dV}_{\text{BUS}}}{\text{dt}}$ | Maximum V <sub>BUS</sub> Slope ab        | ove 5.5 V when Boost or Charger are Active      |                   | 4    | V/μs |

|                                            | E                                        | Human Body Model per JESD22-A114 (All Pins)     | 15                | 500  |      |

| ESD                                        | Electrostatic Discharge Protection Level | Charged Device Model per JESD22-C101 (All Pins) | 50                | 00   | V    |

|                                            | Trotodion Lovor                          | IEC 61000-4-2 System (VBUS and D+ Pin)          | 80                | 000  |      |

| TJ                                         | Junction Temperature                     |                                                 | -40               | +150 | °C   |

| T <sub>STG</sub>                           | Storage Temperature                      |                                                 | -65               | +150 | °C   |

| TL                                         | Lead Soldering Tempera                   | ture, 10 Seconds                                |                   | +260 | °C   |

#### Notes:

- 2. 5 s maximum pulse, non-repetitive, for V<sub>BUS</sub> slew rates faster than -5 V/ms, resulting in -0.7 V>V<sub>BUS</sub>>-2.0 V, applies only for an open battery condition.

- Lesser of 6.5 V or V<sub>BAT</sub> + 0.3 V.

## **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to absolute maximum ratings.

| Symbol            | Parameter                                                      |                                 | Min. | Max. | Unit |

|-------------------|----------------------------------------------------------------|---------------------------------|------|------|------|

| V <sub>BUS</sub>  | Supply Voltage                                                 |                                 | (4)  | 7.5  | V    |

| $V_{BAT(MAX)}$    | Maximum Battery Voltage when Boost enabled                     |                                 |      | 4.5  | V    |

| dV <sub>BUS</sub> | Negative V <sub>BUS</sub> Slew Rate during VBUS Short Circuit, | T <sub>A</sub> ≤ 60°C           |      | 4    | \//a |

| dt                | $C_{MID} \leq 4.7 \mu F$                                       | T <sub>A</sub> <u>&gt;</u> 60°C | 4    | 2    | V/μs |

| T <sub>A</sub>    | Ambient Temperature                                            |                                 | -30  | +85  | °C   |

| TJ                | Junction Temperature (see Thermal Regulation Loop sed          | ction)                          | -30  | +120 | °C   |

#### Note:

4. Greater of V<sub>BAT</sub> or 4 V.

## **Thermal Properties**

Junction-to-ambient thermal resistance is a function of application and board layout. This data is measured with four-layer 2s2p boards in accordance to JEDEC standard JESD51. Special attention must be paid not to exceed junction temperature  $T_{J(max)}$  at a given ambient temperature  $T_A$ . For measured data, see Table 3.

| Symbol            | Parameter                              | Typical | Unit |

|-------------------|----------------------------------------|---------|------|

| $\theta_{\sf JA}$ | Junction-to-Ambient Thermal Resistance | 60      | °C/W |

| θЈВ               | Junction-to-PCB Thermal Resistance     | 20      | °C/W |

## **Electrical Specifications**

Unless otherwise specified: circuit of Figure 2, recommended operating temperature range for  $T_J$  and  $T_A$ ,  $V_{BUS} = 5.0 \text{ V}$ , DIS = 0, (Charger Mode operation); SCL, SDA = 0 or 1.8 V; typical values are for  $T_J = 25$ °C.

| Symbol                  | Parameter                                            | Cond                                                                                                                                                                                                                                       | itions                                               | Min. | Тур. | Max. | Unit     |

|-------------------------|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|------|------|------|----------|

| Power Su                | pplies                                               |                                                                                                                                                                                                                                            |                                                      | l    | 1    | 1    | <u> </u> |

| V <sub>IN(MIN)1</sub>   | V <sub>BUS</sub> Input Voltage Rising                | To Initiate and Pass V <sub>BU</sub>                                                                                                                                                                                                       | S Validation                                         | 4.30 | 4.40 | 4.50 | V        |

| V <sub>IN(MIN)2</sub>   | Minimum V <sub>BUS</sub>                             | While Charging                                                                                                                                                                                                                             |                                                      | 3.60 | 3.70 | 3.80 | V        |

| \/                      | V Dog Loop Throohold                                 | V <sub>BUS_REF</sub> = 01 (Reg2 [3:2                                                                                                                                                                                                       | 2])                                                  | 4.22 | 4.32 | 4.42 | V        |

| V <sub>BUS_REF</sub>    | V <sub>BUS</sub> Reg. Loop Threshold                 | Other V <sub>BUS_REF</sub> Codes (F                                                                                                                                                                                                        | Reg2 [3:2])                                          | -3   |      | +3   | %        |

| t <sub>VBUS_VALID</sub> | V <sub>BUS</sub> Validation Time                     |                                                                                                                                                                                                                                            |                                                      |      | 32   |      | ms       |

|                         |                                                      | V <sub>BUS</sub> > V <sub>BUS_REF</sub> , PWM S                                                                                                                                                                                            | Switching                                            |      | 22   |      |          |

| $I_{VBUS}$              | V <sub>BUS</sub> Current                             | V <sub>BUS</sub> > V <sub>BUS_REF</sub> ; V <sub>BAT</sub> > I <sub>BUS</sub> Setting = 100 mA                                                                                                                                             | V <sub>OREG</sub>                                    |      | 2.0  |      | mA       |

|                         | A**                                                  | 0°C < T <sub>J</sub> < 85°C, HZ_M                                                                                                                                                                                                          | ODE = 1, I <sub>REG</sub> = 0 A                      |      | 188  | 250  | μA       |

| I <sub>BAT</sub>        | Battery Discharge Current in Sleep Mode              | $0^{\circ}\text{C} < \text{T}_{\text{J}} < 85^{\circ}\text{C}, \text{V}_{\text{BAT}} = 4.2 \text{ V}, \text{V}_{\text{BUS}} = \text{Open},$<br>SDA = SCL = DIS = ILIM = DBP = 0  V,<br>$\text{STAT} = \text{POK}\_\text{B} = \text{Float}$ |                                                      |      | 1.7  | 5.0  | μA       |

| I <sub>BUSLKG</sub>     | V <sub>BAT</sub> to V <sub>BUS</sub> Leakage Current | $0^{\circ}\text{C} < \text{T}_{\text{J}} < 85^{\circ}\text{C}, \text{ V}_{\text{BAT}} = 4.2 \text{ V}, \text{ V}_{\text{BUS}} = 0 \text{ V},$ SDA = SCL = DIS = ILIM = DBP = 0 V, STAT = POK B = Float                                     |                                                      |      | 0.01 | 1.00 | μA       |

| Charger V               | oltage Regulation                                    |                                                                                                                                                                                                                                            |                                                      |      |      |      |          |

|                         | Charge Voltage Range                                 |                                                                                                                                                                                                                                            |                                                      | 3.38 |      | 4.44 | V        |

|                         |                                                      | V <sub>OREG</sub> = 4.2 V,                                                                                                                                                                                                                 | T <sub>J</sub> = 25°C                                | -0.5 |      | +0.5 |          |

| \/                      | Charge Valtage Assurage                              | I <sub>BUSLIM</sub> =No Limit                                                                                                                                                                                                              | Temp. Range                                          | -1.0 |      | +1.0 | 0/       |

| $V_{OREG}$              | Charge Voltage Accuracy                              | 2 29 \/ 4 \/                                                                                                                                                                                                                               | T <sub>J</sub> = 25°C                                | -1.0 |      | +1.0 | - %      |

|                         |                                                      | 3.38 V < V <sub>OREG</sub> < 4.44 V                                                                                                                                                                                                        | Temp. Range                                          | -1.5 |      | +1.5 |          |

|                         | VBAT Overshoot <sup>(6)</sup>                        | See Figure 5                                                                                                                                                                                                                               |                                                      |      | 10   | 15   | mV       |

| Fast Char               | ging Current Regulation                              |                                                                                                                                                                                                                                            |                                                      |      |      |      |          |

| 1                       | Output Charge Current Range                          | V <sub>BAT</sub> < V <sub>OREG</sub> , R <sub>SENSE</sub> = 6                                                                                                                                                                              | 68 mΩ                                                | 350  |      | 1500 | mA       |

| I <sub>OCHRG</sub>      |                                                      | Measured as V Across                                                                                                                                                                                                                       | I <sub>OCHARGE</sub> Setting > 500 mA <sub>MAX</sub> | -10  | -5   | 0    | 0/       |

|                         | Charge Current Accuracy                              | R <sub>SENSE</sub> [V <sub>CSIN</sub> – V <sub>BAT</sub> ]                                                                                                                                                                                 | I <sub>OCHARGE</sub> Setting < 500 mA <sub>MAX</sub> | -15  | -7   | 0    | %        |

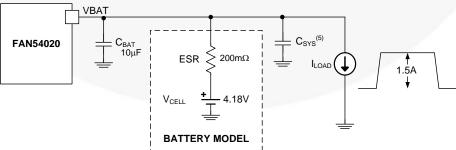

#### **V<sub>BAT</sub> Overshoot Test**

In Figure 5,  $I_{OCHARGE} = 1.5 \, A$  (1100),  $V_{OREG} = 4.2 \, V$ .  $I_{LOAD} t_R = t_F = 1 \, \mu s$ . Charge current prior to load transient =  $\frac{20 m V}{200 m \Omega} = 100 m A$ . Overshoot is measured as the peak voltage above  $V_{BAT}$  level prior to the load transient application.

Figure 5. V<sub>BAT</sub> Overshoot Test Conditions

## **Electrical Specifications**

Unless otherwise specified: circuit of Figure 2, recommended operating temperature range for  $T_J$  and  $T_A$ ,  $V_{BUS} = 5.0 \text{ V}$ , DIS = 0, (Charger Mode operation); SCL, SDA = 0 or 1.8 V; typical values are for  $T_J = 25$ °C.

| Symbol                   | Parameter                              | Conditions                                                                                  | Min. | Тур.     | Max. | Unit |

|--------------------------|----------------------------------------|---------------------------------------------------------------------------------------------|------|----------|------|------|

| Charge Term              | nination Detection                     |                                                                                             |      |          |      | I    |

|                          | Termination Current Range              | $V_{BAT} > V_{OREG} - V_{RCH}, V_{BUS} > V_{BUS\_REF}$<br>R <sub>SENSE</sub> =68 m $\Omega$ | 50   |          | 425  | mA   |

|                          |                                        | [V <sub>CSIN</sub> – V <sub>BAT</sub> ] from 3 mV to 10.2 mV                                | -25  |          | +25  |      |

| I <sub>(TERM)</sub>      | Termination Current Accuracy           | $[V_{CSIN} - V_{BAT}]$ from 10.2 mV to 20.4 mV                                              | -10  |          | +10  | %    |

|                          |                                        | $[V_{CSIN} - V_{BAT}] > 20.4 \text{ mV}$                                                    | -5   |          | +5   |      |

|                          | Termination Current Deglitch Time      | 2 mV Overdrive                                                                              |      | 32       |      | ms   |

| Input Curren             | nt Limit                               |                                                                                             |      |          |      |      |

|                          | Input Current Limit Threshold          | I <sub>BUS</sub> Set to 100 mA                                                              | 87   | 93       | 100  | mA   |

| I <sub>BUSLIM</sub>      | Includes I <sub>LDO</sub>              | I <sub>BUS</sub> Set to 500 mA                                                              | 450  | 475      | 500  | IIIA |

| Logic Levels             | s: DIS, SDA, SCL, ILIM, DBP            |                                                                                             |      |          |      |      |

| V <sub>IH</sub>          | High-Level Input Voltage               |                                                                                             | 1.05 |          |      | V    |

| $V_{IL}$                 | Low-Level Input Voltage                |                                                                                             |      |          | 0.4  | V    |

| I <sub>IN</sub>          | Input Bias Current                     | Input Tied to GND or VBUS                                                                   |      | 0.01     | 1.00 | μА   |

| R <sub>PD</sub>          | ILIM, DBP, DIS Pull-Down<br>Resistance |                                                                                             | 0.65 | 1.00     | 1.40 | ΜΩ   |

| 3.3 V Linear             | Regulator                              |                                                                                             | 10   | l!       |      |      |

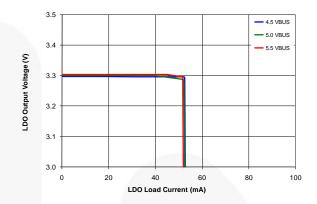

| $V_{LDO}$                | 3.3 V Regulator Output                 | I <sub>LDO</sub> from 0 to 40 mA                                                            | 3.20 | 3.30     | 3.47 | V    |

| I <sub>LDO_IN</sub>      | LDO Quiescent Current                  | V <sub>BAT</sub> = 3.6 V                                                                    |      | 125      |      | μА   |

| V <sub>LDO_IN(MIN)</sub> | LDO Drop-Out Voltage                   | $I_{LDO} = 40 \text{ mA}, V_{BUS} = 0 \text{ V},$<br>$V_{LDO\_IN} = V_{BAT}$                |      | 270      | 330  | mV   |

| t <sub>3.3</sub>         | Regulator Startup Time                 | V <sub>BUS</sub> >V <sub>IN(MIN)1</sub> , DBP=0 or LDO_OFF (Reg2[4]) =1                     |      | 4.5      | 5.0  | ms   |

| Battery Rech             | narge Threshold                        |                                                                                             | - 1  |          |      |      |

| V                        | Recharge Threshold <sup>(6)</sup>      | Below V <sub>OREG</sub>                                                                     | - // | 120      |      | mV   |

| $V_{RCH}$                | Deglitch Time                          | V <sub>BAT</sub> Falling below V <sub>RCH</sub> Threshold                                   | 4    | 132      |      | ms   |

| D+ Output                |                                        |                                                                                             | /    |          |      |      |

| V <sub>DBP_SRC</sub>     | Voltage on D+                          | DBP = 0, $I_{LOAD}$ on D+ from 0 to 250 $\mu$ A                                             | 0.51 | 0.64     | 0.69 | V    |

| I <sub>DBP_OFF</sub>     | Leakage Current                        | DBP = 1, V <sub>D+</sub> from 0 to 5 V                                                      | -1   |          | +1   | μА   |

| STAT and Po              | OK_B Output                            |                                                                                             |      | 1        |      | I    |

| V <sub>STAT(OL)</sub>    | STAT and POK_B Output Low              | I <sub>STAT</sub> = 10 mA                                                                   |      |          | 0.4  | V    |

| I <sub>STAT(OH)</sub>    | STAT and POK_B High Leakage<br>Current | V <sub>STAT</sub> = 5 V                                                                     |      |          | 1    | μА   |

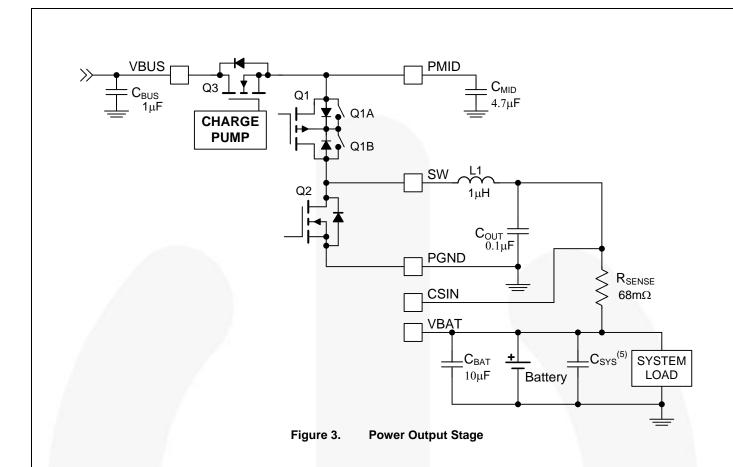

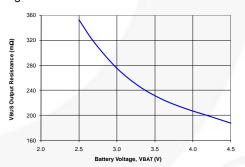

| Power Switc              | hes (see Figure 3)                     |                                                                                             |      | 1        |      |      |

|                          | Q3 On Resistance (VBUS to PMID)        | $I_{IN(LIMIT)} > 500 \text{ mA}$                                                            |      | 160      | 220  |      |

| R <sub>DS(ON)</sub>      | Q1 On Resistance (PMID to SW)          |                                                                                             |      | 110      | 160  | mΩ   |

| TVDS(ON)                 | ,                                      |                                                                                             |      | <b> </b> |      | 1    |

Continued on the following page...

## **Electrical Specifications** (Continued)

Unless otherwise specified: circuit of Figure 2, recommended operating temperature range for  $T_J$  and  $T_A$ ,  $V_{BUS} = 5.0 \text{ V}$ , DIS = 0, (Charger Mode operation); SCL, SDA = 0 or 1.8 V; typical values are for  $T_J = 25$ °C.

| Symbol                  | Parameter                                                   | Conditions                                                                                | Min. | Тур.            | Max. | Unit |

|-------------------------|-------------------------------------------------------------|-------------------------------------------------------------------------------------------|------|-----------------|------|------|

| Charger PW              | M Modulator                                                 |                                                                                           | •    |                 |      |      |

| f <sub>SW</sub>         | Oscillator Frequency                                        |                                                                                           | 2.7  | 3.0             | 3.3  | MHz  |

| D <sub>MAX</sub>        | Maximum Duty Cycle                                          |                                                                                           |      |                 | 100  | %    |

| D <sub>MIN</sub>        | Minimum Duty Cycle                                          |                                                                                           |      | 0               |      | %    |

| I <sub>SYNC</sub>       | Synchronous to Non-Synchronous<br>Current Cut-Off Threshold | Low-Side MOSFET (Q2) Cycle-by-<br>Cycle Current Limit                                     |      | 180             |      | mA   |

| VBUS Load               | Resistance                                                  |                                                                                           |      |                 | II.  |      |

|                         | VIDUO ( DONID D : )                                         | Normal Operation                                                                          | /    | 1500            |      |      |

| $R_{VBUS}$              | VBUS to PGND Resistance                                     | During V <sub>BUS</sub> Validation                                                        |      | 100             |      | Ω    |

| Protection a            | nd Timers                                                   |                                                                                           |      |                 |      | •    |

| VDLIC                   | V <sub>BUS</sub> OVP Accuracy                               | V <sub>BUS</sub> Rising                                                                   | -5   |                 | +5   | %    |

| VBUS <sub>OVP</sub>     | Hysteresis                                                  | V <sub>BUS</sub> Falling                                                                  | \    | 140             |      | mV   |

| \/                      | Battery Short-Circuit Threshold                             | V <sub>BAT</sub> Rising                                                                   | 2.15 | 2.24            | 2.36 | V    |

| V <sub>SHORT</sub>      | Hysteresis                                                  | V <sub>BAT</sub> Falling                                                                  |      | 160             | 11   | mV   |

| .,                      | V <sub>BUS</sub> Voltage above which the I <sub>BUS</sub>   | V <sub>BUS</sub> Rising                                                                   | 5.80 | 6.00            | 6.25 | V    |

| $V_{IBUS(DIS)}$         | Limit is Disabled                                           | V <sub>BUS</sub> Falling                                                                  | 5.50 | 5.75            |      | V    |

| I <sub>SHORT</sub>      | Linear Charging Current                                     | V <sub>BAT</sub> < V <sub>SHORT</sub>                                                     | 80   | 90              | 100  | mA   |

| I <sub>LIMPK(CHG)</sub> | Q1 Cycle-by-Cycle I <sub>PEAK</sub> Limit                   | Charge or PTM Mode                                                                        | 3.3  | 3.8             |      | Α    |

| _                       | Thermal Shutdown Threshold <sup>(6)</sup>                   | T <sub>J</sub> Rising                                                                     |      | 145             |      | °C   |

| T <sub>SHUTDWN</sub>    | Re-Enable Threshold <sup>(6)</sup>                          | T <sub>J</sub> Falling                                                                    |      | T <sub>CF</sub> |      | °C   |

| T <sub>CF</sub>         | Thermal Regulation Accuracy <sup>(6)</sup>                  | Relative to T <sub>CF</sub> Setting                                                       | -10  |                 | +10  | °C   |

|                         | 00 Co and Times                                             | Charger Enabled, Boost Disabled                                                           | 20.5 | 24.3            | 28.0 | S    |

| t <sub>32S</sub>        | 32-Second Timer                                             | Charger Disabled, Boost Enabled                                                           | 17.0 | 24.3            | 31.6 | s    |

| t <sub>30MIN</sub>      | 30-Minute Timer                                             |                                                                                           | 30   | 38              | 45   | Min  |

|                         | latara di Ocalilatara Talarana                              | Charge or ADP Probe                                                                       | -10  |                 | 10   | 0/   |

| t <sub>osc</sub>        | Internal Oscillator Tolerance                               | Boost and ADP_Detect Modes                                                                | -30  |                 | 30   | %    |

| Production 7            | Test Mode                                                   |                                                                                           |      |                 |      |      |

| I <sub>BAT(PTM)</sub>   | Production Test Output Current <sup>(6)</sup>               | 20% Duty with Max. Period 10 ms, $V_{BUS} = 5.5 \text{ V}$ , $V_{OREG} \le 4.2 \text{ V}$ | 2.3  |                 |      | А    |

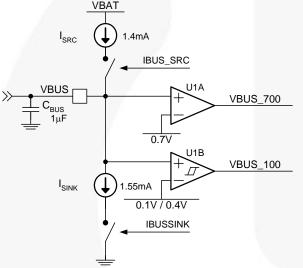

| ADP Circuit             | (see Figure 49)                                             |                                                                                           |      |                 |      |      |

| I <sub>SRC</sub>        | ADP Probe Source Current                                    | V <sub>BUS</sub> ≥ V <sub>700</sub>                                                       | 1.20 | 1.40            | 1.60 | mA   |

| I <sub>SINK</sub>       | ADP Probe Sink Current                                      | $V_{BUS} \ge V_{100}$ , ADP_SNS = 0                                                       | 1.15 | 1.55            | 1.95 | mA   |

| V <sub>100</sub>        | Lower ADP Comparator Threshold                              | ADP_SNS = 0                                                                               | 75   | 100             | 125  | mV   |

| V <sub>700</sub>        | 700 mV ADP Threshold                                        |                                                                                           | 650  | 700             | 750  | mV   |

| $dV_{ADP}$              | V <sub>700</sub> - V <sub>100</sub>                         |                                                                                           | 570  | 600             | 630  | mV   |

|                         |                                                             | V <sub>BUS</sub> Rising                                                                   | 390  | 450             | 510  | ma\/ |

| $V_{SENSE}$             | ADP Sense Threshold,<br>ADP_SNS = 1                         | V <sub>BUS</sub> Falling                                                                  | 230  | 290             | 350  | mV   |

|                         | 7.51 _0110 = 1                                              | Hysteresis                                                                                | 100  | 150             |      |      |

| I <sub>REFRESH</sub>    | Battery Current during Refresh                              |                                                                                           |      | 60              |      | μА   |

| t <sub>REFRESH</sub>    | RDVBUS Set to STAT Pulse                                    |                                                                                           |      |                 | 1    | ms   |

Continued on the following page...

## **Electrical Specifications** (Continued)

Unless otherwise specified: circuit of Figure 2, recommended operating temperature range for  $T_J$  and  $T_A$ ,  $V_{BUS} = 5.0 \text{ V}$ , DIS = 0, (Charger Mode operation); SCL, SDA = 0 or 1.8 V; typical values are for  $T_J = 25$ °C.

| Symbol                  | Parameter                         | Conditions                                                                                | Min. | Тур. | Max. | Unit |  |  |  |  |

|-------------------------|-----------------------------------|-------------------------------------------------------------------------------------------|------|------|------|------|--|--|--|--|

| <b>Boost Mode</b>       | Boost Mode Operation              |                                                                                           |      |      |      |      |  |  |  |  |

| V                       | Popot Output Voltage of VPLIC     | 2.5 V < V <sub>BAT</sub> < 4.5 V,<br>I <sub>LOAD</sub> from 0 to 200 mA                   | 4.80 | 5.07 | 5.17 | V    |  |  |  |  |

| V <sub>BOOST</sub>      | Boost Output Voltage at VBUS      | 3.0 V < V <sub>BAT</sub> < 4.5 V,<br>I <sub>LOAD</sub> from 0 to 500 mA                   | 4.77 | 5.07 | 5.17 | V    |  |  |  |  |

| I <sub>BAT(BOOST)</sub> | Boost Mode Quiescent Current      | PFM Mode, V <sub>BAT</sub> =3.6 V, I <sub>OUT</sub> = 0,<br>LDO On with No Load           |      | 300  | 450  | μА   |  |  |  |  |

| t <sub>REG(BST)</sub>   | Boost Startup Time <sup>(6)</sup> | To within 2% of $V_{BOOST}$ Final Value, $I_{LOAD}$ < 200 mA, $C_{BUS}$ $\leq$ 15 $\mu F$ |      | 0.5  | 2.0  | ms   |  |  |  |  |

| I <sub>LIMPK(BST)</sub> | Q2 Peak Current Limit             |                                                                                           | 1350 | 1550 | 1950 | mA   |  |  |  |  |

| UVLO <sub>BST</sub>     | Minimum Battery Voltage for Boost | While Boost Active                                                                        |      | 2.32 |      | V    |  |  |  |  |

| UVLUBST                 | Operation                         | To Start Boost Regulator                                                                  |      | 2.48 | 2.70 | V    |  |  |  |  |

#### Notes:

- 5.  $C_{BAT}$  is placed as close to the charger IC as possible. An additional 30  $\mu$ F of distributed system capacitance ( $C_{SYS}$ ) is parallel with CBAT, but is located further from the IC.

- 6. Guaranteed by design; not tested in production.

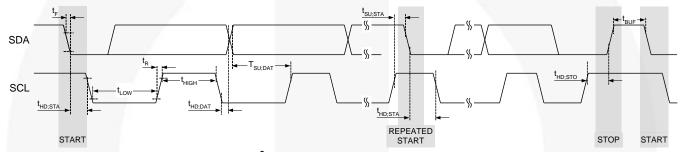

## I<sup>2</sup>C Timing Specifications

Guaranteed by design.

| Symbol              | Parameter                         | Conditions                               | Min. | Тур.              | Max. | Uni |  |

|---------------------|-----------------------------------|------------------------------------------|------|-------------------|------|-----|--|

|                     |                                   | Standard Mode                            |      |                   | 100  |     |  |

|                     | COL Objets Francisco              | Fast Mode                                |      |                   | 400  |     |  |

| f <sub>SCL</sub>    | SCL Clock Frequency               | High-Speed Mode, C <sub>B</sub> ≤ 100 pF |      |                   | 3400 | kHz |  |

|                     |                                   | High-Speed Mode, C <sub>B</sub> ≤ 400 pF |      |                   | 1700 |     |  |

|                     | Bus-Free Time between STOP and    | Standard Mode                            |      | 4.7               |      |     |  |

| t <sub>BUF</sub>    | START Conditions                  | Fast Mode                                |      | 1.3               |      | μS  |  |

|                     |                                   | Standard Mode                            |      | 4                 |      | μS  |  |

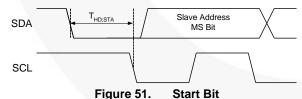

| t <sub>HD;STA</sub> | START or Repeated START Hold Time | Fast Mode                                |      | 600               |      | -   |  |

|                     |                                   | High-Speed Mode                          |      | 160               |      | ns  |  |

|                     |                                   | Standard Mode                            |      | 4.7               |      |     |  |

|                     |                                   | Fast Mode                                |      | 1.3               |      | μS  |  |

| $t_{LOW}$           | SCL LOW Period                    | High-Speed Mode, C <sub>B</sub> ≤ 100 pF |      | 160               |      |     |  |

|                     |                                   | High-Speed Mode, C <sub>B</sub> ≤ 400 pF |      | 320               |      | ns  |  |

|                     |                                   | Standard Mode                            |      | 4                 |      | μS  |  |

|                     | SCL HIGH Period                   | Fast Mode                                |      | 600               |      | , , |  |

| t <sub>HIGH</sub>   |                                   | High-Speed Mode, C <sub>B</sub> ≤ 100 pF |      | 60                |      | ns  |  |

|                     |                                   | High-Speed Mode, C <sub>B</sub> ≤ 400 pF |      | 120               |      |     |  |

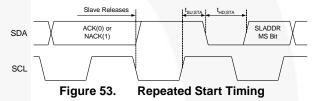

|                     |                                   | Standard Mode                            |      | 4.7               |      | με  |  |

| t <sub>SU:STA</sub> | Repeated START Setup Time         | Fast Mode                                |      | 600               |      | pro |  |

| -00,0171            |                                   | High-Speed Mode                          |      | 160               |      | ns  |  |

|                     |                                   | Standard Mode                            |      | 250               |      |     |  |

| t <sub>SU:DAT</sub> | Data Setup Time                   | Fast Mode                                |      | 100               |      | ns  |  |

| 00,5/11             |                                   | High-Speed Mode                          |      | 10                |      |     |  |

|                     |                                   | Standard Mode                            | 0    |                   | 3.45 | μS  |  |

|                     |                                   | Fast Mode                                | 0    |                   | 900  | μο  |  |

| t <sub>HD;DAT</sub> | Data Hold Time                    | High-Speed Mode, C <sub>B</sub> ≤ 100 pF | 0    |                   | 70   | ns  |  |

|                     |                                   | High-Speed Mode, C <sub>B</sub> ≤ 400 pF | 0    |                   | 150  |     |  |

|                     |                                   | Standard Mode                            |      | ).1C <sub>B</sub> | 1000 |     |  |

|                     |                                   | Fast Mode                                |      | ).1C <sub>B</sub> | 300  |     |  |

| $t_{RCL}$           | SCL Rise Time                     | High-Speed Mode, C <sub>B</sub> ≤ 100 pF |      | 10                | 80   | ns  |  |

|                     |                                   | High-Speed Mode, C <sub>B</sub> ≤ 400 pF |      | 20                | 160  |     |  |

|                     |                                   | Standard Mode                            | 20+0 | ).1C <sub>B</sub> | 300  |     |  |

|                     |                                   | Fast Mode                                |      | ).1C <sub>B</sub> | 300  |     |  |

| $t_{FCL}$           | SCL Fall Time                     | High-Speed Mode, C <sub>B</sub> ≤ 100 pF |      | 10                | 40   | ns  |  |

|                     |                                   | High-Speed Mode, C <sub>B</sub> ≤ 400 pF |      | 20                | 80   |     |  |

|                     |                                   | Standard Mode                            | 20+0 | ).1C <sub>B</sub> | 1000 |     |  |

| t <sub>RDA</sub>    | SDA Rise Time                     | Fast Mode                                |      | ).1C <sub>B</sub> | 300  |     |  |

| t <sub>RCL1</sub>   | Rise Time of SCL after a Repeated | High-Speed Mode, C <sub>B</sub> ≤ 100 pF |      | 10                | 80   | ns  |  |

|                     | START Condition and after ACK Bit | High-Speed Mode, C <sub>B</sub> ≤ 400 pF |      | 20                | 160  |     |  |

Continued on the following page...

## I<sup>2</sup>C Timing Specifications

Guaranteed by design.

| Symbol              | Parameter                    | Conditions                               | Min. | Тур.              | Max. | Unit |

|---------------------|------------------------------|------------------------------------------|------|-------------------|------|------|

|                     |                              | Standard Mode                            | 20+0 | ).1C <sub>B</sub> | 300  |      |

|                     | CDA Fall Time                | Fast Mode                                | 20+0 | ).1C <sub>B</sub> | 300  | 1    |

| t <sub>FDA</sub>    | SDA Fall Time                | High-Speed Mode, C <sub>B</sub> ≤ 100 pF |      | 10                | 80   | ns   |

|                     |                              | High-Speed Mode, C <sub>B</sub> ≤ 400 pF |      | 20                | 160  |      |

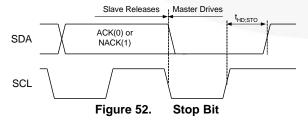

|                     |                              | Standard Mode                            |      | 4                 |      | μS   |

| t <sub>SU;STO</sub> | Stop Condition Setup Time    | Fast Mode                                |      | 600               |      |      |

|                     |                              | High-Speed Mode                          |      | 160               |      | ns   |

| Св                  | Capacitive Load for SDA, SCL |                                          |      |                   | 400  | pF   |

## **Timing Diagrams**

Figure 6. I<sup>2</sup>C Interface Timing for Fast and Slow Modes

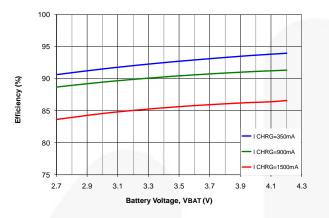

85 80 - 4.5 VBUS - 5.0 VBUS - 5.5 VBUS - 6.5 VBUS - 6.5 VBUS - 6.5 VBUS - 6.5 VBUS

Figure 7. Efficiency vs. Battery Voltage Over-I<sub>CHRG</sub> Range

Figure 8. Efficiency vs. I<sub>CHRG</sub> Over-V<sub>BUS</sub> Range

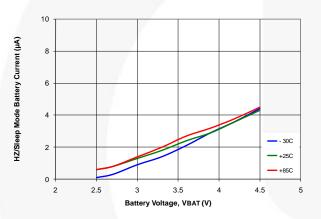

Figure 9. HZ/Sleep Mode Battery Discharge Current, SDA=SCL=1.8 V, DIS=DBP=0

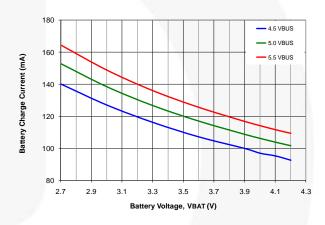

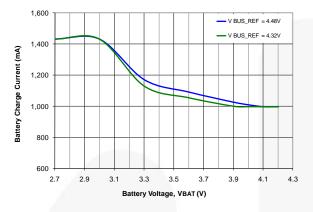

Figure 10. Charge Current vs. Battery Voltage, IBUSLIM=100 mA

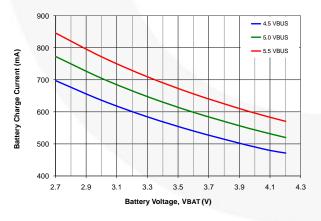

Figure 11. Charge Current vs. Battery Voltage, IBUSLIM=500 mA

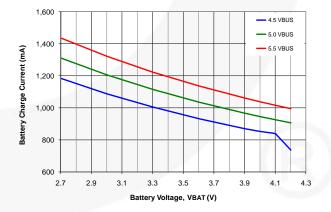

Figure 12. Charge Current vs. Battery Voltage, IBUSLIM=900 mA

Figure 13. Charge Current vs. Battery Voltage, 5.2 V<sub>BUS</sub>, 1 A Source Limited

2 V<sub>BUS</sub>, Figure 14. LDO Regulation vs. Load Over-V<sub>BUS</sub> Range,

4.2 V<sub>BAT</sub>

Tek Stop

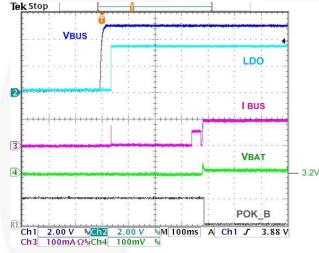

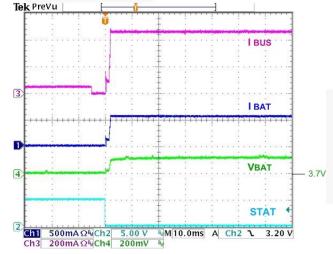

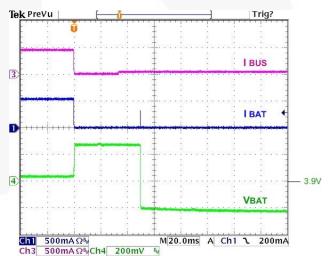

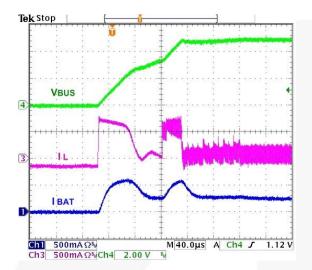

Figure 15. Charger Startup at  $V_{BUS}$  Plug-In, 3.2  $V_{BAT}$ , ILIM=DBP=0, 1 k $\Omega$  LDO Load

Figure 16. Charger Startup at  $V_{BUS}$  Plug-In, 3.2  $V_{BAT}$ , ILIM=1, DBP=0, 1 k $\Omega$  LDO Load

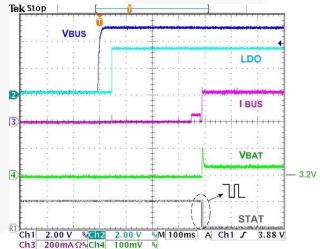

Figure 17. Charger Startup at HZ Bit Reset, 3.7  $V_{BAT}$ , ILIM=DBP=1, 1  $k\Omega$  LDO Load,  $I_{CHRG}$ =1.0 A

Figure 18. Charger Startup at V<sub>BUS</sub> Plug-In, Dead Battery, ILIM=DBP=0, 1 kΩ LDO Load

Figure 19. Charger Startup at  $V_{BUS}$  Plug-In, No Battery, ILIM=DBP=0, 300  $\Omega$  LDO Load

Figure 20.  $V_{BUS}$  OVP Response while Charging, 5-9-5  $V_{BUS}$ , 3.7  $V_{BAT}$ ,  $I_{BUSLIM}$ =500 mA,  $I_{CHRG}$ =1.0 A

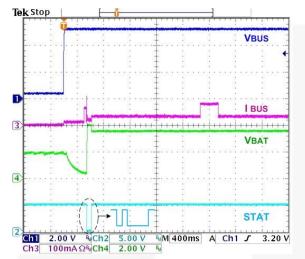

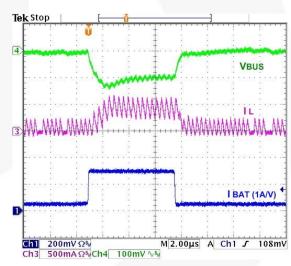

Figure 21. Battery Removal/Insertion while Charging, TE\_DIS=1, 3.7  $V_{BAT}$ , 1  $k\Omega$  LDO Load,  $I_{BUSLIM}$ =500 mA,  $I_{CHRG}$ =1.0 A

Figure 22. Battery Removal/Insertion while Charging, TE\_DIS=0, 3.7 VBAT, 1 k $\Omega$  LDO Load, IBUSLIM=500 mA, ICHRG=1.0 A

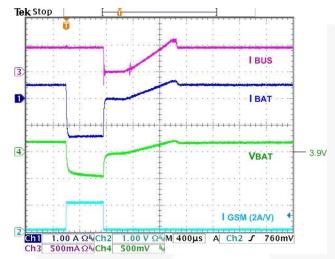

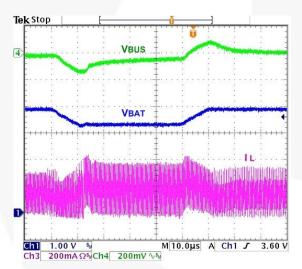

Figure 23. GSM Pulse (2 A Step,  $t_R/t_F$ =5  $\mu$ s) Response, 3.9  $V_{BAT}$ , 1  $k\Omega$  LDO Load,  $I_{BUSLIM}$ =500 mA,  $I_{CHRG}$ =1.0 A

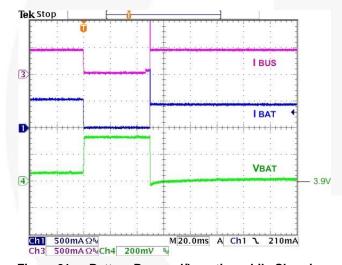

Figure 24. GSM Pulse (2 A Step,  $t_R/t_F=5~\mu s$ ) Response, 3.9  $V_{BAT}$ , 1  $k\Omega$  LDO Load,  $I_{BUSLIM}=No$  Limit,  $I_{CHRG}=1.0$  A, 500 mA  $V_{BUS}$  Source Limited

## **Boost Mode Typical Characteristics**

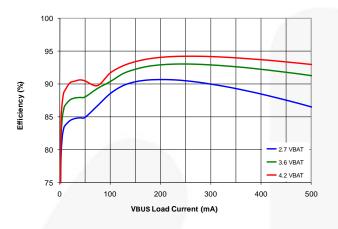

Unless otherwise specified, using circuit of Figure 2 V<sub>BAT</sub>=3.6 V, DIS=0, SCL=SDA=1.8 V, LDO no load, T<sub>A</sub>=25°C.

- 4.2 VBAT

500

400

90 Efficiency (%) 85 - 30C 80 + 25C + 85C 75 100 200 300 500 400 **VBUS Load Current (mA)**

Figure 25. **Efficiency vs. Load Current Over-Input** Voltage (V<sub>BAT</sub>) Range

2.7 VBAT 3.6 VBAT 5.10

Figure 26. Efficiency vs. Load Current Over-Temperature Range, 3.6 V<sub>BAT</sub>

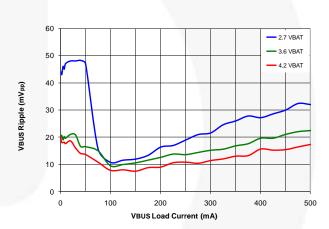

Figure 27. **Output Regulation vs. Load Current** Over- Input Voltage (VBAT) Range

200 VBUS Load Current (mA)

300

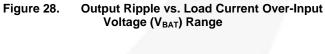

Figure 29. **OTG / Boost Quiescent Current vs. Input** Voltage (V<sub>BAT</sub>) Over-Temperature

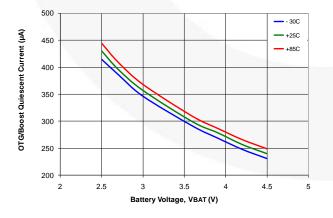

**OTG / Boost DC Load Current Limit** Figure 30. Threshold vs. Input Voltage (VBAT) Over-Temperature

VBUS Output Voltage (V)

5.05

5.00

4.95

4 90

4.85

100

## **Boost Mode Typical Characteristics**

Unless otherwise specified, using circuit of Figure 2 V<sub>BAT</sub>=3.6 V, DIS=0, SCL=SDA=1.8 V, LDO no load, T<sub>A</sub>=25°C.

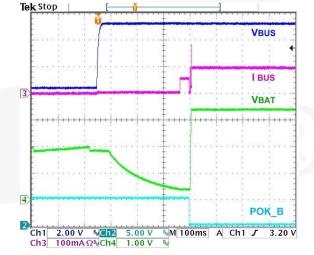

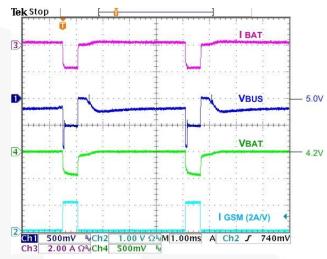

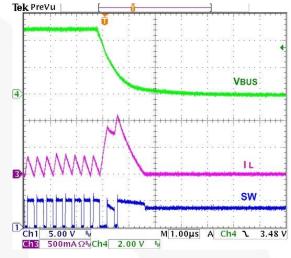

Figure 31. Startup, 50  $\Omega$  Load, Additional 10  $\mu$ F on  $V_{BUS}$

Figure 32.  $V_{\text{BUS}}$  Output Fault Response

Figure 33. Line Transient Response, 50  $\Omega$  Load, 3.9-3.3-3.9  $V_{BAT}$ ,  $t_R/t_F$ =10  $\mu s$

Figure 34. Load Transient Response, 50-300-50 mA,  $t_{\rm R}/t_{\rm F}$ =100 ns

## **Operation and Applications Description**

The FAN54020 is a USB-compliant single-cell Li-lon switching charger with support for dead battery provision (DBP) within the BC1.2 specification, including a 30-minute timer that cannot exceed 45 minutes. The maximum charge current is rated at 1.5 A. The FAN54020 is designed to be stable with space-saving ceramic capacitors.

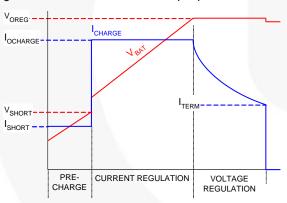

#### **Charging Stages**

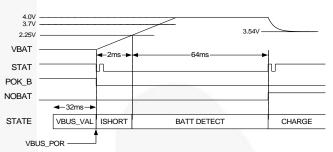

Figure 35 shows the different stages of Li+ charging when a charger is connected to the USB pins and a battery is present and discharged below 2.25 V. Generally, the pregualification (called "PRE-CHARGE" in Figure 35) stage is when the battery voltage is below 2.25 V when an I<sub>SHORT</sub> current of 90 mA charges the battery to V<sub>SHORT</sub> voltage of 2.25 V. Then Fast Charge starts if a battery is detected and the current is increased considerably to a programmable IOCHARGE level ("CURRENT REGULATION" in the figure). The battery voltage climbs quickly based on the drop caused by the current across the load elements of the battery. Then the voltage climbs linearly until the constant voltage stage is reached at the programmable voltage of V<sub>OREG</sub>. The current is monitored during this stage ("VOLTAGE REGULATION" in the figure) and, when it reaches the end of current ITERM, charging stops.

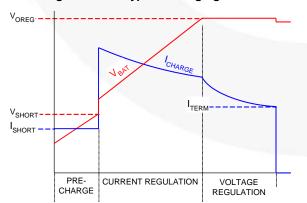

Figure 36 shows the charge stages using a switching charger when the input power of the charging source is limited by the IC. During current regulation, as  $V_{BAT}$  rises, charge current decreases because input power is limited.

Figure 35. Typical Charging Profile

Figure 36. Charge Curve, I<sub>INLIM</sub> Limits I<sub>CHARGE</sub>

#### **VBUS CON**

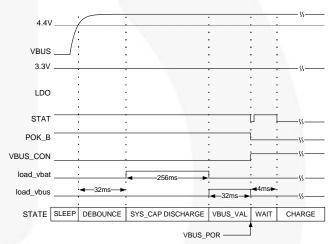

The VBUS\_CON bit is set after  $V_{\text{BUS}}$  rises above  $V_{\text{BAT}}$  and  $V_{\text{INMIN1}} \left(4.4 \text{ V}\right)^{(7)}\!.$

As soon as V<sub>BUS</sub> falls below either V<sub>IN(MIN)2</sub> (3.7 V) or V<sub>BAT</sub>, the IC turns off the charger and applies 50 mA to VBUS for 66 ms. If V<sub>BUS</sub> is below V<sub>BAT</sub> or 3.7 V at the end of this period, VBUS\_CON is reset.

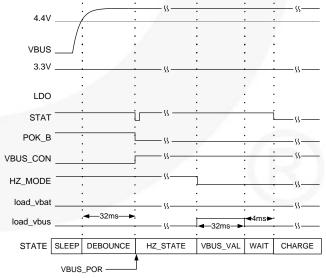

The STAT pin pulses whenever the VBUS\_CON bit changes from HIGH to LOW. For VBUS\_CON LOW to HIGH, the STAT pulse occurs per timing in Figure 37 or Figure 38, depending on whether or not charge or HZ state is entered after VBUS is connected.

#### Note:

If V<sub>BUS</sub> is above V<sub>INMIN2</sub> (3.7 V), but below V<sub>INMIN1</sub> (4.4 V); VBUS\_CON is set for 132 ms. POK\_B also pulses LOW for 132 ms.

Figure 37. VBUS Plug-in Timing: Battery Present, DBP=1, DIS = 0, HZ\_MODE = 0

Figure 38. VBUS Plug-in Timing from HZ\_MODE: Battery Present, DBP = 1

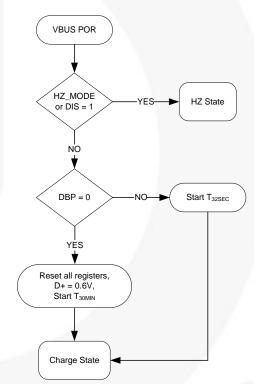

#### **VBUS POR and DBP** (see Figure 37)

When the IC detects that V<sub>BUS</sub> has risen above V<sub>IN(MIN)1</sub> (4.4 V), Q3's charge pump turns on. If V<sub>BUS</sub> remains above this threshold for 16 ms, the IC then applies a 1 mA load to VBAT for 256 ms to ensure that, if the battery was removed or its discharge protection switch is open, the system capacitors across VBAT will be discharged below the V<sub>SHORT</sub> threshold.

$V_{BUS}$  validation is then performed to ensure a valid charging source. Validation occurs with a 50 mA load on VBUS. To pass validation,  $V_{BUS}$  must remain above  $V_{\text{IN}(MIN)^1}$  and below  $V_{\text{BUSOVP}}$  for  $t_{\text{VBUS\_VALID}}$  (32 ms) before the IC initiates charging. If  $V_{BUS}$  fails validation; the load is removed, the VALIDATION FAIL bit is set, and validation is attempted every two seconds.

Once  $V_{BUS}$  is validated; VBUS\_CON (Reg7[7]) is set, POK\_B pulls low, and the STAT pin pulses to indicate to the system that VBUS is connected. This point is considered to be VBUS\_POR.

If  $V_{BUS}$  fails validation, the POK\_B pin and bit (Reg7[6]) are raised and the STAT pin pulsed to indicate a  $V_{BUS}$  fault.  $V_{BUS}$  validation is subsequently re-tried every two seconds. Setting HZ\_MODE or DIS prevents periodic re-validation.  $V_{BUS}$  validation is also performed prior to entering CHARGE state from any state where the charger is off.

At VBUS POR, the IC operates in accordance with its  $I^2C$  register settings as long as the DBP pin is HIGH. If the DBP pin is LOW, the IC sets all registers to their default values and the  $I_{BUS}$  current is controlled by the ILIM pin, with  $I_{BUS}(MAX) = 100$  mA when ILIM is LOW and  $I_{BUS}(MAX) = 500$  mA when ILIM is HIGH. Once DBP returns HIGH, D+ is tri-stated and charge parameters may be programmed by the host.  $I_{BUS}(MAX)$  remains controlled by the state of the ILIM pin until the first  $I^2C$  write occurs; at which time,  $I_{BUS}(MAX)$  is controlled by the  $I_{BUS}$  register bits (Reg5). The first  $I^2C$  write after DBP rises stops the  $I_{30MIN}$  timer and starts the 32-second timer ( $I_{32S}$ ).

BC1.2 and USB 2.0 allow a portable device (defined as a device with a battery) with a dead battery to take a maximum of 100 mA from the USB VBUS line for a maximum of 45 minutes as long as the portable device forces the D+ line to 0.6 V typical.

If the DBP pin is LOW at VBUS POR or transitions from HIGH to LOW when VBUS is valid, the FAN54020:

- 1. Resets its registers to default values;

- 2. Starts the t<sub>30MIN</sub> timer;

- Charges with its input current limit set by the state of the ILIM pin as described above; and

- 4. Sources 0.6 V to the D+ pin.

Both ILIM and DBP are internally pulled down and there is typically nothing to force them HIGH at this point due to the processor/system not being awake. When  $t_{30\text{MIN}}$  expires, the FAN54020 removes the 0.6 V from D+ and stops charging. The D+ pin is also tri-stated when DBP is HIGH.

After a  $t_{30\text{MIN}}$  timer expiration, charging may only be restarted after a new VBUS POR.

#### LDO

The FAN54020 contains a 3.3 V LDO available to provide power to the USB PHY. By default, the LDO is enabled and biased from VBAT when DBP is HIGH and  $V_{BUS} < V_{BAT}$ . When  $V_{BUS} > V_{BAT}$ , the LDO is biased from VBUS. If DBP is LOW, the LDO is only biased from VBUS and off when  $V_{BUS} < V_{IN(MIN)1}$ . When the LDO\_OFF bit (Reg02[4]) is raised, the LDO is biased from VBUS and off when  $V_{BUS} < V_{IN(MIN)1}$ .

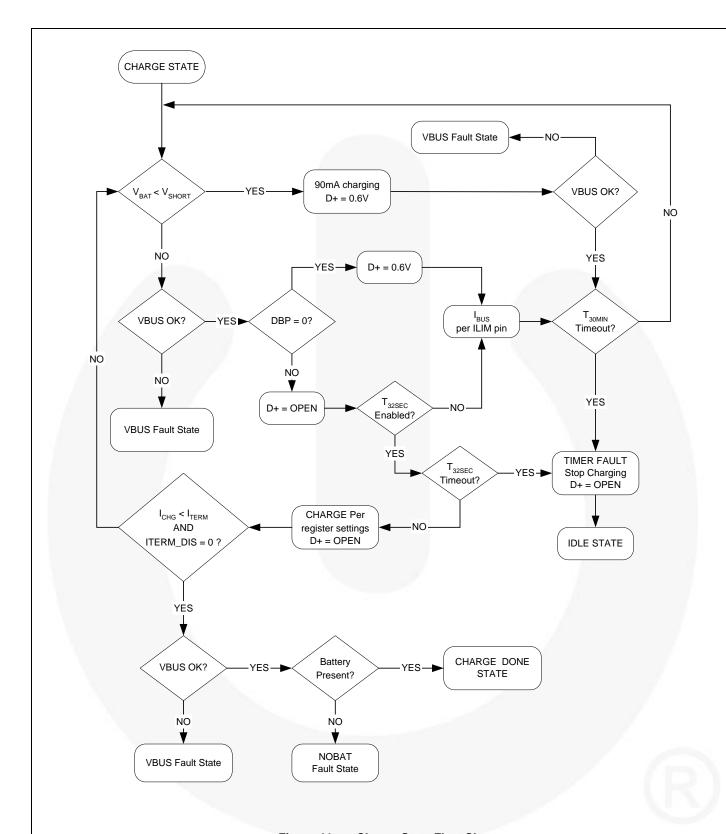

#### **Pre-Charging Stage**

A typical battery has a protection circuit within the battery pack to prevent further discharge if its cell voltage falls below 2.25 V. This causes  $V_{BAT}$  to decay quickly to ground since all that is holding  $V_{BAT}$  up is the external decoupling capacitors. Another way  $V_{BAT}$  can get so low is if VBAT is shorted to ground accidentally. Both are very rare in a typical system because a dead battery is typically above 3 V and only goes below 3 V via leakage over a long period of time.

When  $V_{BUS} > V_{BAT}$ , the IC takes its power from VBUS while monitoring VBAT to determine the optimal charging profile.

If  $V_{BAT}$  is below 2.25 V, a charging current of 90 mA is used to trickle charge the battery. If it is not a short circuit,  $V_{BAT}$  should recover very quickly above 2.25 V since it is only charging decoupling capacitors. If there is a short circuit, the timer continues up to 30 minutes and expires, shutting down the charger. This limits the short-circuit current of 90 mA to be drawn only for 30 minutes. The only way to recover from this fault is to remove the short circuit. If the short circuit is not removed, detaching and re-attaching the charger restarts the dead battery provision timer for another 30 minutes before shutting off again.

#### **Battery Absent / Present Response**

The FAN54020 detects if the battery is absent if  $V_{BAT}$  is below 2.25 V at the start of charging. To accomplish this, the IC raises  $V_{OREG}$  to 4.0 V for up to 128 ms after  $V_{BAT}$  is above 2.25 V. After 64 ms,  $V_{BAT}$  is compared to 3.7 V. If  $V_{BAT}$  rises above 3.7 V at any time in that 64 ms period, the battery is assumed to be absent (see Figure 39).

If battery absence is detected; all registers are reset, the NOBAT bit is set, an interrupt generated, and  $V_{\text{OREG}}$  reverts to its default value of 3.54 V. The charger continues to provide power to the system with STAT HIGH in DBP Mode until otherwise instructed through  $l^2 C$  commands. This allows the host processor an opportunity to detect charger type and negotiate with the USB host for higher current.

The IC continues to provide current, provided that:

- 1. A timer (T<sub>30MIN</sub> or T<sub>32S</sub>) is running; and

- 2.  $HZ_MODE = 0$  and DIS = 0.

The current drawn from VBUS is determined by the state of the ILIM pin and the  $I_{\text{OCHARGE}}$  settings.

Once the initial battery absence test is performed, the only other battery absent test performed occurs if ITERM\_DIS = 0 and the charge current drops below the ITERM setting.

#### **Constant Current / Constant Voltage Charging**

In this stage,  $V_{BAT}$  is above the pre-qualification voltage of 2.25 V, but below  $V_{OREG}$ . At a certain  $V_{BAT}$  level, the system begins a low-level software boot sequence and uses the USB PHY to determine if a Dedicated Charging Port (DCP), Charging Downstream Port (CDP), or a typical PC host (a Standard Downstream Port (SDP)) is connected. The result of the interrogation determines how much current the FAN54020 can draw and remain USB compliant.

For SDP and CDP, enumeration is required. After enumeration, the system can raise the ILIM pin to increase charge current to 500 mA or the host can use the  $I^2$ C bus to program the charge current via the  $I_{OCHARGE}$  bits in IBAT (REG3[7:4]).

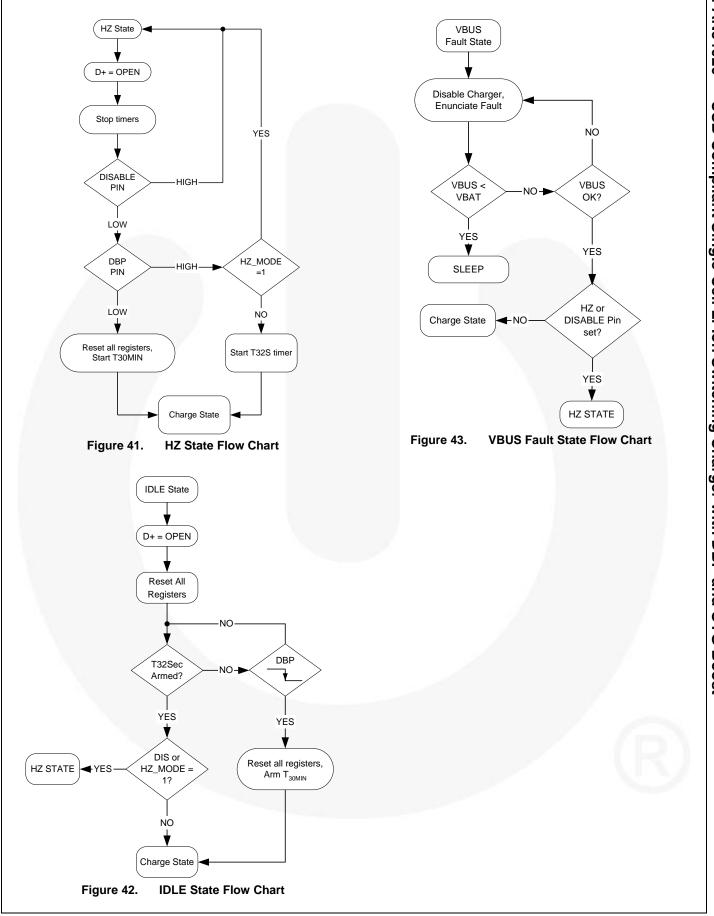

After DBP transitions from LOW to HIGH, writing to any register through I<sup>2</sup>C stops and resets the t<sub>30MIN</sub> timer, which in turn enables the 32-second timer (t<sub>32S</sub>). As long as t<sub>32S</sub> is enabled, charge current is controlled by I<sup>2</sup>C register settings.

If the  $t_{32S}$  timer subsequently expires, charging stops and the IC enters IDLE state (see Figure 42). To continue charging when  $t_{32S}$  is enabled, the host must reset the  $t_{32S}$  timer by periodically setting the TMR\_RST bit (Reg0A[7]). Once the IDLE state is entered; charging can resume only after VBUS is disconnected and reconnected, the DBP pin is lowered, or a new I $^2$ C write starts the  $t_{32S}$  timer.

The constant voltage,  $V_{OREG}$ , threshold is also expected to be set based on battery type and battery temperature, which should be monitored by the processor via separate controls. Thermal regulation within the FAN54020 may have little correlation to the battery temperature since the heat dissipation of the PCB that the FAN54020 is soldered to may be completely different from the heat dissipation within the battery pack.

#### **Charge Termination and Recharge**

When  $V_{BAT}$  reaches  $V_{OREG}$  (Reg4[5:0]), the current charging the battery is reduced, limited by the battery's ESR and its internal cell voltage. Charging continues until the  $I_{BAT} < I_{TERM}$  (set by Reg3[3:0] bits) threshold is crossed. If ITERM\_DIS = 0, charging stops (charge termination), and  $t_{32S}$  stops.

After charge termination, a small load is placed across VBAT for 132 ms. The battery is presumed absent if  $V_{BAT}$  stays below  $V_{RCH}$  (140 mV below  $V_{OREG}$ ) for the next 132 ms. The NOBAT bit is then set and the NOBAT Fault state is entered (see *Figure 46*). The charger restarts after two seconds and:

If V<sub>BAT</sub> < V<sub>SHORT</sub>, a battery absent/present test described in Figure 39 is performed;

#### OR

2. If  $V_{BAT} > V_{SHORT}$ , PWM charging resumes.

The NOBAT bit is reset only if one of the battery absent / present tests is performed with battery presence detected or after a VBUS POR with the battery present.

If  $V_{BAT}$  falls to 140 mV below  $V_{OREG}$ , the Fast Charge charging cycle starts again, if  $VRCH_DIS = 0$ . A recharge condition debounce time of 132 ms is used to prevent transient battery load currents (such as GSM current pulses) from triggering recharge unnecessarily.

Figure 39. Battery Absent After VBUS POR

Figure 40. VBUS\_POR Flow Chart

Figure 44. Charge State Flow Chart

#### Note:

8. If HZ\_MODE is set, or DIS = 1, Charge State exits to HZ State.

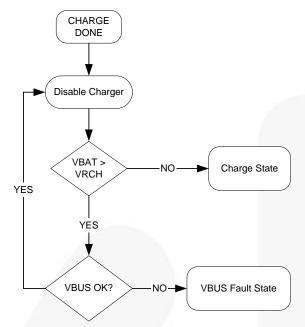

Figure 45. Charge Done State Flow Chart

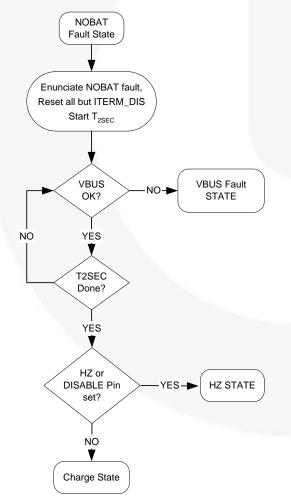

Figure 46. NOBAT Fault State Flow Chart

#### **Production Test Mode**

Production Test Mode (PTM) provides power for the system from the USB port.

PTM is enabled when the PTM\_EN bit is HIGH and the battery is absent (NOBAT = 1). Only the OREG loop is active and  $V_{OREG}$  must be programmed by the user. The 32second timer ( $T_{32S}$ ) is stooped during PTM.

During PTM, high-current pulses (load currents greater than 1.5 A) must be limited to 20% duty cycle with a minimum period of 10 ms. A 50 mA minimum DC load is required.

#### **STAT Pin and Interrupts**

The STAT pin is used to indicate charging status, as well as to signal the host processor of a change in the status of the IC or system. The STAT pin emits a 125  $\mu$ s low-going pulse whenever an unmasked interrupt event occurs (see Reg6 – Reg7). The static state of the STAT pin is determined by whether the IC is charging a battery:

Table 2. STAT Pin Static State

| CHARGER | NOBAT Bit | STAT Pin |  |  |

|---------|-----------|----------|--|--|

| ON      | 0         | 0        |  |  |

| OFF     | X         | 1        |  |  |

| Х       | 1         | 1        |  |  |

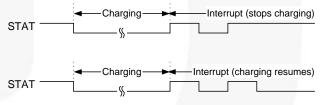

Any interrupt pulse that occurs while STAT was statically LOW is preceded by a 125  $\mu s$  STAT HIGH pulse, as shown in Figure 47.

Figure 47. STAT Interrupt Pulse Behavior

If the condition causing the interrupt also causes the charger to stop charging (for example, a Timer fault (TC\_TO)), STAT remains HIGH after the 125  $\mu s$  low-going pulse. If charging continues after the interrupt (as with TREG\_FLAG interrupt), STAT goes HIGH for 125  $\mu s$  after the 125  $\mu s$  low-going pulse, then returns LOW.

When bits in the INTERRUPT or STATUS register are set, if the corresponding MASK bit is reset, the INTERRUPT bit (Reg1[0]) is set before the falling edge of STAT, which enunciates the interrupt. The INTERRUPT bit is cleared when the host reads Reg1. For an interrupt to be enunciated by the STAT pin, the following conditions must ALL be true:

- An interrupt condition occurs, which sets an interrupt bit in INTERRUPT or STATUS registers; and

- 2. The corresponding mask bit = 0; and

- 3. The INTERRUPT bit (Reg1[0]) = 0.

If additional interrupt conditions occur before the host clears the INTERRUPT bit by reading Reg1, the STAT pin does not pulse.

#### OVP and VBUS\_IN Regulation

The FAN54020 contains programmable over-voltage protection (OVP) on VBUS, ranging from 6.5 V to 8.0 V, as specified in the  $V_{\text{BUSOVP}}$  bits (Reg1[2:1), with the default setting of 7 V. If OVP is detected, the FAN54020 suspends charging functionality if charging is active when OVP is detected. The FAN54020 interrupts the host when the OVP event occurs and sets the OVP\_FLAG bit.

Charging resumes when  $V_{BUS}$  returns below the OVP threshold. While charging is suspended, the  $t_{30MIN}$  or  $t_{32S}$  timer continues and D+ remains at 0.6 V if DBP is LOW.

When  $V_{BUS}$  rises above  $V_{IBUS(DIS)}$  (6.0 V typical), the IBUS loop is disabled and remains disabled for the next one second. If  $V_{BUS}$  falls below  $V_{IBUS(DIS)}$  (5.75 V), the IBUS loop is re-enabled. This allows Q3 to be used as a linear regulator to protect PMID from going above about 6 V, while still allowing the charger to operate up to its OVP threshold. When Q3 is used as a linear regulator, it can no longer be used as a sense element for IBUS.

$V_{BUS}$  is typically 5 V  $\pm 10\%,$  depending on the charging current. If the FAN54020 is programmed to a higher current than the charger can support, a VBUS regulation loop ensures that the "weak" source does not create a situation where VBUS collapses due to loading. The FAN54020 attempts to lower the charger current and maintain VBUS to the value set in the VBUS\_REF bits (Reg2[3:2]). The VBUS regulation loop is enabled by default and has a default value of 4.3 V.

Charging is stopped if  $V_{BUS}$  falls below  $V_{IN(MIN)1}$  (3.7 V typical) or  $V_{BAT}$ , typically indicating that VBUS has been disconnected. Charging remains stopped until  $V_{BUS}$  rises above  $V_{IN(MIN)1}$  (4.4 V typical) and stays above this threshold.

#### Thermal Regulation Loop

If the IC junction temperature reaches  $T_{\text{CF}}$  (Reg5[7:6]), the charger reduces its output current to 300 mA to prevent overheating and the TREG\_FLAG bit is set. If the temperature increases beyond  $T_{\text{SHUTDWN}}$ ; charging is suspended and the TSD\_FLAG is set. While charging is suspended, the  $t_{30\text{MIN}}$  or  $t_{32\text{S}}$  timer continues to run and D+ remains at 0.6 V if DBP is LOW. Charging resumes at programmed current after the die cools below  $T_{\text{CF}}$ . This algorithm allows for the fastest recovery from a thermal regulation event, while still averaging a current that keeps the temperature below  $T_{\text{CF}}$ .

In both cases, removal of the over-temperature conditions is indicated via the OT\_RECOV bit. Temperature is continuously monitored whenever the charger is enabled.

Additional  $\theta_{JA}$  data points, measured using the FAN54020 evaluation board, are given in Table 3 (measured with  $T_A$ =25°C). As power dissipation increases, the effective  $\theta_{JA}$  decreases due to the larger difference between the die temperature and its ambient.

Table 3. FAN54020 Evaluation Board Θ<sub>JA</sub>

| Power (W) | $\theta_{JA}$ |

|-----------|---------------|

| 0.504     | 54°C/W        |

| 0.844     | 50°C/W        |

| 1.506     | 46°C/W        |

#### **Safety Registers**

The SAFETY register (Reg0Fh) prevents the values in  $V_{OREG}$  (Reg4[5:0]) and  $I_{OCHARGE}$  (Reg3 [7:4]) from exceeding the SAFETY register values of  $V_{SAFE}$  (Reg0Fh[3:0]) and  $I_{SAFE}$  (Reg0Fh[7:4]).