# DATASHEET

# Low Power DRAM (LPDDR4 FBGA)

D1611PM3BDGUI-U B3221PM3BDGUI-U B3221PM3BDGVIW-U C3212PM3BDGUI-U Q6422PM3BDGVK-U

## **Specifications**

- Die Density: 16Gbits

- Organization

- x 16 bits: 128M words x 16 bits x 8 banks

- 2 pieces of 16Gb (x16) in one package (For 32Gb case)

- Row Address: R0 ~ R16

- Column Address: C0 ~ C9

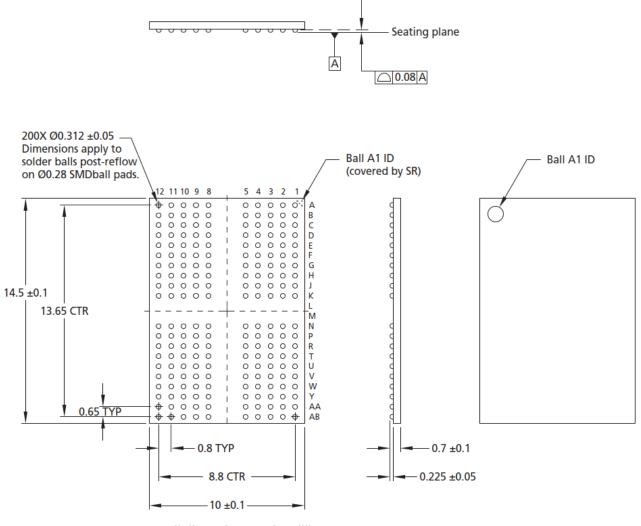

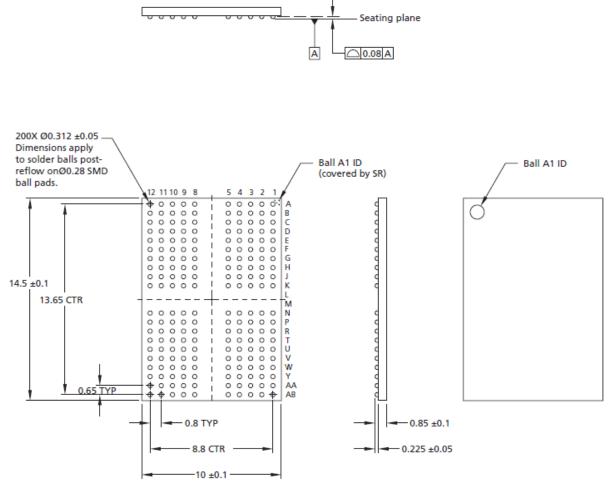

- Package

- 200-ball FBGA

- Power supply

- VDD1 = 1.8V (1.70V to 1.95V)

- VDD2, VDDCA and VDDQ = 1.1V (1.06V to 1.17V)

- Data rate:

- 4266Mbps max. Backward compatible

- Eight internal banks per channel for concurrent operation

- Burst lengths (BL): 16, 32 and on-the-fly

On the fly mode is enabled by MRS

- Programmable RL (Read Latency) and WL (Write Latency)

- Precharge: auto precharge option for each burst access

- Programmable driver strength

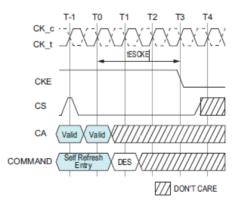

- Refresh: auto-refresh, self-refresh

- Refresh cycles: 8192 cycles/32ms

Average refresh period: 3.9µs

- Operating temperature range

- TC =  $-25^{\circ}$ C to  $+85^{\circ}$ C (Standard)

- TC = -40°C to +95°C (Industrial Temperature)

(1024Mx16bitsx1channel) (1024Mx16bitsx2channel) (1024Mx16bitsx2channel) (2048Mx16bitsx1channel) (2048Mx16bitsx2channel)

#### Features

- Low power consumption

- Per Bank Refresh

- Partial Array Self-Refresh (PASR)

- Bank Masking

- Segment Masking

- Auto Temperature Compensated Self-Refresh

(ATCSR) by built-in temperature sensor

- All bank auto refresh and directed per bank auto refresh supported

- Double-data-rate architecture; two data transfers per one clock cycle

- Differential clock inputs (CK\_t and CK\_c)

- Bi-directional differential data strobe (DQS\_tandDQS\_c)

- Commands entered on both rising and falling CK\_t edge; data and data mask referenced to both edges of DQS\_t

- DMI pin support for write data masking and DBIdc functionality

| Lower Clock<br>Frequency | Upper Clock WRITE Latend |             | Latency |                 |                |  |  |

|--------------------------|--------------------------|-------------|---------|-----------------|----------------|--|--|

| Limit (MHz)              | Limit (MHz)              | Set A Set B |         | DBI<br>Disabled | DBI<br>Enabled |  |  |

| 1600                     | 1866                     | 16          | 30      | 32              | 36             |  |  |

| 1866                     | 2133                     | 18          | 34      | 36              | 40             |  |  |

|                         | Device Addressing        |                                                       |                                                        |                                                        |                                                        |  |  |  |  |  |

|-------------------------|--------------------------|-------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--|--|--|--|--|

| Part N                  | Number                   | D1611PM3BDGUI-U                                       | B3221PM3BDGUI-U<br>B3221PM3BDGVIW-U                    | C3212PM3BDGUI-U                                        | Q6422PM3BDGVK-U                                        |  |  |  |  |  |

| Devic                   | e density                | 16Gb (1024M x 16<br>I/O x 1 channel)                  | 32Gb (1024M x 16 I/O<br>x 2 channels)                  | 32Gb (2048M x 16<br>I/O x 1 channels)                  | 64Gb (2048M x 16<br>I/O x 2 channels)                  |  |  |  |  |  |

| Numb<br>devic           | per of die per<br>e      | 1                                                     | 2                                                      | 2                                                      | 4                                                      |  |  |  |  |  |

| Devic<br>rank)          | e density (per           | 16Gb                                                  | 32Gb                                                   | 16Gb                                                   | 32Gb                                                   |  |  |  |  |  |

| Die d                   | ensity                   | 16Gb                                                  | 16Gb                                                   | 16Gb                                                   | 16Gb                                                   |  |  |  |  |  |

| Devic                   | e configuration          | 128Mb x 1 rank(s) x 8<br>banks x 16 DQ x 1<br>channel | 128Mb x 1 rank(s) x 8<br>banks x 16 DQ x 2<br>channels | 128Mb x 2 rank(s) x 8<br>banks x 16 DQ x 1<br>channels | 128Mb x 2 rank(s) x 8<br>banks x 16 DQ x 2<br>channels |  |  |  |  |  |

| Numb                    | er of channels           | 1                                                     | 2                                                      | 1                                                      | 2                                                      |  |  |  |  |  |

| Numb                    | er of ranks              | 1                                                     | 1                                                      | 2                                                      | 2                                                      |  |  |  |  |  |

| chanr                   | 1                        | 8                                                     | 8                                                      | 8                                                      | 8                                                      |  |  |  |  |  |

| Numb<br>chanr           | er of rows (per<br>el)   | 131,072                                               | 131,072                                                | 131,072                                                | 131,072                                                |  |  |  |  |  |

| Bank                    | address                  | BA0-BA2                                               | BA0-BA2                                                | BA0-BA2                                                | BA0-BA2                                                |  |  |  |  |  |

| v16                     | Row<br>addresses         | R0-R16                                                | R0-R16                                                 | R0-R16                                                 | R0-R16                                                 |  |  |  |  |  |

| x16 Column<br>addresses |                          | C0-C9                                                 | C0-C9                                                  | C0-C9                                                  | C0-C9                                                  |  |  |  |  |  |

| Burst<br>bound          | starting address<br>lary | 64-bit                                                | 64-bit                                                 | 64-bit                                                 | 64-bit                                                 |  |  |  |  |  |

Notes: 1. The lower two column addresses (C0–C1) are assumed to be zero and are not transmitted on the CA bus.

2. Row and column address values on the CA bus that are not used for a particular density are "Don't Care."

## **Revision History**

| Revision No. | History                                            | Release date | Editor   | Approved by            |

|--------------|----------------------------------------------------|--------------|----------|------------------------|

| A00          | Initial release                                    | Feb 2024     | Jona Lee | Sander Huang / CK Wang |

| B00          | Add part number C3212PM3BDGUI-U & B3221PM3BDGVIW-U | June 2024    | Jona Lee | Sander Huang / CK Wang |

| C00          | Add part number Q6422PM3BDGVK-U                    | July 2024    | Jona Lee | Sander Huang / CK Wang |

\*Products and specifications discussed herein are for evaluation and reference purposes only and are subject to change by without notice.

All information discussed herein is provided on an "as is" basis, without warranties of any kind.

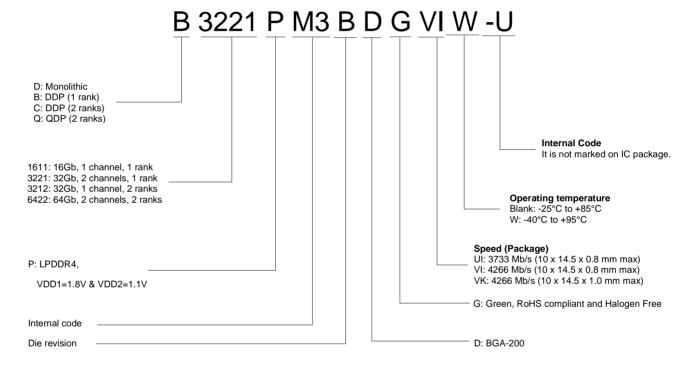

#### **Ordering Information**

| Part number      | Die revision | Organization<br>(words x bits x channels) | Internal banks | JEDEC speed | Package       |

|------------------|--------------|-------------------------------------------|----------------|-------------|---------------|

| D1611PM3BDGUI-U  | B Die        | 1024M x 16bits x 1 channel                | 8 banks        | 3733 Mb/s   | 200 ball FBGA |

| B3221PM3BDGUI-U  | B Die        | 1024M x 16bits x 2 channels               | 8 banks        | 3733 Mb/s   | 200 ball FBGA |

| B3221PM3BDGVIW-U | B Die        | 1024M x 16bits x 2 channels               | 8 banks        | 4266 Mb/s   | 200 ball FBGA |

| C3212PM3BDGUI-U  | B Die        | 2048M x 16bits x 1 channel                | 8 banks        | 3733 Mb/s   | 200 ball FBGA |

| Q6422PM3BDGVK-U  | B Die        | 2048M x 16bits x 2 channels               | 8 banks        | 4266 Mb/s   | 200 ball FBGA |

#### **Part Number**

## 1. LPDDR4 Interface

## 1.1 Pin Function and Descriptions

|                                                                 |           | Table — Pin Function and Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------------------------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name                                                            | Туре      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

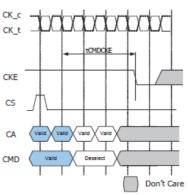

| CK_t_A, CK_c_A<br>CK_t_B, CK_c_B                                | Input     | <b>Clock:</b> CK_t and CK_c are differential clock inputs. All address, command, and control input signals are sampled on the crossing of the positive edge of CK_t and the negative edge of CK_c. AC timings for CA parameters are referenced to CK. Each channel (A & B) has its own clock pair.                                                                                                                                                                                                                                              |

| CKE0_A<br>CKE0_B                                                | Input     | <b>Clock Enable:</b> CKE HIGH activates and CKE LOW deactivates the internal clock circuits, input buffers, and output drivers. Power-saving modes are entered and exited via CKE transitions.<br>CKE is part of the command code. Each channel (A & B) has its own CKE signal.                                                                                                                                                                                                                                                                 |

| CS0_A<br>CS0_B                                                  | Input     | Chip Select: CS is part of the command code. Each channel (A & B) has its own CS signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CA[5:0]_A<br>CA[5:0]_B                                          | Input     | <b>Command/Address Inputs:</b> CA signals provide the Command and Address inputs according to the Command Truth Table. Each channel (A&B) has its own CA signals.                                                                                                                                                                                                                                                                                                                                                                               |

| ODT_CA_A<br>ODT_CA_B                                            | Input     | <b>CA ODT Control:</b> The ODT_CA pin is used in conjunction with the Mode Register to turn on/off the On-Die-Termination for CA pins.                                                                                                                                                                                                                                                                                                                                                                                                          |

| DQ[15:0]_A,<br>DQ[15:0]_B                                       | I/O       | Data Input/Output: Bi-direction data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| DQS[1:0]_t_A,<br>DQS[1:0]_c_A,<br>DQS[1:0]_t_B,<br>DQS[1:0]_c_B | I/O       | <b>Data Strobe:</b> DQS_t and DQS_c are bi-directional differential output clock signals used to strobe data during a READ or WRITE. The Data Strobe is generated by the DRAM for a READ and is edge-aligned with Data. The Data Strobe is generated by the Memory Controller for a WRITE and must arrive prior to Data. Each byte of data has a Data Strobe signal pair. Each channel (A & B) has its own DQS strobes.                                                                                                                         |

| DMI[1:0]_A,<br>DMI[1:0]_B                                       | I/O       | <b>Data Mask Inversion:</b> DMI is a bi-directional signal which is driven HIGH when the data<br>on the data bus is inverted, or driven LOW when the data is in its normal state. Data<br>Inversion can be disabled via a mode register setting.<br>Each byte of data has a DMI signal. Each channel (A & B) has its own DMI signals. This<br>signal is also used along with the DQ signals to provide write data masking information<br>to the DRAM. The DMI pin function - Data Inversion or Data mask - depends on Mode<br>Register setting. |

| ZQ                                                              | Reference | <b>Calibration Reference:</b> Used to calibrate the output drive strength and the termination resistance. There is one ZQ pin per die. The ZQ pin shall be connected to VDDQ through a $240\Omega \pm 1\%$ resistor.                                                                                                                                                                                                                                                                                                                            |

| VDDQ,<br>VDD1,<br>VDD2                                          |           | Power Supplies: Isolated on the die for improved noise immunity.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| VSS, VSSQ                                                       | GND       | Ground Reference: Power supply ground reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RESET_n                                                         | Input     | <b>RESET:</b> When asserted LOW, the RESET_n signal resets all channels of the die. There is one RESET_n pad per die.                                                                                                                                                                                                                                                                                                                                                                                                                           |

NOTE 1 "\_A" and "\_B" indicate DRAM channel "\_A" pads are present in all devices. "\_B" pads are present in dual channel SDRAM devices only.

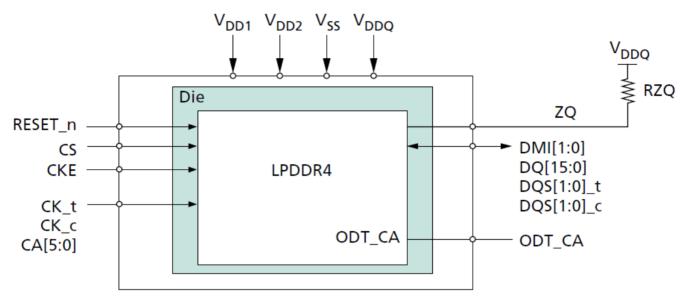

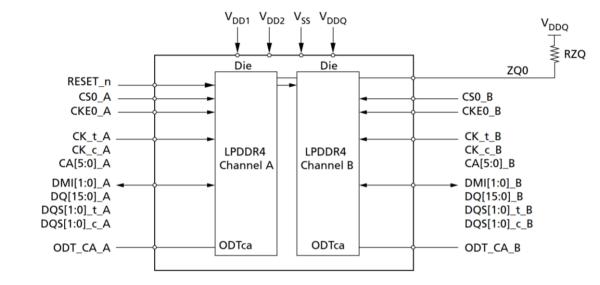

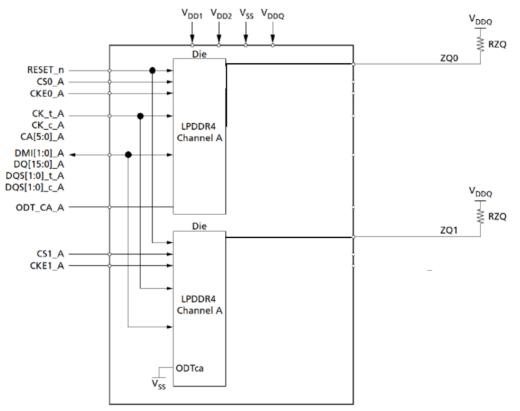

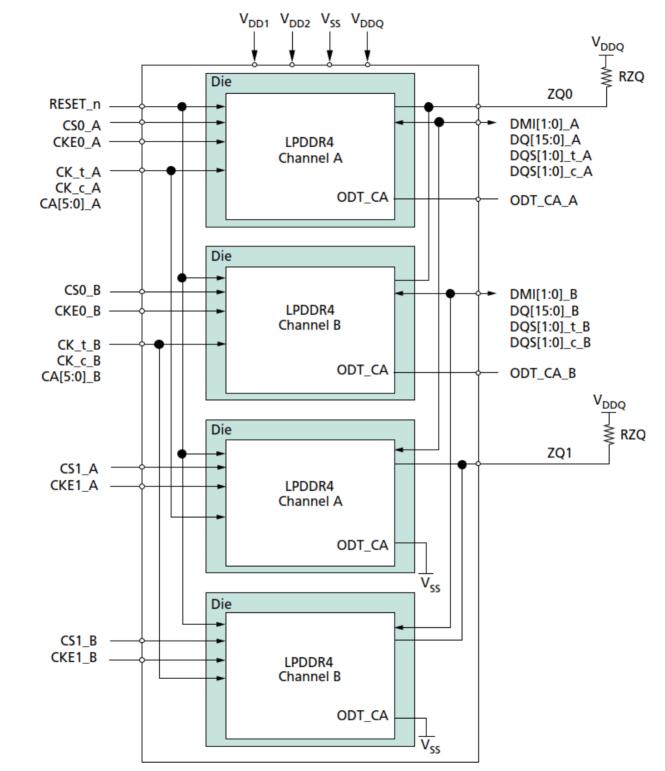

## **Functional Block Diagram**

## SDP

Single-Die, Single-Channel, Single-Rank Package Block Diagram (x16l/O)

## DDP

Dual-Die, Dual-Channel, Single-Rank Package Block Diagram

Dual-Die, Single-Channel, Dual-Rank Package Block Diagram

## QDP

Quad-Die, Dual-Channel, Dual-Rank Package Block Diagram (x32 I/O)

NOTE 1. ODT\_CA for Rank 0 of each channel is wired to the respective ODT ball. ODT\_CA for Rank 1 of each channel is wired to VSS in the package.

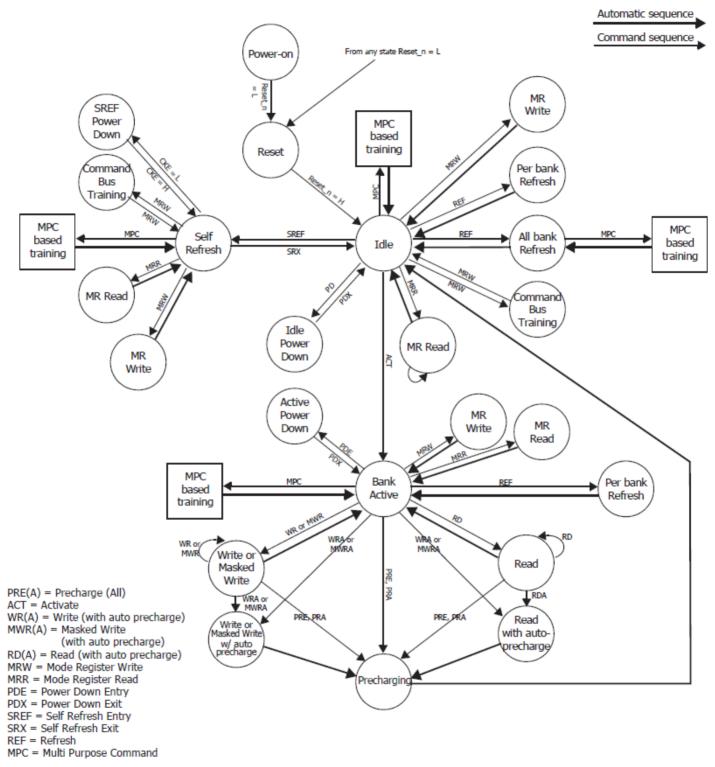

#### **Simplified State Diagram**

#### Figure — Simplified Bus Interface State Diagram

Note 1: For DDR4 Mobile RAM in the Idle state, all banks are precharged.

## **1.2 Electrical Conditions**

All voltages are referenced to VSS (GND)

- Execute power-up and Initialization sequence before proper device operation is achieved.

- Operation or timing that is not specified is illegal, and after such an event, in order to guarantee proper operation, the DDR4 Mobile RAM Device must be powered down and then restarted through the specialized initialization sequence before normal operation can continue.

#### 1.2.1 Absolute maximum Ratings

|                                      |           |      | atings |      |      |

|--------------------------------------|-----------|------|--------|------|------|

| Parameter                            | Symbol    | min. | max.   | Unit | Note |

| VDD1 supply voltage relative to VSS  | VDD1      | -0.4 | 2.1    | V    | 2    |

| VDD2 supply voltage relative to VSS  | VDD2      | -0.4 | 1.5    | V    | 2    |

| VDDQ supply voltage relative to VSSQ | VDDQ      | -0.4 | 1.5    | V    | 2    |

| Voltage on any ball relative to VSS  | VIN, VOUT | -0.4 | 1.5    | V    |      |

| Storage Temperature                  | TSTG      | -55  | 125    | °C   | 3    |

|                                      |           |      |        |      |      |

#### Table — Absolute maximum Ratings

Notes:

1. Stresses greater than those listed under "Absolute maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

2. See Power-Ramp section "Power-up, initialization and Power-Off" on section1.4 for relationship between power supplies

3. Storage Temperature is the case surface temperature on the center/top side of the DDR3 Mobile RAM Device. For the measurement conditions, please refer to JESD51-2 standard.

Caution

Exposing the device to stress above those listed in Absolute maximum Ratings could cause permanent damage. The device is not meant to be operated under conditions outside the limits described in the operational section of this specification. Exposure to Absolute maximum Rating conditions for extended periods may affect device reliability.

## 1.2.2 Recommended DC Operating Conditions

#### Table — Recommended DC Operating Conditions

|                                 |        |      | U    |      |      |       |

|---------------------------------|--------|------|------|------|------|-------|

| Parameter                       | Symbol | min. | Тур  | max. | Unit | Note  |

| Core Power1                     | VDD1   | 1.70 | 1.80 | 1.95 | V    | 1,2   |

| Core Power2, Input buffer power | VDD2   | 1.06 | 1.10 | 1.17 | V    | 1,2,3 |

| I/O Buffer Power                | VDDQ   | 1.06 | 1.10 | 1.17 | V    | 2,3   |

|                                 |        |      |      |      |      |       |

1. VDD1 uses significantly less current than VDD2.

2. The voltage range is for DC voltage only. DC is defined as the voltage supplied at the DRAM and is inclusive of all noise up to 20MHz at the DRAM package ball.

3. The voltage noise tolerance from DC to 20MHz exceeding a pk-pk tolerance of 45mV at the DRAM ball is not included in the TdIVW.

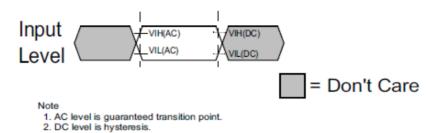

## 1.2.3 AC and DC Input Measurement Levels

## 1.2.3.1 V High speed LVCMOS (HS\_LLVCMOS)

|                     | вына шра |           |           |      |      |

|---------------------|----------|-----------|-----------|------|------|

| Parameter           | Symbol   | min.      | max.      | Unit | Note |

| AC input logic high | VIH(AC)  | 0.75*VDD2 | VDD2+0.2  | V    | 1    |

| AC input logic low  | VIL(AC)  | -0.2      | 0.25*VDD2 | V    | 1    |

| DC input logic high | VIH(DC)  | 0.65*VDD2 | VDD2+0.2  | V    |      |

| DC input logic low  | VIL(DC)  | -0.2      | 0.35*VDD2 | V    |      |

#### Table — LPDDR4 Input level for CKE

Note: 1. See "Overshoot and Undershoot Specifications" on section 1.2.4.

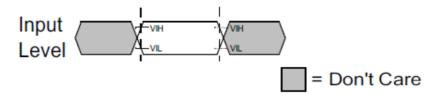

### 1.2.3.2 LPDDR4 Input Level for Reset\_n and ODT\_CA

#### Table — LPDDR4 Input level for Reset\_n and ODT\_CA

| Parameter        | Symbol | min.     | max.      | Unit | Note |

|------------------|--------|----------|-----------|------|------|

| Input high level | VIH    | 0.8*VDD2 | VDD2+0.2  | V    | 1    |

| Input low level  | VIL    | -0.2     | 0.20*VDD2 | V    | 1    |

Note: 1. See "Overshoot and Undershoot Specifications" on section 1.2.4.

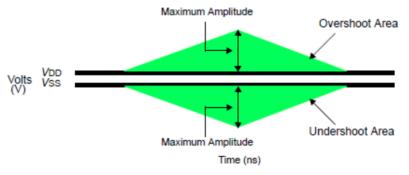

## 1.2.4 AC Overshoot and Undershoot Specifications

|                                                     | n opcoi | noution       |      |

|-----------------------------------------------------|---------|---------------|------|

| Parameter                                           |         | Specification | Unit |

| maximum peak amplitude allowed for overshoot area.  | Max.    | 0.3           | V    |

| maximum peak amplitude allowed for undershoot area. | Max.    | 0.3           | V    |

| maximum overshoot area above VDD/VDDQ               | Max.    | 0.1           | V-ns |

| maximum undershoot area below VSS/VSSQ              | Max.    | 0.1           | V-ns |

#### Table — LPDDR4 Overshoot/Undershoot Specification

Figure — AC Overshoot and Undershoot Definition

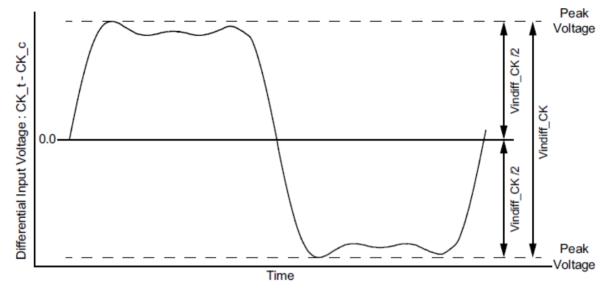

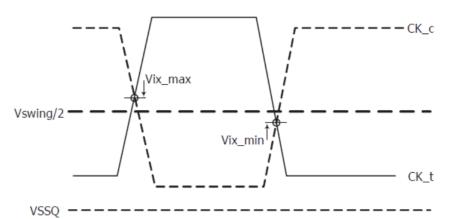

#### 1.2.5 Differential Input Voltage 1.2.5.1 Differential Input Voltage for CK

The minimum input voltage need to satisfy both Vindiff\_CK and Vindiff\_CK /2 specification at input receiver and their measurement period is 1tCK. Vindiff\_CK is the peak to peak voltage centered on 0 volts differential and Vindiff\_CK /2 is max and min peak voltage from 0V.

Figure — CK Differential input voltage

Table — CK Differential input voltage

|                               |            |           |     | Data           | Rate |                 |     |      |       |

|-------------------------------|------------|-----------|-----|----------------|------|-----------------|-----|------|-------|

| Parameter                     | Symbol     | 1600/1867 |     | 2133/2400/3200 |      | /3200 3733/4267 |     | Unit | Notes |

|                               |            | Min       | Max | Min            | Max  | Min             | Max |      |       |

| CK differential input voltage | Vindiff_CK | 420       | -   | 380            | -    | 360             | -   | mV   | 1     |

| Nata                          | ····•··    |           | 1   |                | 1    |                 |     |      | L     |

Notes:

1. The peak voltage of Differential CK signals is calculated in a following equation.

Vindiff\_CK = (Max Peak Voltage) - (Min Peak Voltage)

Max Peak Voltage = Max(f(t)) Min Peak Voltage = Min(f(t))

$f(t) = VCK_t - VCK_c$

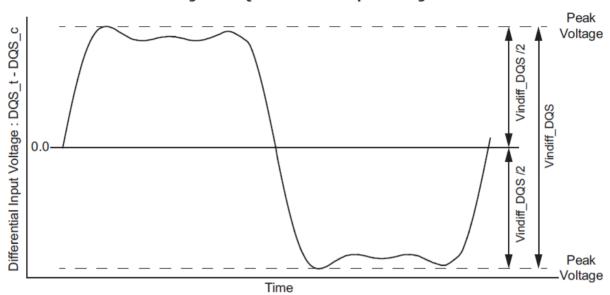

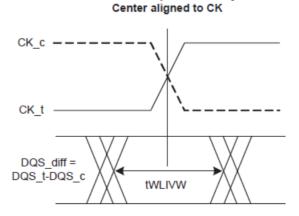

## 1.2.5.2 Differential Input Voltage for DQS

The minimum input voltage need to satisfy both Vindiff\_DQS and Vindiff\_DQS /2 specification at input receiver and their measurement period is 1UI(tCK/2). Vindiff\_DQS is the peak to peak voltage centered on 0 volts differential and Vindiff\_DQS /2 is max and min peak voltage from 0V

#### Table — Differential AC and DC Input Levels

|                        |             |      |       | Data    | Rate    |      |       |      |       |

|------------------------|-------------|------|-------|---------|---------|------|-------|------|-------|

| Parameter              | Symbol      | 1600 | /1867 | 2133/24 | 00/3200 | 3733 | /4267 | Unit | Notes |

|                        |             | Min  | Max   | Min     | Max     | Min  | Max   |      |       |

| DQS differential input | Vindiff_DQS | 360  | -     | 360     | -       | 340  | -     | mV   | 1     |

| Nataai                 |             |      |       |         |         |      |       |      |       |

Notes:

1. The peak voltage of Differential CK signals is calculated in a following equation.

Vindiff\_DQS = (Max Peak Voltage) - (Min Peak Voltage)

Max Peak Voltage = Max(f(t))

Min Peak Voltage = Min(f(t))

$f(t) = VDQS_t - VDQS_c$

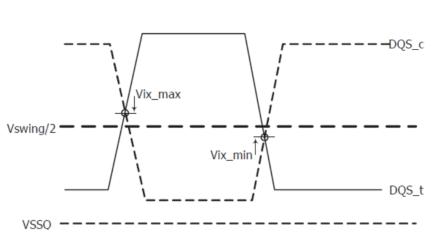

## 1.2.6 Differential Input Cross Point Voltage

VDDQ ---

Figure — DQS input cross-point voltage (V)VIX Definition

| Parameter                                            | Symbol        | Min / |           | Data rate      |           | Unit | Note |

|------------------------------------------------------|---------------|-------|-----------|----------------|-----------|------|------|

| Falameter                                            | Symbol        | Max   | 1600/1867 | 2133/2400/3200 | 3733/4267 | Unit | note |

| DQS Differential input cross-<br>point voltage ratio | Vix_DQS_ratio | Max   | 20        | 20             | 20        | %    | 1,2  |

| Notes:                                               |               |       |           |                |           |      |      |

Table — DQS input voltage cross-point (Vix) ratio

1. The Vix voltage is referenced to Vswing/2(avg)= 0.5(VDQS\_t + VDQS\_c) where the average is over tbd UI.

2. The ratio of the Vix pk voltage divided by Vdiff\_DQS : Vix\_DQS\_Ratio = 100\* (Vix\_DQS/Vdiff DQS pk-pk) where VdiffDQS  $pk-pk = 2^*|VDQS_t - VDQS_c|$ .

Figure — CK input cross-point voltage (Vix)

| Deremeter                                           | Symbol       | Min / |           | Data rate      |           | Linit | Note |

|-----------------------------------------------------|--------------|-------|-----------|----------------|-----------|-------|------|

| Parameter                                           | Symbol       | Max   | 1600/1867 | 2133/2400/3200 | 3733/4267 | Unit  | Note |

| CK Differential input cross-<br>point voltage ratio | Vix_CK_ratio | Max   | 25        | 25             | 25        | %     | 1,2  |

Notes:

- 1. The Vix voltage is referenced to Vswing/2(avg)= 0.5(VCK\_t + VCK\_c) where the average is over tbd UI.

- 2. The ratio of the Vix pk voltage divided by Vdiff\_CK : Vix\_CK\_Ratio = 100\* (Vix\_CK/Vdiff CK pk-pk) where VdiffCK pk-pk = 2\*|VCK\_t VCK\_c|

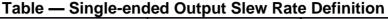

#### 1.2.6.1 Single Ended Output Slew Rate

With the reference load for timing measurements, output slew rate for falling and rising edges is defined and measured between VOL(AC) and VOH(AC) for single ended signals as shown in Table 14 and Figure 8.

| Description                                    | Meas    | sured   | Defined by                      |

|------------------------------------------------|---------|---------|---------------------------------|

| Description                                    | from    | to      | Defined by                      |

| Single-ended output slew rate for rising edge  | VOL(AC) | VOH(AC) | [VOH(AC) – VOL(AC)] / DeltaTRse |

| Single-ended output slew rate for falling edge | VOH(AC) | VOL(AC) | [VOH(AC) – VOL(AC)] / DeltaTFse |

#### Figure — Single Ended Output Slew Rate Definition

| Parameter                                      | Symbol | min. | max. | Unit |

|------------------------------------------------|--------|------|------|------|

| Single-ended Output Slew Rate (VOH = VDDQ/3)   | SRQse  | 3.5  | 9.0  | V/ns |

| Output slew-rate matching Ratio (Rise to Fall) |        | 0.8  | 1.2  |      |

Remark: SR: Slew Rate, Q: Query Output (like in DQ, which stands for Data-in, Query-Output), se: Single-ended Signals

Notes:

- 1. Measured with output reference load.

- 2. The ratio of pull-up to pull-down slew rate is specified for the same temperature and voltage, over the entire temperature and voltage range. For a given output, it represents the maximum difference between pull-up and pulldown drivers due to process variation.

- 3. The output slew rate for falling and rising edges is defined and measured between VOL(AC) and VOH(AC).

- 4. Slew rates are measured under normal SSO conditions, with 1/2 of DQ signals per data byte driving logic high and 1/2 of DQ signals per data byte driving logic low.

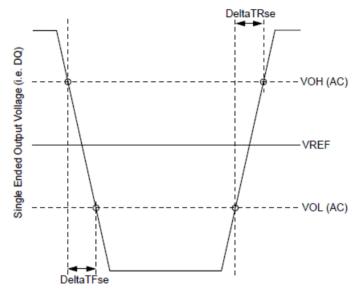

#### 1.2.7 Differential Output Slew Rate

With the reference load for timing measurements, output slew rate for falling and rising edges is defined and measured between VOLdiff(AC) and VOHdiff(AC) for differential signals as shown in Table 16 and Figure 9.

| Description                                    | Meas        | sured       | Defined by                                |

|------------------------------------------------|-------------|-------------|-------------------------------------------|

| Description                                    | from        | to          | Defined by                                |

| Differential output slew rate for rising edge  | VOLdiff(AC) | VOHdiff(AC) | [VOHdiff(AC) – VOLdiff(AC)] / DeltaTRdiff |

| Differential output slew rate for falling edge | VOHdiff(AC) | VOLdiff(AC) | [VOHdiff(AC) – VOLdiff(AC)] / DeltaTFdiff |

|                                                |             |             |                                           |

#### Table — Differential Output Slew Rate Definition

Note: 1. Output slew rate is verified by design and characterization, and may not be subject to production test.

Figure — Differential Output Slew Rate Definition

|--|

| Parameter                                | Symbol  | min.       | max. | Unit |

|------------------------------------------|---------|------------|------|------|

| fferential Output Slew Rate (VOH=VDDQ/3) | SRQdiff | 7          | 18   | V/ns |

|                                          |         | <b>•</b> • | ~    |      |

Remark: SR: Slew Rate, Q: Query Output (like in DQ, which stands for Data-in, Query-Output), diff: Differential Signals

Notes:

Dif

1. Measured with output reference load.

2. The output slew rate for falling and rising edges is defined and measured between VOL(AC) and VOH(AC).

3. Slew rates are measured under normal SSO conditions, with 1/2 of DQ signals per data byte driving logic high and 1/2 of DQ signals per data byte driving logic low.

## **1.3 Electrical Specifications**

#### 1.3.1 IDD Measurement Conditions

The following definitions are used within the IDD measurement tables: LOW: VIN  $\leq$  VIL(DC) max. HIGH: VIN  $\geq$  VIH(DC) min. STABLE: Inputs are stable at a HIGH or LOW level

|           |                  |      |      |      | <u> </u> |      | -    |      |  |  |  |

|-----------|------------------|------|------|------|----------|------|------|------|--|--|--|

|           | Switching for CA |      |      |      |          |      |      |      |  |  |  |

| CK_t edge | R1               | R2   | R3   | R4   | R5       | R6   | R7   | R8   |  |  |  |

| CKE       | HIGH             | HIGH | HIGH | HIGH | HIGH     | HIGH | HIGH | HIGH |  |  |  |

| CS        | LOW              | LOW  | LOW  | LOW  | LOW      | LOW  | LOW  | LOW  |  |  |  |

| CA0       | HIGH             | LOW  | LOW  | LOW  | LOW      | HIGH | HIGH | HIGH |  |  |  |

| CA1       | HIGH             | HIGH | HIGH | LOW  | LOW      | LOW  | LOW  | HIGH |  |  |  |

| CA2       | HIGH             | LOW  | LOW  | LOW  | LOW      | HIGH | HIGH | HIGH |  |  |  |

| CA3       | HIGH             | HIGH | HIGH | LOW  | LOW      | LOW  | LOW  | HIGH |  |  |  |

| CA4       | HIGH             | LOW  | LOW  | LOW  | LOW      | HIGH | HIGH | HIGH |  |  |  |

| CA5       | HIGH             | HIGH | HIGH | LOW  | LOW      | LOW  | LOW  | HIGH |  |  |  |

|           |                  |      |      |      |          |      |      |      |  |  |  |

#### Table — Definition of Switching for CA Input Signals

Notes:

1. CS must always be driven LOW.

2. 50% of CA bus is changing between HIGH and LOW once per clock for the CA bus.

3. The above pattern is used continuously during IDD measurement for IDD values that require switching on the CA bus.

| Clock Cycle Number | CKE  | CS   | Command  | CA0 | CA1 | CA2 | CA3 | CA4 | CA5 |

|--------------------|------|------|----------|-----|-----|-----|-----|-----|-----|

| N                  | HIGH | HIGH | Read-1   | L   | Н   | L   | L   | L   | L   |

| N+1                | HIGH | LOW  | Read-1   | L   | Н   | L   | L   | L   | L   |

| N+2                | HIGH | HIGH | CAS-2    | L   | Н   | L   | L   | Н   | L   |

| N+3                | HIGH | LOW  |          | L   | L   | L   | L   | L   | L   |

| N+4                | HIGH | LOW  | Deselect | L   | L   | L   | L   | L   | L   |

| N+5                | HIGH | LOW  | Deselect | L   | L   | L   | L   | L   | L   |

| N+6                | HIGH | LOW  | Deselect | L   | L   | L   | L   | L   | L   |

| N+7                | HIGH | LOW  | Deselect | L   | L   | L   | L   | L   | L   |

| N+8                | HIGH | HIGH | Dood 1   | L   | Н   | L   | L   | L   | L   |

| N+9                | HIGH | LOW  | Read-1   | L   | Н   | L   | L   | Н   | L   |

| N+10               | HIGH | HIGH |          | L   | Н   | L   | L   | Н   | Н   |

| N+11               | HIGH | LOW  | CAS-2    | Н   | Н   | Н   | Н   | Н   | Н   |

| N+12               | HIGH | LOW  | Deselect | L   | L   | L   | L   | L   | L   |

| N+13               | HIGH | LOW  | Deselect | L   | L   | L   | L   | L   | L   |

| N+14               | HIGH | LOW  | Deselect | L   | L   | L   | L   | L   | L   |

| N+15               | HIGH | LOW  | Deselect | L   | L   | L   | L   | L   | L   |

#### Table — CA pattern for IDD4R for BL = 16

Notes:

1. BA[2:0] = 010, CA[9:4] = 000000 or 111111, Burst Order CA[3:2] = 00 or 11 (Same as LPDDR3 IDD4R Spec)

2. Difference from LPDDR3 Spec : CA pins are kept low with DES CMD to reduce ODT current.

| Clock Cycle | СКЕ  | CS   | Command  | CA0 | CA1 | CA2 | CA3 | CA4  | CA5 |

|-------------|------|------|----------|-----|-----|-----|-----|------|-----|

| Number      |      |      | Command  | UNU | UAI | UA2 | UNU | 0/14 | UNU |

| N           | HIGH | HIGH | Write-1  | L   | L   | Н   | L   | L    | L   |

| N+1         | HIGH | LOW  | WIILE-1  | L   | н   | L   | L   | L    | L   |

| N+2         | HIGH | HIGH | CAS-2    | L   | Н   | L   | L   | Н    | L   |

| N+3         | HIGH | LOW  |          | L   | L   | L   | L   | L    | L   |

| N+4         | HIGH | LOW  | Deselect | L   | L   | L   | L   | L    | L   |

| N+5         | HIGH | LOW  | Deselect | L   | L   | L   | L   | L    | L   |

| N+6         | HIGH | LOW  | Deselect | L   | L   | L   | L   | L    | L   |

| N+7         | HIGH | LOW  | Deselect | L   | L   | L   | L   | L    | L   |

| N+8         | HIGH | HIGH | Write-1  | L   | L   | Н   | L   | L    | L   |

| N+9         | HIGH | LOW  | write-i  | L   | Н   | L   | L   | Н    | L   |

| N+10        | HIGH | HIGH | CAR 2    | L   | Н   | L   | L   | Н    | Н   |

| N+11        | HIGH | LOW  | CAS-2    | L   | L   | н   | Н   | Н    | Н   |

| N+12        | HIGH | LOW  | Deselect | L   | L   | L   | L   | L    | L   |

| N+13        | HIGH | LOW  | Deselect | L   | L   | L   | L   | L    | L   |

| N+14        | HIGH | LOW  | Deselect | L   | L   | L   | L   | L    | L   |

| N+15        | HIGH | LOW  | Deselect | L   | L   | L   | L   | L    | L   |

Table — CA pattern for IDD4W for BL = 16

Notes:

1. BA[2:0] = 010, CA[9:4] = 000000 or 111111 (Same as LPDDR3 IDD4W Spec.)

2. Difference from LPDDR3 Spec:

1-No burst ordering

2-CA pins are kept low with DES CMD to reduce ODT current.

| DBI OFF case |       |       |       |       |       |       |       |       |     |            |

|--------------|-------|-------|-------|-------|-------|-------|-------|-------|-----|------------|

|              | DQ[7] | DQ[6] | DQ[5] | DQ[4] | DQ[3] | DQ[2] | DQ[1] | DQ[0] | DBI | No. of 1's |

| BL0          | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 0   | 8          |

| BL1          | 1     | 1     | 1     | 1     | 0     | 0     | 0     | 0     | 0   | 4          |

| BL2          | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0   | 0          |

| BL3          | 0     | 0     | 0     | 0     | 1     | 1     | 1     | 1     | 0   | 4          |

| BL4          | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 1     | 0   | 2          |

| BL5          | 0     | 0     | 0     | 0     | 1     | 1     | 1     | 1     | 0   | 4          |

| BL6          | 1     | 1     | 1     | 1     | 1     | 1     | 0     | 0     | 0   | 6          |

| BL7          | 1     | 1     | 1     | 1     | 0     | 0     | 0     | 0     | 0   | 4          |

| BL8          | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 0   | 8          |

| BL9          | 1     | 1     | 1     | 1     | 0     | 0     | 0     | 0     | 0   | 4          |

| BL10         | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0   | 0          |

| BL11         | 0     | 0     | 0     | 0     | 1     | 1     | 1     | 1     | 0   | 4          |

| BL12         | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 1     | 0   | 2          |

| BL13         | 0     | 0     | 0     | 0     | 1     | 1     | 1     | 1     | 0   | 4          |

| BL14         | 1     | 1     | 1     | 1     | 1     | 1     | 0     | 0     | 0   | 6          |

| BL15         | 1     | 1     | 1     | 1     | 0     | 0     | 0     | 0     | 0   | 4          |

| BL16         | 1     | 1     | 1     | 1     | 1     | 1     | 0     | 0     | 0   | 6          |

| BL17         | 1     | 1     | 1     | 1     | 0     | 0     | 0     | 0     | 0   | 4          |

| BL18         | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 1     | 0   | 2          |

| BL19         | 0     | 0     | 0     | 0     | 1     | 1     | 1     | 1     | 0   | 4          |

| BL20         | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0   | 0          |

| BL21         | 0     | 0     | 0     | 0     | 1     | 1     | 1     | 1     | 0   | 4          |

| BL22         | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 0   | 8          |

| BL23         | 1     | 1     | 1     | 1     | 0     | 0     | 0     | 0     | 0   | 4          |

| BL24         | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 1     | 0   | 2          |

| BL25         | 0     | 0     | 0     | 0     | 1     | 1     | 1     | 1     | 0   | 4          |

| BL26         | 1     | 1     | 1     | 1     | 1     | 1     | 0     | 0     | 0   | 6          |

| BL27         | 1     | 1     | 1     | 1     | 0     | 0     | 0     | 0     | 0   | 4          |

| BL28         | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 0   | 8          |

| BL29         | 1     | 1     | 1     | 1     | 0     | 0     | 0     | 0     | 0   | 4          |

| BL30         | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0   | 0          |

| BL31         | 0     | 0     | 0     | 0     | 1     | 1     | 1     | 1     | 0   | 4          |

| No. of 1's   | 16    | 16    | 16    | 16    | 16    | 16    | 16    | 16    |     |            |

### Table — Data pattern for IDD4W (DBI off) for BL = 16

Notes:

1. Simplified pattern compared with last showing.

2. Same data pattern was applied to DQ[4], DQ[5], DQ[6], DQ[7] for reducing complexity for IDD4W/R pattern programming.

| DQ[7]DQ[6]DQ[5]DQ[4]DQ[3]DQ[2]DQ[1]DQ[0]DBINo. of 1'sBL011111111108BL111110000004BL200000000000BL300000111104BL40000111104BL5000011104BL61111110004BL81111111004BL8111111108BL9111111104BL11000000000BL130000111104BL120000000004BL120000111104BL1411111110000BL130000 <th></th> <th></th> <th>Table</th> <th></th> <th>DBI OF</th> <th>F case</th> <th>- <u>(</u></th> <th></th> <th></th> <th></th> <th></th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |       | Table |       | DBI OF | F case | - <u>(</u> |       |       |     |            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------|-------|-------|--------|--------|------------|-------|-------|-----|------------|

| BL01111111108BL111110000004BL200000000000BL300000111104BL40000011104BL5000011102BL51111110006BL711111110004BL811111110004BL711110000004BL811111110000BL100000000000BL13000011104BL14111111000BL130000011104BL141111111000BL151111 <td></td> <td>DQ[7]</td> <td>DQ[6]</td> <td>DQ[5]</td> <td></td> <td></td> <td>DQ[2]</td> <td>DQ[1]</td> <td>DQ[0]</td> <td>DBI</td> <td>No. of 1's</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            | DQ[7] | DQ[6] | DQ[5] |        |        | DQ[2]      | DQ[1] | DQ[0] | DBI | No. of 1's |

| BL2         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         1         1         1         0         4           BL5         0         0         0         0         0         1         1         1         1         1         1         1         1         1         1         1         1         1         1         0         4         4         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1 <td>BL0</td> <td></td> <td>1</td> <td></td> <td>_</td> <td>1</td> <td></td> <td></td> <td></td> <td>0</td> <td>8</td>              | BL0        |       | 1     |       | _      | 1      |            |       |       | 0   | 8          |

| BL3         0         0         0         1         1         1         1         1         0         4           BL4         0         0         0         0         0         0         0         1         1         1         0         4           BL5         0         0         0         0         1         1         1         0         4           BL6         1         1         1         1         1         1         1         1         0         0         0         0         4           BL6         1         1         1         1         1         1         1         1         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0 <th< td=""><td>BL1</td><td>1</td><td>1</td><td>1</td><td>1</td><td>0</td><td>0</td><td>0</td><td>0</td><td>0</td><td>4</td></th<>                              | BL1        | 1     | 1     | 1     | 1      | 0      | 0          | 0     | 0     | 0   | 4          |

| BL40000001102BL50000111104BL611111110000BL7111111100004BL8111111111000BL911111000000BL100000000000BL110000000000BL120000011104BL130000000000BL14111111000BL13000000000BL16111111100BL180000000000BL18000000000BL18000000000BL20111111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | BL2        | 0     | 0     | 0     | 0      | 0      | 0          | 0     | 0     | 0   | 0          |

| BL5         0         0         0         1         1         1         1         0         4           BL6         1         1         1         1         1         1         1         0         0         0         0         6           BL7         1         1         1         1         1         1         1         1         0         0         0         0         0         4           BL8         1         1         1         1         1         1         1         1         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                                                | BL3        | 0     | 0     | 0     | 0      | 1      | 1          | 1     | 1     | 0   | 4          |

| BL6         1         1         1         1         1         1         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                              | BL4        | 0     | 0     | 0     | 0      | 0      | 0          | 1     | 1     | 0   | 2          |

| BL7         1         1         1         1         0         0         0         0         4           BL8         1         1         1         1         1         1         1         1         1         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                                    | BL5        | 0     | 0     | 0     | 0      | 1      | 1          | 1     | 1     | 0   | 4          |

| BL8         1         1         1         1         1         1         1         1         1         0         8           BL9         1         1         1         1         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                                    | BL6        | 1     | 1     | 1     | 1      | 1      | 1          | 0     | 0     | 0   | 6          |

| BL9         1         1         1         1         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         1         1         1         1         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                              | BL7        | 1     | 1     | 1     | 1      | 0      | 0          | 0     | 0     | 0   | 4          |

| BL10         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         1         1         1         1         0         2           BL13         0         0         0         0         0         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1 </td <td>BL8</td> <td>1</td> <td>1</td> <td>1</td> <td>1</td> <td>1</td> <td>1</td> <td>1</td> <td>1</td> <td>0</td> <td>8</td>  | BL8        | 1     | 1     | 1     | 1      | 1      | 1          | 1     | 1     | 0   | 8          |

| BL11         0         0         0         1         1         1         1         0         4           BL12         0         0         0         0         0         0         0         1         1         1         0         2           BL13         0         0         0         0         1         1         1         0         2           BL14         1         1         1         1         1         1         1         0         4           BL14         1         1         1         1         1         1         0         0         0         0         0         4           BL16         1         1         1         1         1         1         1         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                                                                | BL9        | 1     | 1     | 1     | 1      | 0      | 0          | 0     | 0     | 0   | 4          |

| BL12         0         0         0         0         0         1         1         0         2           BL13         0         0         0         0         1         1         1         1         0         4           BL14         1         1         1         1         1         1         1         0         4           BL14         1         1         1         1         1         1         0         0         0         0         0         4           BL15         1         1         1         1         1         1         1         1         0         0         0         0         0         4           BL16         1         1         1         1         1         1         1         0         8           BL17         1         1         1         1         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                                                                     | BL10       | 0     | 0     | 0     | 0      | 0      | 0          | 0     | 0     | 0   | 0          |

| BL13         0         0         0         1         1         1         1         0         4           BL14         1         1         1         1         1         1         0         0         0         6           BL15         1         1         1         1         1         0         0         0         0         0         4           BL16         1         1         1         1         1         1         1         1         0         0         0         0         4           BL16         1         1         1         1         1         1         1         1         0         0         0         0         4           BL17         1         1         1         1         1         1         1         0         8           BL18         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                                                                     | BL11       | 0     | 0     | 0     | 0      | 1      | 1          | 1     | 1     | 0   | 4          |

| BL14         1         1         1         1         1         0         0         0         6           BL15         1         1         1         1         0         0         0         0         0         4           BL16         1         1         1         1         1         1         1         1         1         1         1         0         0         0         0         4           BL16         1         1         1         1         1         1         1         1         0         0         0         0         0         0         0         4           BL17         1         1         1         1         1         1         1         1         0         0         0         0         0           BL18         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                                                                | BL12       | 0     | 0     | 0     | 0      | 0      | 0          | 1     | 1     | 0   | 2          |

| BL15         1         1         1         1         0         0         0         0         0         4           BL16         1         1         1         1         1         1         1         1         0         8           BL17         1         1         1         1         1         1         1         0         8           BL18         0         0         0         0         0         0         0         0         0         4           BL20         1         1         1         1         1         1         0         4           BL20         1         1         1         1         1         0         0         0         0         0         0         0         0         6           BL20         1         1         1         1         1         1         0         4         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                                                                     | BL13       | 0     | 0     | 0     | 0      | 1      | 1          | 1     | 1     | 0   | 4          |

| BL16         1         1         1         1         1         1         1         0         88           BL17         1         1         1         1         0         0         0         0         0         0         0         0         0         4           BL18         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0 <th< td=""><td>BL14</td><td>1</td><td>1</td><td>1</td><td>1</td><td>1</td><td>1</td><td>0</td><td>0</td><td>0</td><td>6</td></th<>             | BL14       | 1     | 1     | 1     | 1      | 1      | 1          | 0     | 0     | 0   | 6          |

| BL17         1         1         1         0         0         0         0         0         4           BL18         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0 </td <td>BL15</td> <td>1</td> <td>1</td> <td>1</td> <td>1</td> <td>0</td> <td>0</td> <td>0</td> <td>0</td> <td>0</td> <td>4</td> | BL15       | 1     | 1     | 1     | 1      | 0      | 0          | 0     | 0     | 0   | 4          |

| BL18         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                             | BL16       | 1     | 1     | 1     | 1      | 1      | 1          | 1     | 1     | 0   | 8          |

| BL19         0         0         0         1         1         1         1         0         4           BL20         1         1         1         1         1         1         0         0         0         6           BL21         1         1         1         1         0         0         0         0         6           BL22         0         0         0         0         0         0         0         0         4           BL22         0         0         0         0         0         0         0         0         0         0         4           BL23         0         0         0         0         0         0         1         1         1         0         4           BL23         0         0         0         0         0         0         0         0         2           BL24         0         0         0         0         0         0         0         0         0         0         0         0         0           BL25         0         0         0         0         0         0         0         0                                                                                                                                                                               | BL17       | 1     | 1     | 1     | 1      | 0      | 0          | 0     | 0     | 0   | 4          |

| BL20         1         1         1         1         1         0         0         0         6           BL21         1         1         1         1         0         0         0         0         0         4           BL22         0         0         0         0         0         0         0         0         0         4           BL23         0         0         0         0         0         1         1         0         2           BL23         0         0         0         0         1         1         1         0         2           BL24         0         0         0         0         1         1         1         0         4           BL24         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                                                                     | BL18       | 0     | 0     | 0     | 0      | 0      | 0          | 0     | 0     | 0   | 0          |

| BL21         1         1         1         0         0         0         0         0         4           BL22         0         0         0         0         0         0         0         1         1         0         2           BL23         0         0         0         0         0         1         1         1         0         2           BL23         0         0         0         0         1         1         1         0         2           BL24         0         0         0         0         1         1         1         1         0         4           BL24         0         0         0         0         0         0         0         0         0         0         0         0           BL25         0         0         0         0         1         1         1         1         1         1         1         0         4           BL26         1         1         1         1         1         1         1         0         3         3           BL28         0         0         0         0         0                                                                                                                                                                               | BL19       | 0     | 0     | 0     | 0      | 1      | 1          | 1     | 1     | 0   | 4          |

| BL22         0         0         0         0         0         1         1         0         2           BL23         0         0         0         0         1         1         1         0         2           BL23         0         0         0         0         1         1         1         1         0         4           BL24         0         0         0         0         0         0         0         0         0         0         4           BL24         0         0         0         0         0         0         0         0         0         0         0         0         0         0           BL25         0         0         0         0         1         1         1         1         0         4           BL26         1         1         1         1         1         1         1         0         8           BL27         1         1         1         1         0         0         0         2           BL28         0         0         0         0         0         1         1         1         0                                                                                                                                                                               |            | 1     | 1     | 1     | 1      | 1      | 1          | 0     | 0     | 0   | 6          |

| BL23         0         0         0         0         1         1         1         1         0         4           BL24         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0 </td <td></td> <td>1</td> <td>1</td> <td>1</td> <td>1</td> <td>0</td> <td>0</td> <td>0</td> <td>0</td> <td></td> <td></td>       |            | 1     | 1     | 1     | 1      | 0      | 0          | 0     | 0     |     |            |

| BL24         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                             | BL22       | 0     | 0     | 0     | 0      | 0      | 0          | 1     | 1     | 0   | 2          |

| BL25         0         0         0         0         1         1         1         1         0         4           BL26         1         1         1         1         1         1         1         1         0         8           BL27         1         1         1         1         1         1         1         0         8           BL27         1         1         1         0         0         0         0         0         4           BL28         0         0         0         0         0         0         1         1         0         2           BL29         0         0         0         0         1         1         1         0         2           BL30         1         1         1         1         1         1         0         4           BL31         1         1         1         1         1         0         0         0         4                                                                                                                                                                                                                                                                                                                                                    |            | -     |       | 0     | -      | 1      | 1          | 1     | 1     |     | 4          |