# SIG102 - Multi I/O Control over DC Powerline Network

#### 1 Overview

The SIG102 transceiver device merges both data and power over the powerline, eliminating the need for control and data wires. Eight configurable I/Os ports can be configured as PWM output, Analog to digital converter (ADC) input, and digital I/Os. The SIG102 is a solution for multiple sensors and actuator networks over DC power lines.

The SIG102 is an economical device for applications as controlling motors or lights, reading sensors, etc., eliminating the need for dedicated control wires and a microcontroller (host ECU), reducing the harness size and increases reliability.

The device has a unique built-in byte-oriented UART multiplex signaling modem designed to overcome the powerline noisy conditions at bitrates up to 115.2Kbit/s. Sleep mode allows low power consumption when the device is not used. A SIG102 QFN48 (7x7 mm) package provides a small size PCB footprint (1)

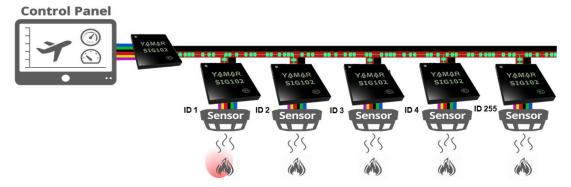

The SIG102 network consists of one SIG102 device operating as a master, controlled by any ECU via its UART port (HDI, HDO, and HDC pins). Up to 255 SIG102 devices can operate as slaves. When the device operates as a master (attached to ECU) it remotely controls other SIG102 Slaves IOs ports over the powerline and locally controls its ports.

Multiple networks can operate over the same powerline using selectable carrier frequencies between 5MHz and 30MHz in the spacing of 100 kHz.

## **Applications**

- Renewable energy Nano-Grid

- **Battery management (BMS)**

- **Climate control network**

- Sensors/actuators bus

- **Robotics control network**

- Lighting control

- Vehicle control networks

### Features

- Master controlling up to 255 I/O slaves

- Standalone slave with 8 configurable digital or analog I/O pine

- Noise robust communication network over DC powerline

- Selectable bitrate from 9.6kbit/s up to 115.2kbit/s

- Multiple networks may operate over a single powerline

- 251 selectable carrier frequencies (5MHz to 30MHz)

- Communicates over a wide range of DC voltages.

- Small footprint 48 pin QFN package

- Sleep modes for low power consumption

- I/O Watchdog protection

Figure 1 - SIG102 sensors actuators network

Tel: +972-3-5445294 Fax: +972-3-5445279 www.yamar.com

## **Table of Content**

| 1   | OVERVIEW                                                |    |  |  |

|-----|---------------------------------------------------------|----|--|--|

| 2   | DESCRIPTION                                             | 4  |  |  |

| 2.: | .1 The Signaling technology                             | 4  |  |  |

| 2.2 | .2 THE SIG102 NETWORK                                   | 4  |  |  |

| 2.3 | .3 DEVICE ARCHITECTURE                                  | 5  |  |  |

| 2.4 |                                                         |    |  |  |

| 2.  | .5 Implementation                                       | 8  |  |  |

| 3   | OPERATION                                               | 12 |  |  |

| 3.: |                                                         |    |  |  |

| 3.2 |                                                         |    |  |  |

| 3.  | .3 DEVICE CONFIGURATION                                 | 13 |  |  |

| 4   | SIG102 I/O PINS DESCRIPTION                             | 15 |  |  |

| 4.: | ,                                                       |    |  |  |

| 4.  | .2 DIGITAL IO                                           | 16 |  |  |

| 4.3 |                                                         |    |  |  |

| 4.4 | .4 ANALOG TO DIGITAL CONVERTER (ADC)                    | 18 |  |  |

| 5   | SIG102 I/OS SETTINGS AND CONTROL                        | 19 |  |  |

| 5.: | .1 I/Os local control                                   | 20 |  |  |

| 5.2 | .2 I/Os Remote slaves control (Commands over powerline) | 21 |  |  |

| 6   | POWER OPERATION MODES                                   | 24 |  |  |

| 6.: | .1 NORMAL MODE                                          | 24 |  |  |

| 6.2 |                                                         |    |  |  |

| 6.3 | .3 SLEEP MODES (POWER-SAVING)                           | 24 |  |  |

| 6.4 | .4 Auto Sleep mode                                      | 26 |  |  |

| 6.  | .5 SLEEP MODES EXAMPLES                                 | 27 |  |  |

| 7   | SIG102 CONTROL REGISTERS                                | 28 |  |  |

| 7.: | .1 REG_0 - 'Device Control 0' (Address 0x00)            | 28 |  |  |

| 7.3 | .2 REG_1 - 'Device Control 1' (Address 0x01)            | 28 |  |  |

| 7.3 |                                                         |    |  |  |

| 7.4 |                                                         |    |  |  |

| 7.  |                                                         |    |  |  |

| 7.0 | _ ' ' '                                                 |    |  |  |

| 7.  |                                                         |    |  |  |

| 7.8 | = ' ' ' ' ' ' ' ' ' ' ' ' ' ' ' ' ' ' '                 |    |  |  |

| 7.9 | =======================================                 |    |  |  |

|     | .10 REG_39 – UUID[31:24] (ADDRESS 0X39)                 |    |  |  |

|     | .11 REG_3A – UUID[23:16] (ADDRESS 0x3A)                 |    |  |  |

|     | .12 REG_SB = OUID[15.8] (ADDRESS 0XSB)                  |    |  |  |

|     | .14 REGISTERS CONFIGURATION (COMMAND MODE)              |    |  |  |

|     | SPECIFICATIONS                                          |    |  |  |

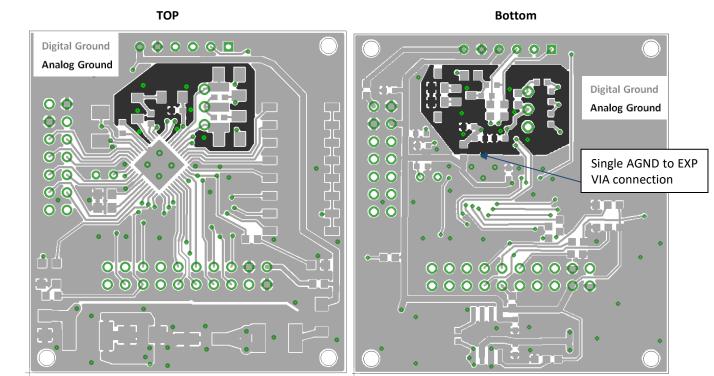

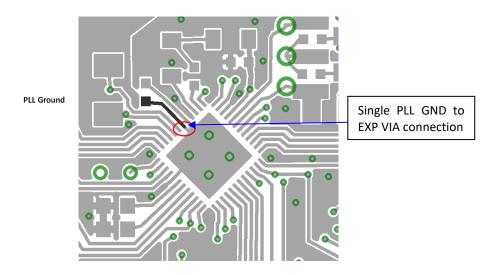

|     | SIG102 PCB LAYOUT RECOMMENDATION                        |    |  |  |

| 10  | PACKAGE, MECHANICAL                                     |    |  |  |

| _   | ·                                                       |    |  |  |

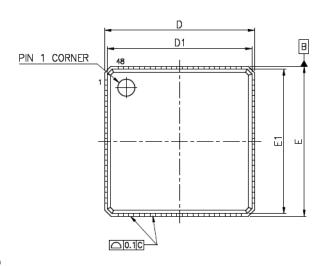

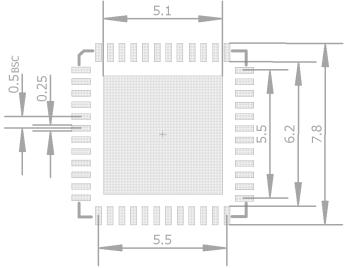

| _   | 0.1 Mechanical Drawing                                  |    |  |  |

| _   | 0.2 PCB Drawing                                         |    |  |  |

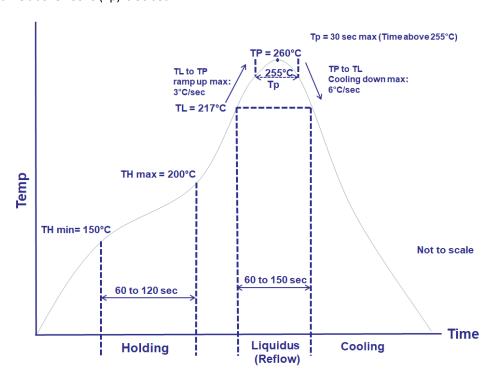

| ΤÚ  | U.J JULUINIU FRUFILE                                    |    |  |  |

Tel: +972-3-5445294 Fax: +972-3-5445279

## Data may be changed without notice - Proprietary information of Yamar Electronics Ltd.

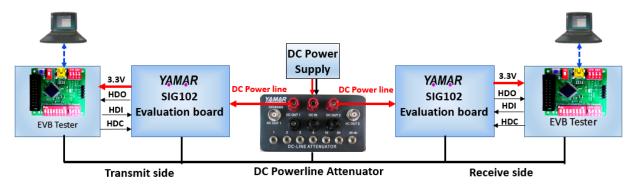

| 11   | TEST ENVIRONMENT    | 37   |

|------|---------------------|------|

|      |                     |      |

| 11.1 | COMMUNICATION TESTS | . 37 |

| 11.2 | REMOTE I/O TEST     | . 37 |

Tel: +972-3-5445294 Fax: +972-3-5445279

## 2 Description

The SIG102 is a multi I/O powerline transceiver device with a unique modem specially designed for economical communication over a noisy DC powerline. The device has eight configurable input/output pins operating as ADC inputs, PWM outputs, and digital I/O. All eight I/O pins can be controlled remotely from a master SIG102 device over a DC powerline or locally by a host ECU's UART port using HDI, HDO, and HDC pins.

A Sleep mode reduces significantly the power consumption when there is no need for communication over the powerline.

### 2.1 The Signaling technology

SIG102 communication is based on a unique Signaling technology. The device transmits and receives UART bytes; modulate it by a multiphase signaling carrier over the powerline. At the receiving side, this phase-modulated pattern is extracted from the powerline and decoded back as UART bytes. There is no restriction to the number of bytes (message size).

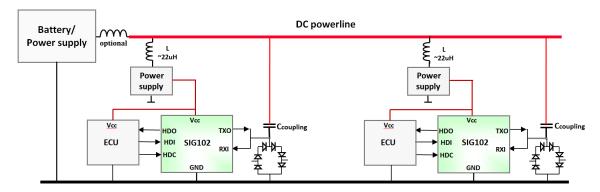

#### 2.2 The SIG102 network

The SIG102 operates as a Master-Slaves network of multiple SIG102 devices over a selectable carrier frequency between 5MHz and 30MHz with 100 kHz spacing. Multiple independent networks may operate over the same powerline by selecting different carrier frequencies for each network. It is recommended to keep at least 1MHz spacing between two carriers (networks).

Two alternate frequencies are pre-defined for fast hoping using FREQ\_SEL[1:0] pins when the communication fails on the main frequency. The main operating frequency and two alternative frequencies are set by dedicated registers described in section 3.3.2.

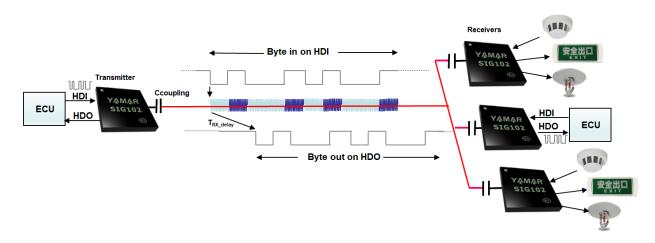

Figure 2 depicts a typical SIG102 network consists of one SIG102 master device which remotely controls sensor and actuators attached to SIG102 slave devices. Also, the master SIG102 device can transfer and receive data to/from a slave SIG102 device attached also to an ECU. Figure 2 demonstrating a single powerline *byte-field* transmission from SIG102 TX device to three SIG102 RX devices coupled through C<sub>coupling</sub> to the same powerline. Upon detection start bit on SIG102 TX device HDI, a powerline *byte-field* transmission begins. After fix latency of T<sub>RX</sub> delay, the powerline *byte-field* is decoded and digitally output on SIG102 RX devices' HDO.

Figure 2 – SIG102 typical network

### 2.2.1 SIG102 channel parameters

Carrier frequency: 251 selectable frequencies between 5MHz - 30MHz with 100 kHz spacing. Powerline bitrate: 9.6kbit/s, 10.4bit/s, 19.2Kbit/s, 38.4Kbit/s, 57.6kbit/s, and 115.2kbit/s.

Powerline voltage: Any, with proper powerline coupling interfacing (see 2.5.8)

Cable length: Depends on the powerline loads AC signal-attenuation (100m is practicable)

Cable type: Any cable.

DS-SIG102 R 0.90

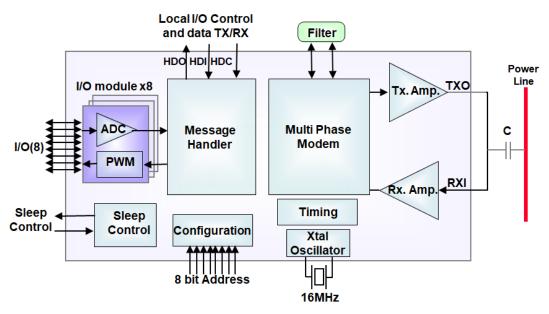

### 2.3 Device Architecture

Figure 3 depicts the SIG102 blocks.

Figure 3- SIG102 Logical Blocks

The SIG102 main building blocks:

- Message handler Interface with UART/LIN ECU.

- IOs controller Control IOs configuration and status.

- Multi-Phase Modem Phase modulates and demodulates the data to and from the DC-BUS powerline.

- Sleep control Ensures low power consumption during Sleep mode.

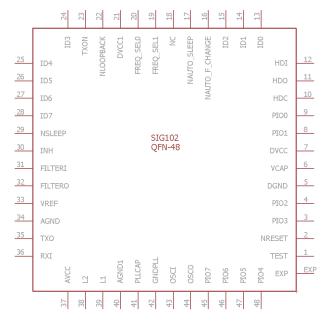

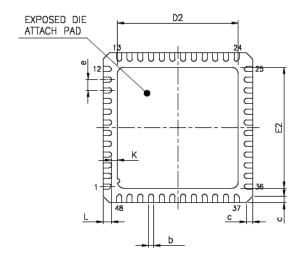

## 2.4 Pin configuration and function

Figure 4 - SIG102 pinout diagram in QFN48 7x7 mm package

## 2.4.1 Signals and Pinout description

Table 1 - Pinout description

|              | 1     | T               |                   | Pinout description                                   |                            |                     |         |

|--------------|-------|-----------------|-------------------|------------------------------------------------------|----------------------------|---------------------|---------|

| Name         | Pin # | Pin type        | Internal<br>PU/PD | Description                                          |                            |                     |         |

|              |       |                 |                   | Outputs the received data from the powerline or from |                            |                     |         |

| HDO          | 11    | Output 12mA     |                   | internal registers to the host.                      |                            |                     |         |

|              |       | -               |                   | Transfers data fro                                   | m the host to the          | powerline           | or the  |

| HDI          | 12    | Digital input   | PU                | internal registers.                                  |                            | •                   |         |

|              |       |                 |                   | Host ECU Data / Co                                   | mmand input. When          | n low, enabl        | es read |

|              |       |                 |                   |                                                      | he SIG102 control re       |                     |         |

| HDC          | 10    | Digital input   | PU                | 7.14).                                               |                            |                     |         |

| TEST         | 1     | Digital Input   | PD                | Should be connecte                                   | d to GND.                  |                     |         |

| NRESET       | 2     | Digital Input   | PU                | Reset, active low.                                   |                            |                     |         |

|              |       |                 |                   | Sleep mode control                                   | input (see section 6.      | 3).                 |         |

| NSLEEP       | 29    | Digital Input   |                   |                                                      | 3.3V when not in us        |                     |         |

|              |       |                 |                   | When low, the SIG                                    | 102 will automatical       | ly hop betwo        | een the |

| NAUTO_F      |       |                 |                   |                                                      | ncy and two alterna        |                     |         |

| _CHANGE      | 16    | Digital Input   |                   | 3.3.3).                                              | •                          | ·                   | -       |

|              |       |                 |                   | When low, the SIG1                                   | LO2 will automaticall      | y enter Slee        | p mode  |

|              |       |                 |                   |                                                      | Transmission or rec        |                     |         |

|              |       |                 |                   | powerline for mor                                    | e than <i>AutoSleep-ti</i> | meout setti         | ng (see |

| NAUTO_SLEEP  | 17    | Digital Input   |                   | 6.4).                                                |                            |                     |         |

| NC           | 11    |                 |                   | Should be left floate                                | ed.                        |                     |         |

|              |       |                 |                   | When high, loopba                                    | ack from HDO to H          | DI is disable       | ed (see |

| NLOOPBACK    | 22    | Digital Input   | PU                | 3.3.4)                                               |                            |                     |         |

|              |       | Digital Output  |                   | When high, SIG102 is in Normal mode                  |                            |                     |         |

| INH          | 30    | 8mA             |                   | When low, SIG102 is                                  |                            |                     |         |

| FREQ_SEL0    | 20    | Digital Input   |                   | Main and 2 alternat                                  | e frequencies selecti      | on control.         |         |

| <del>-</del> |       |                 |                   | FREQ_SEL[1:0]                                        | Default Frequency          |                     |         |

|              |       |                 |                   |                                                      | [MHz]                      |                     |         |

|              |       |                 |                   | '00','11'<br>'01'                                    | 13<br>5                    | Main<br>Alternate 1 |         |

|              |       |                 |                   | '10'                                                 | 22                         | Alternate 2         |         |

| FREQ_SEL1    | 19    | Digital Input   |                   | see 3.3.2                                            |                            |                     | J       |

| <del>-</del> |       |                 |                   | TX ON output - Hig                                   | h when transmission        | onto the po         | werline |

| TXON         | 23    | Output 12mA     |                   | is active.                                           |                            | •                   |         |

| PIO0         | 9     | ADC In/ Digital | PD (digital       |                                                      |                            |                     |         |

|              |       | In/Output       | Input only)       |                                                      |                            |                     |         |

|              |       | PWM 12mA        | , ,,              | Device I/O pin 0, de                                 | fault set as digital inp   | out.                |         |

| PIO1         | 8     | ADC In/ Digital | PD (digital       | •                                                    | <u> </u>                   |                     |         |

|              |       | In /Output      | Input only)       |                                                      |                            |                     |         |

|              |       | 12mA            |                   | Device I/O pin 1, de                                 | fault set as digital inp   | out.                |         |

| PIO2         | 4     | ADC In/ Digital | PD (digital       |                                                      |                            |                     |         |

|              |       | In/Output       | Input only)       |                                                      |                            |                     |         |

|              |       | PWM 12mA        |                   | Device I/O pin 2, de                                 | fault set as digital inp   | out.                |         |

| PIO3         | 3     | ADC In/ Digital | PD (digital       |                                                      |                            |                     |         |

|              |       | In/Output       | Input only)       |                                                      |                            |                     |         |

|              |       | PWM 12mA        |                   | Device I/O pin 3, default set as digital input.      |                            |                     |         |

| PIO4         | 48    | ADC In/ Digital | PD (digital       |                                                      |                            |                     |         |

|              |       | In/Output       | Input only)       |                                                      |                            |                     |         |

|              |       | PWM 12mA        |                   | Device I/O pin 4, default set as digital input.      |                            |                     |         |

| PIO5         | 47    | ADC In/ Digital | PD (digital       |                                                      |                            |                     |         |

|              |       | In/Output       | Input only)       |                                                      |                            |                     |         |

|              |       | PWM 12mA        |                   | Device I/O pin 5, de                                 | fault set as digital inp   | out.                |         |

| PIO6         | 46    | ADC In/ Digital | PD (digital       |                                                      |                            |                     |         |

|              |       | In/Output       | Input only)       |                                                      |                            |                     |         |

|              |       | PWM 12mA        |                   | Device I/O pin 6, de                                 | fault set as digital inp   | out.                |         |

Tel: +972-3-5445294 Fax: +972-3-5445279

|          |              |                     | Internal    |                                                                          |  |  |

|----------|--------------|---------------------|-------------|--------------------------------------------------------------------------|--|--|

| Name     | Pin #        | Pin type            | PU/PD       | Description                                                              |  |  |

| PIO7     | 45           | ADC In/ Digital     | PD (digital | ·                                                                        |  |  |

|          |              | In/Output           | Input only) |                                                                          |  |  |

|          |              | PWM 12mA            |             | Device I/O pin 7, default set as digital input.                          |  |  |

| ID0      | 13           | Digital Input       | PD          | Device address bit [0]                                                   |  |  |

| ID1      | 14           | Digital Input       | PD          | Device address bit [1]                                                   |  |  |

| ID2      | 15           | Digital Input       | PD          | Device address bit [2]                                                   |  |  |

| ID3      | 24           | Digital Input       | PD          | Device address bit [3]                                                   |  |  |

| ID4      | 25           | Digital Input       | PD          | Device address bit [4]                                                   |  |  |

| ID5      | 26           | Digital Input       | PD          | Device address bit [5]                                                   |  |  |

| ID6      | 27           | Digital Input       | PD          | Device address bit [6]                                                   |  |  |

| ID7      | 28           | Digital Input       | PD          | Device address bit [7]                                                   |  |  |

|          |              |                     |             | Powerline Transmit signal out                                            |  |  |

| l        |              |                     |             | TXON REG_1[4] TX level Impedance $[\Omega]$                              |  |  |

|          |              |                     |             | State   [V-p-p]                                                          |  |  |

|          |              |                     |             | '1' (Default) 2                                                          |  |  |

|          |              |                     |             | Low High Z 5.3k <sup>2</sup>                                             |  |  |

|          |              | Analog Output       |             | <sup>1</sup> Series output impedance                                     |  |  |

| TXO      | 35           | Max 66 mA           |             | <sup>2</sup> Input impedance referenced to VREF                          |  |  |

| RXI      | 36           | Analog Input        |             | Powerline receive Input                                                  |  |  |

|          |              |                     |             | Analog out reference VCC/2 for filtering capacitor. Place                |  |  |

|          |              |                     |             | 1uF between VREF to AGND. The VREF is used as a virtual                  |  |  |

| VREF     | 33           | Analog Output       |             | ground for the external analog circuitry.                                |  |  |

|          |              | Analog,             |             |                                                                          |  |  |

| FILTERI  | 31           | Bi-directional      |             | External filter I/O                                                      |  |  |

| FILTERO  | 22           | Analog,             |             | Futamal filtar I/O                                                       |  |  |

| FILTERO  | 32           | Bi-directional      |             | External filter I/O                                                      |  |  |

| OSCO     | 44           | Analog output       |             | 16MHz Crystal Japant                                                     |  |  |

| OSCI     | 43           | Analog Input        |             | 16MHz Crystal Input                                                      |  |  |

| L1       | 39           | Analog Input        |             | External inductor L1 (pin capacitance should be maximal 1pF), see 2.5.4. |  |  |

| L2       | 38           | Analog Input        |             | External inductors L2 (optional), see 2.5.4.                             |  |  |

| AVCC     | 37           | Power               |             | Analog 3.3V supply                                                       |  |  |

| AGND     | 40,34        | Power               |             | Analog ground                                                            |  |  |

| AGIVD    | 40,34        | TOWE                |             | 1.8V core supply output for filtering capacitor. Place 4.7uF             |  |  |

| VCAP     | 6            | Power               |             | between VCAP and DGND.                                                   |  |  |

| DGND     | 5            | Power               |             | Digital Ground                                                           |  |  |

| DVCC     | 21,7         | Power               |             | Digital 3.3V supply                                                      |  |  |

| GNDPLL   | 42           | Power               |             | Analog Ground                                                            |  |  |

| JIIDI LL | 72           | 1 0 1 1 1           |             | PLL 1.8V output to a filtering capacitor. Place 1uF between              |  |  |

| PLLCAP   | 41           | Power               |             | PLLCAP and GNDPLL.                                                       |  |  |

| EXP      |              | Power               |             | Expose pad, should be connected to DGND.                                 |  |  |

|          | II dama rasi | stor 50K ohm +/-%30 | 1           |                                                                          |  |  |

PD – Internal Pull-down resistor 50K ohm +/-%30

PU – Internal Pull-up resistor 50K ohm +/-%30

Tel: +972-3-5445294 Fax: +972-3-5445279

## 2.5 Implementation

## 2.5.1 SIG102 reference schematic

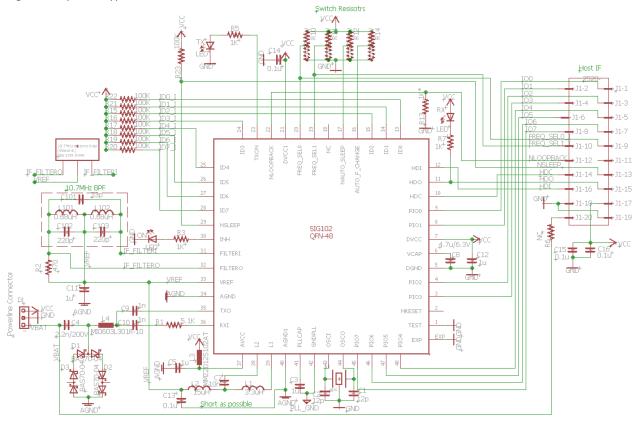

Figure 5 depicts a typical SIG102 schematic.

Figure 5 – SIG102 reference schematic

## 2.5.2 External 10.7MHz filter (BPF)

The SIG102 operates using an external 10.7MHz narrow bandpass filter. The minimum recommended filter bandwidth is 330 kHz @ 3dB. Narrower bandwidth limits the maximal SIG102 bitrate. Figure 6 depicts the recommended 10.7MHz discrete filter.

Figure 6- 10.7MHz discrete bandpass filter

Alternatively, Table 2 describes the recommended 10.7MHz ceramic filters.

| Tahla 2 - | - Recommen | 464 10 7MHz   | ceramic filters |

|-----------|------------|---------------|-----------------|

| Table 2 - | - Recommen | ueu to./ivinz | cerannic inters |

| Manufacturer | Part #       | 3dB BW | Insertion | Stopband    | In/Out | Package |

|--------------|--------------|--------|-----------|-------------|--------|---------|

|              |              | [KHz]  | loss      | attenuation | imped. |         |

|              |              | min.   | [dB] max. | [kHz]       | [Ω]    |         |

| <u>AEC</u>   | LTCV10.7MA19 | 350    | 3.0       | 950         | 470    | SMD     |

| Strong-First | LTCV10.7MA20 | 330    | 3.0       | 680         | 330    | SMD     |

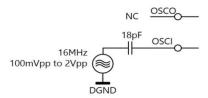

#### 2.5.3 **External Crystal**

The device operates with a low cost, small size 16MHz crystal connected between OSCI and OSCO pins. Each of these pins should be connected to the DGND via a load capacitor. The load capacitors values should be determined according to the crystal manufacturer's recommendations and the actual PCB layout. The PCB traces should be as short as possible.

The overall frequency tolerance should not exceed ± 50ppm.

### **Recommended crystals:**

- O NDK NX2520SA-16MHz, SMD, 2.5x2 mm

- o NDK NX3225SA/GB-16MHz, SMD, 3.2x2.5mm

- NDK NX2016GC-16MHz, SMD, 2.0x1.6mm

- ECS ECS-160-12-37B-CTN-TR, SMD, 2.0x1.6mm

#### 2.5.3.1 16MHz clock from an external source

The device can operate from an external 16HMz clock that meets the requirements above.

Figure 7 depicts an external 16MHz clock connection to the device.

Figure 7 - External 16MHz clock connection

#### L1 and L2 inductors

The SIG102 requires one or two inductors for its operation, depending on the desired operating frequency.

- For full in-band operation, 5MHz 30MHz:

- ▶ L1 3.3uH

- ➤ L2 15uH with 10nF series capacitor between L2 pin and L2 inductor.

- For low in-band operation, 5MHz -12MHz:

- L1 18uH

- ➤ L2 NC

- For high in-band operation, 12MHz 30MHz:

- ➤ L1 3.3uH

- ➤ L2 NC

Figure 8 depicts the in-band operation inductors' connection to pins L1 and L2.

Full in-band selection High or low in-band selection L1 18uH (5-12MHz)

Figure 8 - L1 and L2 inductors connections

#### 2.5.4.1 Recommended L1 & L2 inductors

Table 3 describes the recommended L1 and L2 inductors.

Table 3 - Recommended L1 and L2 manufacturers

| Inductor | ABRACON              | VISHAY         | TDK              |

|----------|----------------------|----------------|------------------|

| L1=3.3uH | 815-AIML-0805-3R3K-T | ILSB0805ER3R3K | MLF2012A3R3JT000 |

| L2=15uH  | 815-AIML-0805-150K-T | ILSB0805ER150K | MLF2012C150KT000 |

| L1=18uH  | 815-AIML-0805-180K-T | ILSB0805ER180K | MLF2012C180KT000 |

#### 2.5.5 Optional EMC chip-bead (L4)

For enhanced mitigation of high harmonics above 30MHz conducted over the powerline, it is recommended to add L4 in series to the coupling capacitor C4 (see Figure 5).

Table 4 describes the recommended EMC chip-beads.

Table 4 - Recommended L4 (optional)

| idole + Necommended E+ (optional |                |  |  |  |  |  |

|----------------------------------|----------------|--|--|--|--|--|

| LAIRD                            | MI0603L301R-10 |  |  |  |  |  |

| LAIRD                            | HZ0603A222R-10 |  |  |  |  |  |

| TDK                              | MMZ1608Q       |  |  |  |  |  |

#### 2.5.6 **Ceramic capacitors**

Low ESR capacitors will provide better performance. X5R and X7R capacitors are recommended, especially for VCAP (C8) and PLLCAP (C3).

#### 2.5.7 TXO output level and drive control

The TXO pin output level and drive capability to the powerline are controlled by REG 1/4, as described in Table 5.

Table 5 - TXO signal level

| TXON State | REG_1[4]      | TX level [V-p-p] |

|------------|---------------|------------------|

| High       | '0'           | 1                |

|            | '1' (Default) | 2                |

| Low (Rx)   |               | High Z           |

Set the TXO output drive capability by configuring REG\_1[7], as described in Table 6.

Table 6- TXO output drive control

| TXON State | REG_1[7]      | Output drive [A] | Impedance [Ω]     |

|------------|---------------|------------------|-------------------|

| High       | '0' (Default) | 33mA             | 18 ¹              |

|            | '1'           | 66mA             |                   |

| Low (Rx)   |               | Disabled         | 5.3k <sup>2</sup> |

<sup>&</sup>lt;sup>1</sup>Series output impedance

© 2020-2023 Yamar Electronics Ltd. www.yamar.com

Tel: +972-3-5445294 Fax: +972-3-5445279

<sup>&</sup>lt;sup>2</sup>Input impedance referenced to VREF

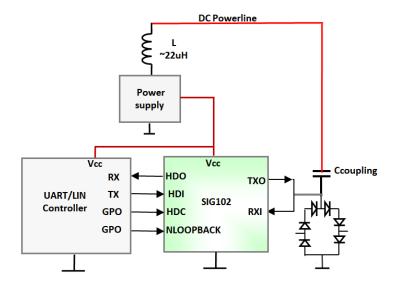

### 2.5.8 Powerline coupling interface

The SIG102 is coupled to the powerline through a single small footprint DC blocking ceramic capacitor, typically 2.2nF. The C<sub>coupling</sub> voltage rating depends on the powerline voltage and its expected impulses.

For high voltage powerline applications (e.g. battery monitoring system in EV or solar panels), it is required to add galvanic isolation.

#### 2.5.9 External protection network

A simple external diode protection network is recommended before the C<sub>coupling</sub>, to protect against high powerline pulses (above 2 V-P-P). The protection network consists of three low capacitance (< 10pF) fast Schottky diodes serially connected in both polarities (e.g. BAS70-04).

## 2.5.10 Recommended connection to power-supply

Power-supplies have filtering capacitors in their DC inputs. These capacitors attenuate strongly the SIG102 carrier signal. It is recommended to add an inductor (>22uH) or ferrite bead (>100 $\Omega$  @ 5MHz-30MHz) in series to the power supply connection to the DC powerline to reduce the carrier signal attenuation.

Figure 9 depicts a typical SIG102 connection to a DC powerline and its 3.3V power supply.

Figure 9 - SIG102 connection to 3.3V power-supply and powerline

## 3 Operation

## 3.1 Interfacing to UART/LIN ECU

The SIG102 interfaces directly to any uC UART/LIN I/O pins (3.3V logic).

The UART/LIN communication protocol uses four pins as described in Table 7.

### Table 7 - UART/LIN interface pins

| SIG102                                           | 2 ECU Description |                                                                                                                                                                        |

|--------------------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HDI                                              | Tx                | Data Input from the host ECU.                                                                                                                                          |

| HDC                                              | GPO               | Data/Command select input. When pulled down, the SIG102 enters command mode,                                                                                           |

|                                                  |                   | enabling access to SIG102 internal registers.                                                                                                                          |

| HDO Rx Data output to the host ECU.              |                   | Data output to the host ECU.                                                                                                                                           |

| NLOOPBACK GPO Enable loopback of HDI to HDO pin. |                   | Enable loopback of HDI to HDO pin.                                                                                                                                     |

| - When interfacing a UART port, ECU may disab    |                   | <ul><li>When interfacing a UART port, ECU may disable/enable the loopback option.</li><li>When interfacing a LIN ECU, tie pin to GND. HDI loops back to HDO.</li></ul> |

Figure 10 depicts a typical SIG102 to UART/LIN ECU interface connection.

Figure 10 - Typical SIG102 to UART ECU interface

### 3.2 SIG102 messages

## 3.2.1 Message structure

The SIG102 message structure contains the following:

- A byte-field (UART byte) is defined with one start bit, 8 data bits, and one stop bit.

- A *PLC-byte* is defined as the signaling pattern of the *byte-field* over the powerline.

- A break-field is defined as one start bit, 12 to 30 zero bits, and one stop bit.

- A PLC-break is defined as the signaling pattern of the break-field over the powerline

The SIG102 is a byte-oriented powerline transceiver. Each UART/LIN byte-field on the HDI pin is encoded into a modulated powerline *PLC-byte* at the length of the ECU UART bitrate. At the receiving side, each *PLC-byte* is decoded back after a fixed delay of ~2.5T<sub>bit</sub> to the HDO byte-field. A break-field at the beginning of a message is handled the same.

## 3.2.2 Transmit flow

Upon detection of a start bit on HDI, the SIG102 starts its byte-field/break-field transmission over the powerline until receiving a stop bit from ECU. In case of ECU transfers bytes continuously (i.e. inter-byte spacing between bytes < 1/3 T<sub>bit</sub>), the SIG102 will not stop its transmission. If the inter-byte space is longer than 1/3 T<sub>bit</sub>, the SIG102 will stop its transmission over the powerline and will wait for the next start bit.

DS-SIG102 R 0.90

#### 3.2.3 Receive flow

Upon detection of a powerline *PLC-byte/PLC-break*, the SIG102 will decode the *PLC-byte* and transfer the *byte-field* to the receiving ECU's HDO pin (a start bit followed by the data bits and stop bit).

The delay (i.e. powerline latency) between Transmitter start bit drop on HDI to Receiver start bit drop is  $T_{RX\_delay} = \sim 2.5 T_{bit}$ .

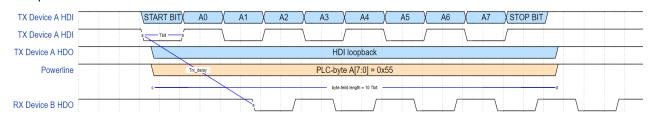

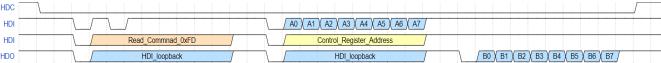

Figure 11 depicts a single byte-field -> PLC-byte -> byte-field TX-RX flow. ECU A transfers 0x55 byte-field on HDI with local loopback feedback on HDO (loopback is enabled). Upon start bit detection, a powerline transmission of PLC-byte 0x55 (length of 10 x T<sub>bit</sub>), begins. Then, after T<sub>RX\_delay</sub> of ~2.5 T<sub>bit</sub>, the PLC-byte is extracted on RX device B HDO pin to its ECU.

Figure 11 - SIG102 single PLC-byte TX-RX example

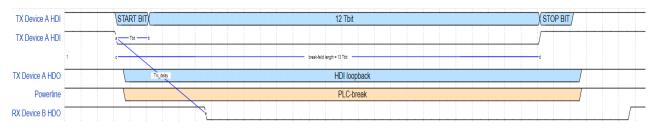

Figure 12 depicts a single *break-field* TX-RX flow. ECU transfers a *break-field* on HDI with local loopback feedback on HDO (loopback is enabled). Upon start bit detection, a powerline transmission of *PLC-break* (length of 13 x  $T_{bit}$ ), begins. Then, after  $T_{RX\_delay}$  of ~2.5  $T_{bit}$ , the *break-field* is extracted on RX device B HDO to its ECU.

Figure 12 - SIG102 single break-field TX-RX example

## 3.3 Device configuration

## 3.3.1 Bitrate configuration

Table 8 describes the SIG102 supported bitrate selection.

Bitrate configuration is made by setting REG\_0[2:0] bits using the WRITE-REG command (see 7.14).

| REG_0            | Bitrate [bit/s] | Host Nominal T <sub>bit</sub> | SIG100 HDO T <sub>bit</sub> |  |  |  |

|------------------|-----------------|-------------------------------|-----------------------------|--|--|--|

| Bitrate_sel[2:0] |                 | ~ [µs]                        | ~ [µs]                      |  |  |  |

| 000              | 9600            | 104                           | 103.8                       |  |  |  |

| 001              | 10417           | 96                            | 95.8                        |  |  |  |

| 010              | 19200 (default) | 52                            | 51.9                        |  |  |  |

| 011              | 38400           | 26                            | 25.8                        |  |  |  |

| 100              | 57600           | 17.36                         | 17.38                       |  |  |  |

| 101              | 115200          | 8.68                          | 8.41                        |  |  |  |

Table 8 - Bitrate selection

### 3.3.2 Carrier frequency management

The SIG102 operates on its configured main frequency. Two alternate frequencies (ALT1 and ALT2) are available for frequency hopping in case that the operating frequency is blocked by interference.

The active working frequency is determined by FREQ\_SEL[1:0] hardware pins setting. For each change in FREQ\_SEL[1:0] pins, the SIG102 will switch to the selected carrier frequency (Main/ALT1/ALT2) according to Table 9 mapping.

Set the Main/ALT1/ALT2 frequencies by configuring REG\_2/ REG\_3/ REG\_4 respectively (see 7).

© 2020-2023 Yamar Electronics Ltd. www.yamar.com

For each configuration of REG\_2, the active frequency is automatically switched to the Main frequency (as set in REG\_2), regardless of FREQ\_SEL[1:0] pins set. Switching to ALT1/ALT2 again will take place only at the next change of FREQ SEL[1:0] pins.

ECU may read the active operating carrier frequency value stored in read-only REG 5.

Table 9 describes the carrier frequency setting and control.

Table 9 - Carrier frequency setting and control

| Carrier Frequency | FREQ_SEL[1:0] | Register name | Default Frequency<br>[MHz] |

|-------------------|---------------|---------------|----------------------------|

| Main              | '00','11'     | REG_2[7:0]    | 13                         |

| ALT1              | '01'          | REG_3[7:0]    | 5                          |

| ALT2              | '10'          | REG_4[7:0]    | 22                         |

#### 3.3.2.1 **Carrier frequency configuration**

ECU can define carrier frequency from 5MHz to 30MHz with a spacing of 100 kHz (Total of 251 selectable carriers). Upon completion of configuration or change of FREQ\_SEL[1:0] pins, the SIG102 will update its operating carrier frequency within a 1msec period. During this period, the SIG102 is kept in Soft-Reset and will not communicate with its ECU nor detect new messages from the powerline and no other internal register configuration is allowed. It is recommended to place the carrier frequency configuration last during multiple registers configuration and wait at least 1ms after HDC is released.

When multiple SIG102 networks operate over a single powerline, it is recommended to select their carrier frequencies spaced more than 1MHz between each other.

The carrier-selected value is calculated as given in the Definition of equation (1).

### **Definition of equation**

$$REG_2/3/4 = (Carrier Freq. [MHz] - 5) * 10$$

(1)

#### **EXAMPLE 1**

When setting the frequency to 14.1MHz:  $REG_2/3/4 = (14.1 - 5) * 10 = 0x5B$

## **EXAMPLE 2**

❖ When Setting to 5MHz:  $REG_2/3/4 = (5 - 5) * 10 = 0x00$

#### 3.3.3 Auto frequency change mode

The Auto frequency change mode is enabled either by pull the NAUTO\_F\_CHANGE pin low or by clearing REG\_0[3]

When enabled, the SIG102 automatically hops between Main, ALT1, or ALT2 configured frequencies when no powerline PLC-byte activity detected more than 1 sec. It indicates that neither transmission nor reception is detected over the powerline.

The hopping method is as follows:

#### 3.3.4 Loopback

LOOPBACK between HDI and HDO is required when interfacing to a LIN ECU. Loopback has to be disabled when interfacing with a LIN transceiver (see 3.1).

Loopback is enabled either by pull the LOOPBACK pin low or by clearing REG 0[5]. The last action prevails.

#### 3.3.5 Remote loopback mode

The remote loopback function, when enabled, triggers the receiving SIG102 to transmit-back its last received powerline PLC-byte over the powerline. This function is useful in point to point communication between two SIG102 devices as part of the ECU built-in ACK/NACK mechanism. For example, the checksum byte at the end of a message is returned to the transmitting Master to validate the integrity of the received message by the Slave.

14 DS-SIG102 R 0.90 Tel: +972-3-5445294 Fax: +972-3-5445279 www.yamar.com

Remote loopback mode is enabled by setting  $REG_0[4]$ . The SIG102 RX device will respond only when the powerline is idle for at least 3 x  $T_{bit}$  times after full reception of the last byte.

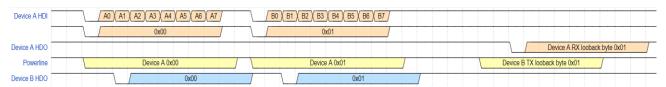

Figure 13 depicts an example of a remote loopback operation. ECU A transfers two data bytes [0x00][0x01] that are transmitted over the powerline to ECU B. Upon detecting the last transmitted 0x01 byte, SIG102 device B waits for 3 x T<sub>bit</sub> time before automatically transmit-back 0x01 over the powerline to device A.

Figure 13 - Remote loopback example

#### 3.3.6 SIG102 UUID

Each SIG102 device is hard-coded with a 48 bit universally unique identifier (UUID[47:0]).

The UUID is stored in REG\_37 to REG\_3C and can be retrieved using the READ-REG commands (see 7.8 to 7.13 7.13).

### 3.3.7 Typical set-up and operation example

- 1. Interface HDI, HDO, and HDC pins to the host ECU.

- 2. Enable/disable loopback of HDI pin to HDO pin (see 3.3.4).

- 3. Select SIG102 bitrate according to ECU UART/LIN bitrate (see3.3).

- 4. Select a carrier frequency (default 13MHz) (see 3.3.2).

- 5. Transmit bytes via HDI pin to the powerline.

- 6. Receive bytes from the powerline via HDO pin.

## 4 SIG102 I/O Pins Description

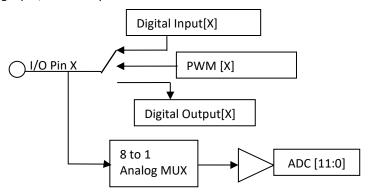

The SIG102 has eight configurable I/O pins that can be configured individually to either digital Input (default) /digital output /analog input/ PWM output.

Figure 14 - I/O pins Block diagram

## 4.1 I/O Pins Configuration

Each I/O can be configured to be either Digital Input / Output, ADC Input, or PWM output. All I/Os is default configured as Digital Inputs, with internal pull-down.

## 4.1.1 REG\_21 - 'I/O Direction' (Address 0x21)

| Bit 7     | Bit 6     | Bit 5     | Bit 4     | Bit 3     | Bit 2     | Bit 1     | Bit 0     |

|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| R/W [1]   |

| IO 7      | 10 6      | IO 5      | IO 4      | IO 3      | IO 2      | IO 1      | 10 0      |

| direction |

Bit [7:0] - IO direction control.

Default all IO set as Input pins.

### 4.1.2 REG\_22 - 'I/O Functionality' (Address 0x22)

| Bit 7    | Bit 6    | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| R/W [0]  |

| IO 7     | IO 6     | IO 5     | IO 4     | 10 3     | IO 2     | IO 1     | 10 0     |

| function |

Bit [7:0] - IO Functionally control.

Default all IO set as digital pins.

| I/O Pin       | 7       | 6         | 5       | 4       | 3       | 2       | 1          | 0      |

|---------------|---------|-----------|---------|---------|---------|---------|------------|--------|

| Configuration | Digital | ADC Input | Digital | Digital | Digital | Digital | PWM Output | PWM    |

|               | Input   |           | Input   | Input   | Output  | Output  |            | Output |

For example, writing '0xF0' and '0x43' to REG 21 and REG 22 respectively, configures the I/Os the following way:

## 4.1.3 REG\_23 - 'IO Watchdog Control' (Address 0x23)

| Bit 7    | Bit 6    | Bit 5    | Bit 4    | Bit 3    | Bit 2   | Bit 1      | Bit 0   |

|----------|----------|----------|----------|----------|---------|------------|---------|

| R        | R        | R        | R        | R        | R/W [0] | R/W [0]    | R/W [0] |

| Reserved | Reserved | Reserved | Reserved | Reserved | IO Wato | chdog time | r[2:0]  |

Bit[2:0] - Set the IO Watchdog timer duration in seconds. If the Watchdog timer is enabled, the SIG102 will power down its outputs if it didn't receive any data from the powerline nor from its host (if connected) for the defined period. Default this feature is disabled.

Bit[7:3] -Reserved.

R - Readable bit, W - Writeable bit [x] - Value on power-up. '1' - bit is set; '0' - bit is cleared

### 4.2 Digital IO

The SIG102 eight IOs can be set as digital input or outputs (CMOS 3.3V). Setting or reading digital IOs is made through REG\_24.

## 4.2.1 REG\_24 - 'Digital IO' (Address 0x24)

The 'Digital IO' register write operation sets the IO configured as digital output correspondingly.

The 'Digital IO' register read operation responds with the current state of the IO (if configured as digital input or output (latch)).

<sup>\*\*</sup> Note - For IO that is configured as analog or PWM, the read value will always return '0'.

| Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| R/W [0] |

| 10 7    | 10 6    | IO 5    | IO 4    | IO 3    | 10 2    | IO 1    | 10 0    |

Bit[7:0] – Set value for IO X as output, Read value of IO X as digital input or Output (latch).

#### **EXAMPLE 3**

Preform WRITE-REG to REG\_24 with the value of 0x55 results in IO 3 output logical '0' and IO 2 output logical '1'. By default all digital inputs are PD. Assume IO 7 is externally PU.

Preform READ-REG to REG 24, the SIG102 responds with byte 0x84.

DS-SIG102 R 0.90

<sup>&#</sup>x27;1' set IO as an Input pin

<sup>&#</sup>x27;0' set IO as an output pin.

<sup>&#</sup>x27;1' set IO as Analog or PWM pin

<sup>&#</sup>x27;0' set IO as a digital pin.

| I/O Pin       | 7       | 6     | 5       | 4       | 3       | 2       | 1      | 0      |

|---------------|---------|-------|---------|---------|---------|---------|--------|--------|

| Configuration | Digital | ADC   | Digital | Digital | Digital | Digital | PWM    | PWM    |

|               | Input   | Input | Input   | Input   | Output  | Output  | Output | Output |

| REG_24        | 0       | 1     | 0       | 1       | 0       | 1       | 0      | 1      |

| WRITE VALUE   |         |       |         |         |         |         |        |        |

| REG_24        | 1       | 0     | 0       | 0       | 0       | 1       | Always | Always |

| READ VALUE    |         |       |         |         |         |         | '0'    | '0'    |

#### 4.3 **PWM Outputs**

The SIG102 IOs can be set up to eight PWM channels with an 8 bits resolution.

All the PWM channels share the same selectable PWM frequency, between 31.37 kHz (~32uS PWM cycle) down to 122.5Hz (~8ms PWM cycle).

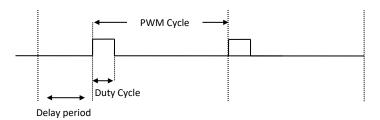

For each channel, the time that the PWM output is high during a PWM cycle (duty cycle) is configured using the PWM DUTY X register, where X is the PWM channel number. In addition, an 8-bit resolution referenced delay period can also be configured using PWM\_DELAY\_X to delay the start of the duty cycle from the beginning of the PWM cycle.

When using multiple PWM channels, it is recommended to add a delay between the PWM channels to moderate the overall peak current consumption of all active PWM channels.

Figure 15- PWM Diagram

### REG\_20 - PWM Frequency (Address 0x20)

Set the PWM frequency divider for all 8 optional PWM IOs.

| Bit 7   | Bit 6                 | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   |  |

|---------|-----------------------|---------|---------|---------|---------|---------|---------|--|

| R/W [0] | R/W [0]               | R/W [0] | R/W [0] | R/W [0] | R/W [0] | R/W [0] | R/W [0] |  |

|         | PWM frequency divider |         |         |         |         |         |         |  |

Bit [7:0] - PWM frequency divider.

The PWM frequency value is calculated as given in Definition of Equation (2)

### **Equation 2**

#### PWM frequency [KHz] = 31.37kHz / (PWM frequency divider[7:0] + 1) (2)

The Max PWM Frequency is 31.37 kHz ((PWM frequency divider == 0x00)

The Min PWM Frequency is 122.5Hz ((PWM frequency divider == 0xFF)

#### 4.3.2 REG\_10 to REG\_17 - PWM Delay\_X (Address 0x10 to address 0x17)

Set the PWM delay for all 8 optional PWM IOs.

| 000000000000000000000000000000000000000 | iii acia, ici ai | то ортопан г |         |         |         |         |         |  |  |  |

|-----------------------------------------|------------------|--------------|---------|---------|---------|---------|---------|--|--|--|

| Bit 7                                   | Bit 6            | Bit 5        | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   |  |  |  |

| R/W [0]                                 | R/W [0]          | R/W [0]      | R/W [0] | R/W [0] | R/W [0] | R/W [0] | R/W [0] |  |  |  |

|                                         | PWM Delay X      |              |         |         |         |         |         |  |  |  |

Bit [7:0] - PWM delay X.

By default, all the PWM channels are synchronized. The delay period enables the user to differentiate each pin output period.

17 Tel: +972-3-5445294 Fax: +972-3-5445279 www.yamar.com

The PWM delay value is calculated as given in Definition of Equation (3)

### **Equation 3**

## 4.3.1 REG\_18 to REG\_1F - PWM DUTY\_CYCLE\_X (Address 0x18 to address 0x1F)

Set the PWM duty cycle for all 8 optional PWM IOs.

| Bit 7            | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   |  |

|------------------|---------|---------|---------|---------|---------|---------|---------|--|

| R/W [0]          | R/W [0] | R/W [0] | R/W [0] | R/W [0] | R/W [0] | R/W [0] | R/W [0] |  |

| PWM Duty Cycle X |         |         |         |         |         |         |         |  |

Bit [7:0] - PWM Duty CYCLE X.

The PWM Duty cycle value is calculated as given in Definition of Equation (4)

#### **Equation 4**

## The following steps are required to configure a PWM channel:

- ✓ Set the PWM frequency in the PWM Frequency register.

- ✓ Set the PWM duty cycle in the PWM DUTY X register.

- ✓ Set the PWM delay in the PWM DELAY X register.

- ✓ Set the desire I/Os as PWM output (see REG\_21 and REG\_22).

### 4.4 Analog to Digital Converter (ADC)

The ADC module allows converting up to eight analog inputs into 12 bits of binary data. Each one of the SIG102 I/Os can be configured as analog input. All the analog inputs are internally mux into one ADC module.

The maximal sampling rate is 50 kSps.

The allowed ADC input signal is between 0 to 3.3V, this gives a maximum resolution of ~0.805mV per bit.

To guarantee a conversion error of less than that 0.5LSB, the source impedance at the input pin (R<sub>source</sub>) may not exceed 45 kOhm.

## 4.4.1 REG\_25 to REG\_34 – ADC\_X\_H and ADC\_X\_L (Address 0x25 to 0x34)

Each channel 12 bits conversion result is stored in 2 registers, ADC\_X\_L and ADC\_X\_H, whereas the X represents the channel (IO) number between 0 to 7.

### ADC\_H\_X

| Bit 7   | Bit 6                          | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   |  |  |  |

|---------|--------------------------------|---------|---------|---------|---------|---------|---------|--|--|--|

| R/W [0] | R/W [0]                        | R/W [0] | R/W [0] | R/W [0] | R/W [0] | R/W [0] | R/W [0] |  |  |  |

|         | ADC_H_X – ADC Conversion[11:4] |         |         |         |         |         |         |  |  |  |

Bit [7:0] - ADC MSB conversion results bit[11:4].

### ADC\_L\_X

| Bit 7   | Bit 6        | Bit 5        | Bit 4   | Bit 3 | Bit 2  | Bit 1 | Bit 0 |

|---------|--------------|--------------|---------|-------|--------|-------|-------|

| R/W [0] | R/W [0]      | R/W [0]      | R/W [0] | R     | R      | R     | R     |

| Д       | DC_L_X – ADC | Conversion[3 | 3:0]    |       | Reserv | ed    |       |

Bit [3:0] - Reserved.

Bit [7:4] - ADC LSB conversion results bit[3:0].

## **EXAMPLE 4**

The conversion result is 0x20 followed by 0x43;

$ADC_X_L = 0x20;$

$ADC_X_H = 0x43;$

Calculation of the conversion result will be:

$(ADC_X_H * 16) + (ADC_X_L / 16) = 0x43*16 + 0x20 / 16 = 1072 + 2 = 1074 = (1074 / 4096) * 3.3V = 0.865V.$

### 4.4.2 ADC Write and Read operation

An ADC conversion starts by performing the WRITE-REG command (locally or remotely, see 5.2) to the ADC\_L\_X ADC\_H\_X registers. When the conversion is completed, the results are stored in the corresponding ADC register. Users can retrieve the last ADC conversion by sending a READ-REG command to a specific ADC channel address. When reading from the ADC\_X\_H address, the SIG102 replies with a single byte of higher nibble conversion result (ADC conversion[11:4]).

When reading from ADC\_X\_L, the SIG102 replies with the full word conversion result (2 bytes, ADC\_L\_X followed by ADC\_H\_X).

### 4.4.2.1 REG\_35 - WRITE/READ ADC ALL (Address 0x35)

To simplify ADC write and read operation, the WRITE/READ ADC ALL register allows users to activate a sequentially analog conversion from all active ADC channels and reply with all conversion results within one message. By performing the WRITE-REG command to REG\_35, a sequentially analog conversion from each one of the active ADC pin is being made. By performing the READ-REG command, the SIG102 returns with 2 bytes conversion results per active analog IOs, starting from low IO index to high IO index (Maximal 2 X 8 = 16 bytes).

|                                                                 | Bit 7              | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |

|-----------------------------------------------------------------|--------------------|-------|-------|-------|-------|-------|-------|-------|--|

| R/W [0] |                    |       |       |       |       |       |       |       |  |

| ĺ                                                               | WRITE-READ-ADC-ALL |       |       |       |       |       |       |       |  |

#### **EXAMPLE 5**

SIG102 IOs 0, 3, and 7 are configured as analog inputs. To enable a sequentially ADC conversion of ADC channel 0, 3, and 7, a **WRITE-REG to 'ADC Read/Write All'** register is performed (The write data byte is ignored).

Upon receiving the WRITE-REG command, the SIG102 will start an ADC conversion starting from channel ADC 0 and ending at channel ADC 7.

Then, perform a READ-REG command from the 'ADC Read/Write All' register.

The SIG102 response with ADC0, ADC3 and ADC7 conversion results: 0x60, 0x35, 0x10, 0x00, 0xF0, and 0x1F (for instance) as follows:

| 1 <sup>st</sup> byte 2 <sup>nd</sup> byte |             | 3 <sup>rd</sup> byte | 4 <sup>th</sup> byte | 5 <sup>th</sup> byte | 6 <sup>th</sup> byte |

|-------------------------------------------|-------------|----------------------|----------------------|----------------------|----------------------|

| 0x60                                      | 0x60 0x35   |                      | 0x00                 | 0xF0                 | 0x1F                 |

| 10 0 10 0                                 |             | IO 3                 | IO 3                 | IO 7                 | IO 7                 |

| ADC_L                                     | ADC_H       | ADC_L                | ADC_H                | ADC_L                | ADC_H                |

| ADC0 - 0x                                 | 356 = 0.68V | ADC3 - 0x00          | 1 = 0.805mV          | ADC7 - 0x1           | FF = 0.411V          |

## 5 SIG102 I/Os settings and control

Setting and controlling each IO is made by WRITE-REG and READ-REG operations from/to the IO control registers, either locally using the command mode (HDC pin required), or remotely over the powerline from a SIG102 Master device using dedicated PLC commands (see 5.2).

Table 10 described the IO control registers summary.

**Table 10 - IO Control register summary**

| Register | R/W | Register name | Function                            |

|----------|-----|---------------|-------------------------------------|

| Address  |     |               |                                     |

| 0x10     | r/w | PWM_delay_0   | PWM IO 0 delay period configuration |

| 0x11     | r/w | PWM_delay_1   | PWM IO 1 delay period configuration |

| 0x12     | r/w | PWM_delay_2   | PWM IO 2 delay period configuration |

| 0x13     | r/w | PWM_delay_3   | PWM IO 3 delay period configuration |

| 0x14     | r/w | PWM_delay_4   | PWM IO 4 delay period configuration |

| 0x15     | r/w | PWM_delay_5   | PWM IO 5 delay period configuration |

| 0x16     | r/w | PWM_delay_6   | PWM IO 6 delay period configuration |

| 0x17     | r/w | PWM_delay_7   | PWM IO 7 delay period configuration |

| 0x18     | r/w | PWM_duty_0    | PWM IO 0 duty cycle configuration   |

| 0x19     | r/w | PWM_duty_1    | PWM IO 1 duty cycle configuration   |

| 0x1A     | r/w | PWM_duty_2    | PWM IO 2 duty cycle configuration   |

| 0x1B     | r/w | PWM_duty_3    | PWM IO 3 duty cycle configuration   |

© 2020-2023 Yamar Electronics Ltd.

DS-SIG102 R 0.90

<sup>\*\*</sup> Note - Reading for inactive ADC channel address will result in no response message from the SIG102 device.

| 0x1C | r/w        | PWM_duty_4       | PWM IO 4 duty cycle configuration                                      |

|------|------------|------------------|------------------------------------------------------------------------|

| 0x1D | r/w        | PWM_duty_5       | PWM IO 5 duty cycle configuration                                      |

| 0x1E | r/w        | PWM_duty_6       | PWM IO 6 duty cycle configuration                                      |

| 0x1F | r/w        | PWM_duty_7       | PWM IO 7 duty cycle configuration                                      |

| 0x20 | r/w        | PWM frequency    | PWM frequency configuration                                            |

| 0x21 | r/w        | I/O Configure 1  | Configure I/O[7:0] as Inputs ('1') Or Outputs ('0')                    |

| 0x22 | r/w        | I/O Configure 2  | Configure I/O[7:0] functionality as digital ('0') or PWM / ADC ('1')   |

| 0x23 | r/w        | IO Watchdog      | WatchDog module control                                                |

| 0x24 | r/w        | Digital I/Os     | Write to this register will update the digital outputs I/Os status     |

|      |            |                  | correspondingly.                                                       |

|      |            |                  | Read from this register will feedback the status of the digital inputs |

|      |            |                  | I/Os and output I/Os (latch).                                          |

| 0x25 | r/w        | ADC0_H           | Read command returns the last measured ADCO higher nibble value        |

|      |            |                  | (1 byte). Write command enables new ADC conversion on IO 0             |

| 0x26 | r/w        | ADC0_L           | Read command returns the measured ADCO word value (2 bytes).           |

|      |            |                  | Write command enables new ADC conversion on IO 1                       |

| 0x27 | r/w        | ADC1_H           | Read command returns the measured ADC1 higher nibble value (1          |

|      |            |                  | byte). Write command start new ADC conversion on IO 1                  |

| 0x28 | r/w        | ADC1_L           | Read command returns the measured ADC1 word value (2 bytes).           |

|      |            |                  | Write command enables new ADC conversion on IO 1                       |

| 0x29 | r/w        | ADC2_H           | Read command returns the measured ADC2 higher nibble value (1          |

|      |            |                  | byte). Write command start new ADC conversion on IO 2                  |

| 0x2A | r/w        | ADC2_L           | Read command returns the measured ADC2 word value (2 bytes).           |

|      |            |                  | Write command enables new ADC conversion on IO 2                       |

| 0x2B | r/w        | ADC3_H           | Read command returns the measured ADC3 higher nibble value (1          |

|      |            |                  | byte). Write command start new ADC conversion on IO 3                  |

| 0x2C | r/w        | ADC3_L           | Read command returns the measured ADC3 word value (2 bytes).           |

|      |            |                  | Write command enables new ADC conversion on IO 3                       |

| 0x2D | r/w        | ADC4_H           | Read command returns the measured ADC4 higher nibble value (1          |

|      |            |                  | byte). Write command start new ADC conversion on IO 4                  |

| 0x2E | r/w        | ADC4_L           | Read command returns the measured ADC4 word value (2 bytes).           |

|      |            |                  | Write command enables new ADC conversion on IO 4                       |

| 0x2F | r/w        | ADC5_H           | Read command returns the measured ADC5 higher nibble value (1          |

|      |            |                  | byte). Write command start new ADC conversion on IO 5                  |

| 0x30 | r/w        | ADC5_L           | Read command returns the measured ADC5 word value (2 bytes).           |

|      |            |                  | Write command enables new ADC conversion on IO 5                       |

| 0x31 | r/w        | ADC6_H           | Read command returns the measured ADC6 higher nibble value (1          |

|      |            |                  | byte). Write command start new ADC conversion on IO 6                  |

| 0x32 | r/w        | ADC6_L           | Read command returns the measured ADC6 word value (2 bytes).           |

|      | ,          | 1007.11          | Write command enables new ADC conversion on IO 6                       |

| 0x33 | r/w        | ADC7_H           | Read command returns the measured ADC7 higher nibble value (1          |

| 024  | 1          | 4007 /           | byte). Write command start new ADC conversion on IO 7                  |

| 0x34 | r/w        | ADC7_L           | Read command returns the measured ADC7 word value (2 bytes).           |

| 025  | ,. I       | ADC Be and Males | Write command enables new ADC conversion on IO 7                       |

| 0x35 | r/w        | ADC Read/Write   | Read command returns the measurements of all active ADC los            |

|      |            | All              | sequentially. Write command enables new ADC conversion for all         |

| 0426 | <i>p.l</i> | Clava Davisa ID  | active ADC IOs (See 4.4.2.1).                                          |

| 0x36 | r/w        | Slave Device ID  | SIG102 Slave Address – Set the SIG102 Slave ID from 0x00 to 0xFE.      |

|      |            |                  | OxFF ID is preserved as broadcast global ID (see 5.2.1.2).             |

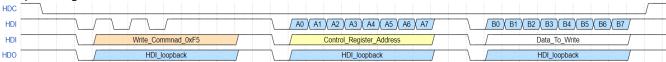

## 5.1 I/Os local control

Accessing to each one of the IO control registers is done locally by ECU interfacing the HDI, HDO, and HDC pins, and performing WRITE-REG and READ-REG commands (see 7.14).

#### 5.2 I/Os Remote slaves control (Commands over powerline)

A SIG102 IOs can be controlled remotely over the powerline by a set of commands transmitted from a SIG102 master (attached to a host ECU).

Table 11 describes the PLC SIG102 commands summary.

Table 11 - PLC SIG102 commands summary

| Command name              | Command Identifier | Description                                  |

|---------------------------|--------------------|----------------------------------------------|

| PLC WRITE-REG             | 0xFB               | Write to the SIG102 internal registers.      |

| PLC READ-REG              | 0xBA               | Read from the SIG102 internal registers.     |

| PLC SLEEP                 | 0x3C               | Put the remote slaves in Sleep mode.         |

| PLC CHANGE FREQUENCY MAIN | 0xB4               | Change the remote slave frequency channel to |

|                           |                    | the Main frequency.                          |

| PLC CHANGE FREQUENCY ALT1 | 0xB1               | Change the remote slave frequency channel to |

|                           |                    | ALT1 frequency.                              |

| PLC CHANGE FREQUENCY ALT2 | 0x32               | Change the remote slave frequency channel to |

|                           |                    | ALT2 frequency.                              |

#### 5.2.1 **PLC command structure**

The PLC command is as follows:

| Break Field Sync Field Identifier | SIG102 Slave ID | DATA bytes | Checksum |

|-----------------------------------|-----------------|------------|----------|

|-----------------------------------|-----------------|------------|----------|

- Break Field Break field length is at least 13-bit times.

- Sync Field '0x55' byte.

- Identifier byte The specific command byte.

- SIG102 Slave ID SIG102 ID byte. 0xFF is the global ID.

- **Data bytes -** Includes the bytes according to selectable command.

#### 5.2.1.1 **Checksum calculations**

The checksum is an inverted 8-bit sum of the Identifier and Data byte including (own) carry as given in Definition of Equation (5)

#### **Equation 5**

#### 5.2.1.2 SIG102 ID

The SIG102 ID range is from 0x00 to 0xFE.

ID 0xFF is preserved as the global ID. Using the global ID allows the user to send broadcast SIG102 commands over the powerline. All commands will be executed by all active SIG102 salves. A read command with a global ID will not be responded.

The SIG102 ID is set either by setting HW pins ID0 to ID7 or by the configuration of REG\_36. The last action prevails.

Upon power-up/hard-reset event, SIG102 ID is set according to HW pins state and remains until the next change on pin ID0 to ID7 or REG\_36 configuration.

### **REG\_36 - SIG102 ID (Address 0x36)**

| Bit 7                                                           | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |

|-----------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|--|

| R/W [0] |       |       |       |       |       |       |       |  |

| SIG102 ID                                                       |       |       |       |       |       |       |       |  |

Bit [7:0] - SIG102 ID.

#### 5.2.2 **PLC Commands description**

#### 5.2.2.1 **PLC READ-REG command**

This command reads the data from the internal registers of the remoted SIG102 slave.

21 DS-SIG102 R 0.90 Tel: +972-3-5445294 Fax: +972-3-5445279 www.yamar.com

The format of the command to the SIG102 slave:

| Break field | Sync Byte  | Identifier Bute | SIG102 Slave ID | Reg. Address |

|-------------|------------|-----------------|-----------------|--------------|

| Dreak Helu  | Sylic byte | identiner byte  | SIGIUZ SIAVE ID | Reg. Address |

- Break field Hold the Data in line at low for a duration of 13 to 31 bits

- Sync Byte send a 0x55 byte.

- **Identifier Byte 0xBA** for the read command.

- SIG102 Slave ID The ID of the remote SIG102 slave we would like to read from. In the case of Global ID,

0xFF is transmitted, the SIG102 will not send a reply message.

- Reg Add The internal SIG102 register address to read from.

Upon receiving the Read register command from the master, the SIG102 response with the internal register value followed by a checksum byte.

The format of Read-Register command Response to the Master -

Data Checksum

Data - Internal register value.

- o Reading from 'ADC H X' responds with the conversion results MSB[11:3].

- o Reading from 'ADC \_L\_X' responds with 'ADC\_L\_X followed by 'ADC \_H\_X' (conversion result[11:0]) .

- Reading from the 'ADC Read/Write All' register will output 2 data bytes (Low and high nibbles

- bytes) represent last ADC sampling for each active ADC channel, a maximum of 16 bytes for all ADC channels (see 4.4)

- o Reading from all other internal registers will output 1 data byte.

**Checksum -** The message checksum byte.

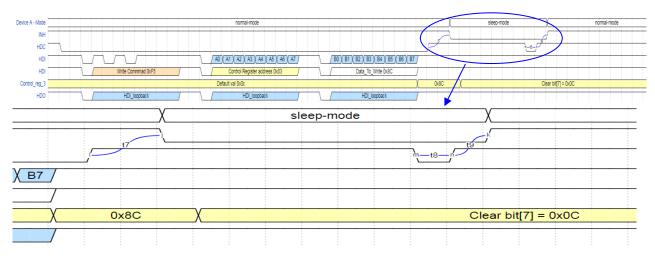

#### 5.2.2.2 PLC WRITE-REG command

This command writes data to internal registers of remoted SIG102 salve.

The format of the command:

| Break field   | Sync Byte | Identifier Byte      | SIG102 Slave ID | Reg. Addr | Data | Checksum   |

|---------------|-----------|----------------------|-----------------|-----------|------|------------|

| Di cait iicia | 0,00,0    | identification by to | 0.010101010     |           |      | O. CONSULL |

- Break field Hold the Data in line at low for a duration of 13 to 31 bits

- Sync Byte send a 0x55 byte.

- Identifier Byte 0xFB for the write command

- Slave ID The ID of the remote SIG102 slave we would like to write to.

- Reg Add The internal SIG102 register address to write.

- Data The data to be written to SIG102 slave internal register

- Checksum The message checksum byte.

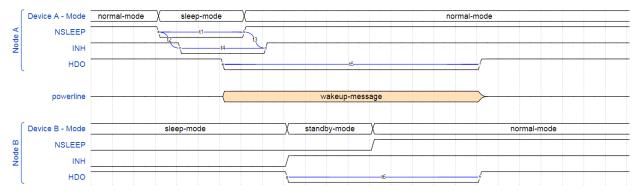

### 5.2.2.3 PLC SLEEP command

Upon receiving this command, the SIG102 will compare the received ID to its ID or the broadcast ID. If there is a match the SIG102 will enter Sleep mode.

The format of the command:

| Break field   Sync Byte   Identifier Byte   SIG102 Slave ID   Checks | Break field | SIG102 Slave ID Checksum | Sync Byte |

|----------------------------------------------------------------------|-------------|--------------------------|-----------|

|----------------------------------------------------------------------|-------------|--------------------------|-----------|

- Break field Hold the Data in line at low for a duration of 13 to 31 bits

- Sync Byte send a 0x55 byte.

- Identifier Byte 0x3C for the Sleep command (as in LIN2.0 specifications)

- Slave ID The ID of the remote SIG102 slave we would like to put into Sleep mode.

- Checksum The message checksum byte.

### 5.2.2.4 PLC CHANGE FREQUENCY commands

Upon receiving this command, the SIG102 will compare the received ID to its ID or the broadcast ID. If there is a match the SIG102 will change the frequency channel selection according to the identifier byte.

The format of the command:

<u>www.yamar.com</u>

Tel: +972-3-5445294 Fax: +972-3-5445279

<sup>\*</sup> Sending write command to an ADC channel activates the A/D conversion. The Data byte field is ignored (see 4.4).

| Dunni, finial | Como Dorto | Idantifian Duta | CICADA Claves ID | Chaalaaaaa |

|---------------|------------|-----------------|------------------|------------|

| Break field   | Sync Byte  | Identifier Byte | SIG102 Slave ID  | Checksum   |

- Break field Hold the Data in line at low for a duration of 13 to 31 bits

- Sync Byte send a 0x55 byte.

- **Identifier Byte -**

- 0xB4 Change frequency to Main frequency

- 0xB1 Change frequency to Alternate Frequency 1,

- 0x32 Change frequency to Alternate frequency 2.

- Slave ID The ID of the remote SIG102 slave we would like to change its frequency selection.

- **Checksum** The message checksum byte.

#### 5.2.3 **SIG102 PLC Commands examples**

#### Example 1

Analog conversion of ADC channel 0 from SIG102 Slave #5 start with a PLC WRITE-REG command to register ADC0\_H:

| _ | Break Field | Sync Byte | Identifier Byte | SIG102 Slave ID | Reg. Address            | Data   | Checksum |

|---|-------------|-----------|-----------------|-----------------|-------------------------|--------|----------|

|   | 0x00,0x00   | 0x55      | 0xFB            | 0x05            | 0x25 ('ADCO_H' Address) | * 0xXX | 0xd9     |

<sup>\*</sup> When writing to an ADC channel the data byte is ignored.

Then, reading from ADC\_O\_H, by sending PLC READ-REG command:

| Break Field | Sync Byte | Identifier Byte | SIG102 Slave ID | Reg Address             |

|-------------|-----------|-----------------|-----------------|-------------------------|

| 0x00 ,0x00  | 0x55      | ОхВА            | 0x05            | 0x25 ('ADC0_H' Address) |

The SIG102 response with the higher nibble conversion result 0x0134 (for instance) and a checksum byte. The conversion results are stored in the 'ADCO\_H' and 'ADCO\_L' registers.

The 'ADCO\_H' stores the 8 MSB and the 'ADCO\_L' store the 4 LSB shifted 4 times to the right.  $'ADCO_H' = 0x13, 'ADCO_L' = 0x40.$

| Data | Checksum |

|------|----------|

| 0x13 | 0x08     |

|      |          |

Where Checksum =  $^{\sim}(0xBA + 0x05 + 0x25 + 0x13) = ^{\sim}(0xF7) = 0x08$ .

Reading from ADC\_0\_L, by sending PLC READ-REG command -

| Sync Break | Sync Byte | Identifier Byte | SIG102 Slave ID | Reg. Address            |

|------------|-----------|-----------------|-----------------|-------------------------|

| 0x00 ,0x00 | 0x55      | 0xBA            | 0x05            | 0x26 ('ADC0_L' Address) |

The SIG102 response with the full word conversion result **0x0134** and a checksum byte.

| Data      | Checksum |

|-----------|----------|

| 0x40,0x13 | 0xC6     |

|           |          |

Where Checksum =  $^{(0xBA + 0x05 + 0x26 + 0x40 + 0x13)}$  =  $^{(0x138)}$  => add the carry =>  $^{(0x39)}$ = 0xC6.

### Example 2

SIG102 IOs 0, 3, and 7 are configured as analog inputs. to enable a sequentially ADC conversion of ADC 0, 3, and 7 from all active SIG102 slaves (global ID) starts with a PLC WRITE-REG to register 'ADC Read/Write All' -

| Break Field | Sync Byte | Identifier Byte | SIG102 Slave ID  | Reg. Address                 | Data   | Checksum |

|-------------|-----------|-----------------|------------------|------------------------------|--------|----------|

| 0x00, 0x00  | 0x55      | 0xFB            | 0xFF (global ID) | 0x35 ('ADC R/W All' Address) | * 0xXX | Охсе     |

|             |           |                 |                  |                              |        |          |

When writing to the 'ADC Read/Write All' register the data byte is ignored.

Upon receiving the write command, the SIG102 will start an ADC conversion starting from channel ADC0 and ending at channel ADC7.

23 DS-SIG102 R 0.90 Tel: +972-3-5445294 Fax: +972-3-5445279 www.yamar.com

Then, to read from SIG102 slave #3, send PLC READ-REG to 'ADC Read/Write All' -

| Break Field | Sync Byte | Identifier Byte | SIG102 Slave ID | Reg. Address                 |