### **Features**

- AEC-Q100 Grade-1 Qualified (TPM2025Q Only)

- Dual Independent Channels

- 5-V Single Supply with Optimized Output Damping for Gan Reliability

- 7-A Peak Source And 5-A Sink-Drive Current

- 0.69-ns Minimum Input Pulse Width (Typical)

- Low Propagation Delay (2-ns Typical)

- Optimized Pinout for nanosecond-pulse-width

- Fast Rise and Fall Times (0.45-ns and 0.45-ns Typical)

- <0.61-ns Typical Delay Matching Between Two Channels

- ESD Protection Exceeds JESD 22 6-kV HBM, 1.5-kV CDM

- Available in Flip-Chip QFN2X2-10 Package

# **Applications**

- Laser Distance Measuring System

- Automotive Lidar

- Driver Monitoring System

- GaN DC/DC Conversion System

### **Description**

The TPM2025 / TPM2025Q family are low-side dual-channel ultra-highspeed gate drivers for GaN and logic-level MOSFETs. It is optimized for high-speed applications such as Lidar and high-density power convertors with enhanced low propagation delay design. The TPM2025's 2-mm×2-mm flip-chip QFN package minimizes parasitic inductance in the gate driver power loop and achieves state-of-the-art narrow pulse width as short as 0.69 ns. Channel independent transient suppressors ensure reliable operation with ultra-fast high-current output pulses.

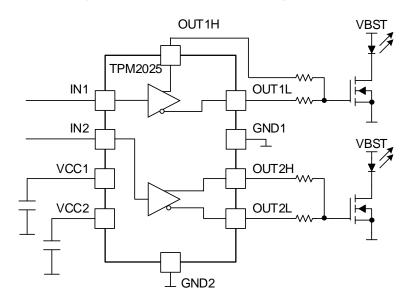

## **Typical Application Diagram**

Figure 1 Typical Application Diagram

## **Table of Contents**

| Features                                |    |

|-----------------------------------------|----|

| Applications                            |    |

| Description                             |    |

| Typical Application Diagram             |    |

| Revision History                        | 3  |

| Pin Configuration and Functions         | 4  |

| Pin Functions                           | 4  |

| Specifications                          | 5  |

| Absolute Maximum Ratings                | 5  |

| ESD, Electrostatic Discharge Protection | 5  |

| Recommended Operation Conditions        | 5  |

| Thermal Information                     | 6  |

| Electrical Characteristics              | 7  |

| Typical Performance Characteristics     | ε  |

| Detailed Description                    | 10 |

| Overview                                |    |

| Functional Block Diagram                | 10 |

| Feature Description                     | 10 |

| Application and Implementation          | 12 |

| Application Information                 | 12 |

| Typical Application                     | 12 |

| Tape and Reel Information               |    |

| Package Outline Dimensions              | 14 |

| Order Information                       | 14 |

| IMPORTANT NOTICE AND DISCLAIMER         | 15 |

# **Revision History**

| Date       | Revision | Notes                                                                                           |

|------------|----------|-------------------------------------------------------------------------------------------------|

| 2021/07/15 | Rev. A.0 | Initial release                                                                                 |

| 2023/02/28 | Rev. A.1 | Updated TPM2025Q orderable part number. Updated electrical characteristics on timing footnotes. |

| 2023/07/10 | Rev. A.2 | Added transient voltage rating                                                                  |

| 2023/08/07 | Rev. A.3 | Added ground description and truth table. Block diagram amendment on signal polarity.           |

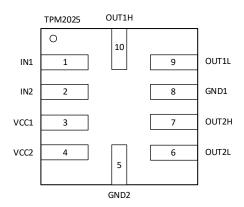

# **Pin Configuration and Functions**

QFN2X2-10 Top View

#### **Pin Functions**

| Р   | 'in   | 1/0    | December 1                   |  |  |

|-----|-------|--------|------------------------------|--|--|

| No. | Name  | I/O    | Description                  |  |  |

| 1   | IN1   | Input  | Channel 1 Input, Active High |  |  |

| 2   | IN2   | Input  | Channel 2 Input, Active High |  |  |

| 3   | VCC1  | Supply | Device Supply for Channel 1  |  |  |

| 4   | VCC2  | Supply | Device Supply for Channel 2  |  |  |

| 5   | GND2  | Ground | Device Ground for Channel 2  |  |  |

| 6   | OUT2L | Output | Channel 2 Pull-down Output   |  |  |

| 7   | OUT2H | Output | Channel 2 Pull-up Output     |  |  |

| 8   | GND1  | Ground | Device Ground for Channel 1  |  |  |

| 9   | OUT1L | Output | Channel 1 Pull-down Output   |  |  |

| 10  | OUT1H | Output | Channel 2 Pull-up Output     |  |  |

## **Specifications**

### **Absolute Maximum Ratings**

| Parameters                                                   | Rating             |  |  |

|--------------------------------------------------------------|--------------------|--|--|

| Power Supply Voltage, VCC1, VCC2                             | -0.3 V to 6 V      |  |  |

| Power Supply Voltage Difference, VCC1 – VCC2                 | -6 V to 6 V        |  |  |

| Ground Difference, GND1 – GND2                               | -0.3V to 0.3V      |  |  |

| Output Voltage Range OUT1H, OUT1L                            | -0.3V to VCC1+0.3V |  |  |

| Output Voltage Range OUT1H, OUT1L, 5-ns Transient            | –5V to VCC1+5V     |  |  |

| Output Voltage Range OUT1H, OUT1L, 10-ns Transient           | -2V to VCC1+2V     |  |  |

| Output Voltage Range OUT2H, OUT2L                            | -0.3V to VCC2+0.3V |  |  |

| Output Voltage Range OUT2H, OUT2L, 5-ns Transient            | –5V to VCC2+5V     |  |  |

| Output Voltage Range OUT2H, OUT2L, 10-ns Transient           | -2V to VCC2+2V     |  |  |

| Input Voltage Range IN1, IN2                                 | -0.3 V to 6 V      |  |  |

| Continuous Output Channel Current OUT1H, OUT2H, OUT1L, OUT2L | –500 mA to 500 mA  |  |  |

| Pulsed Output Channel Sourcing Current OUT1H, OUT1H (500 ns) | 7 A                |  |  |

| Pulsed Output Channel Sourcing Current OUT1H, OUT1H (500 ns) | 5 A                |  |  |

| Operating Junction Temperature Range                         | −40 °C to 150 °C   |  |  |

| Storage Temperature Range                                    | −65 °C to 150 °C   |  |  |

| Lead Temperature (Soldering, 10 sec)                         | 260 °C             |  |  |

**Note 1**: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

### **ESD, Electrostatic Discharge Protection**

| Symbol | Parameter                | Parameter Condition                         |      | Unit |

|--------|--------------------------|---------------------------------------------|------|------|

| НВМ    | Human Body Model ESD     | ANSI/ESDA/JEDEC JS-001, per AEC<br>Q100-002 | ±6   | kV   |

| CDM    | Charged Device Model ESD | ANSI/ESDA/JEDEC JS-002, per AEC<br>Q100-011 | ±1.5 | kV   |

### **Recommended Operation Conditions**

| Parameters | Rating |

|------------|--------|

|------------|--------|

**Note 2**: The inputs are protected by ESD protection diodes to each power supply. If the input extends more than 300 mV beyond the power supply, the input current should be limited to less than 10mA.

Note 3: Power dissipation and thermal limits must be observed.

| Power Supply Voltage, VCC1, VCC2                         | 4.75 V to 5.25 V |

|----------------------------------------------------------|------------------|

| Power Supply Voltage Difference VCC1 – VCC2, GND1 – GND2 | 0 V              |

| Input Voltage IN1, IN2                                   | 0 V to VCC       |

| Output Voltage VOUT1H, VOUT1L, VOUT2H, VOUT2L            | 0 V to VCC       |

| Operating Ambient Temperature Range                      | –40 °C to 125 °C |

## **Thermal Information**

| Package Type | θ <sub>JA</sub> | $	heta_{	extsf{JC}}$ | Unit |  |

|--------------|-----------------|----------------------|------|--|

| QFN2X2-10    | 87.54           | 119.32               | °C/W |  |

### **Electrical Characteristics**

All test condition is  $V_{CC}$  = 5 V,  $T_J$  = -40 °C - 150 °C, 1- $\mu$ F capacitor between  $V_{CC}$  and GND, unless otherwise noted

| Symbol                             | Parameter                                                              | Conditions                                                                       | Min  | Тур  | Max  | Unit     |

|------------------------------------|------------------------------------------------------------------------|----------------------------------------------------------------------------------|------|------|------|----------|

|                                    | VCC Ovince and Comment                                                 | IN1 = H, IN2 = H                                                                 |      | 105  | 200  |          |

| lα                                 | VCC Quiescent Current                                                  | IN1 = L, IN2 = L                                                                 |      | 105  | 200  | μA       |

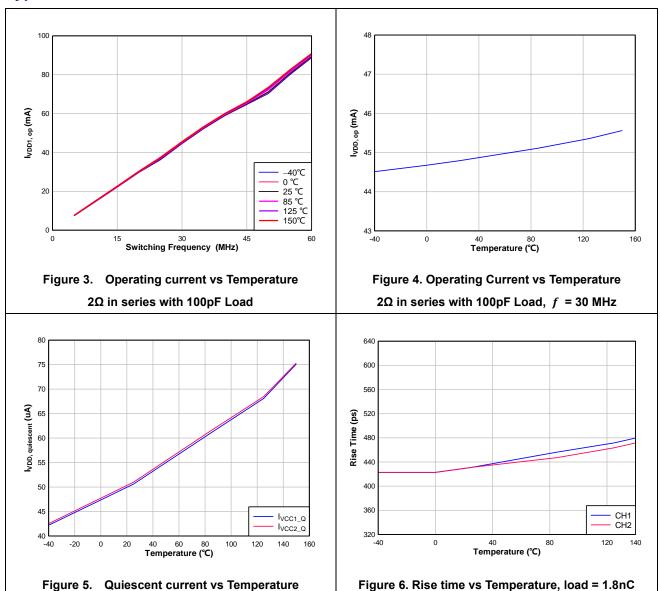

|                                    |                                                                        | $f_{SW}$ =30 MHz, no load, Routh = 2 $\Omega$ , Routl = 2 $\Omega$               |      | 40   |      | mA       |

| Іор                                | VCC Operating Current                                                  | $f_{SW}$ =30 MHz, 100-pF load, $R_{OUTH}$ = 2 $\Omega$ , $R_{OUTL}$ = 2 $\Omega$ |      | 51   |      | mA       |

| $V_{\sf UVLO\_rising}$             | Supply Under Voltage Lock Out rising threshold                         |                                                                                  | 4    | 4.18 | 4.35 | V        |

| $V_{UVLO\_hys}$                    | Supply Under Voltage Lock Out falling hysteresis                       |                                                                                  |      | 85   |      | mV       |

| Тотр                               | Over temperature shutdown, turn-off                                    |                                                                                  |      | 170  |      | °C       |

| $\Delta T_{\text{OTP}}$            | Over temperature hysteresis                                            |                                                                                  |      | 20   |      | °C       |

| $V_{IN\_H}$                        | Input signal high threshold                                            | Input high threshold                                                             | 1.7  | 2.15 | 2.6  | <b>V</b> |

| $V_{IN\_L}$                        | Input signal low threshold                                             | Input low threshold                                                              | 1.1  | 1.45 | 1.8  | V        |

| V <sub>IN_HYS</sub>                | Input hysteresis                                                       |                                                                                  | 0.38 |      | 1    | V        |

| R <sub>IN_pulldown</sub>           | Input pull-down resistance                                             |                                                                                  | 100  | 150  | 250  | kΩ       |

| C <sub>IN</sub>                    | Input capacitance                                                      |                                                                                  |      |      | 1.5  | pF       |

| V <sub>OL</sub>                    | Output low voltage. OUTxL                                              | I <sub>OUTxL</sub> = 100 mA, INx = 0 V                                           |      |      | 36   | mV       |

| V <sub>CCx</sub> –V <sub>OHx</sub> | Output high voltage, OUTxH                                             | I <sub>OUTxH</sub> = 100 mA, INx = 5 V                                           |      |      | 50   | mV       |

| Іон                                | Output Peak Sourcing Current                                           | V <sub>OUTxH</sub> = 0 V, INx = 5 V                                              |      | 7    |      | Α        |

| loL                                | Output Peak Sinking Current                                            | V <sub>OUTxL</sub> = 5 V, INx = 0 V                                              |      | 5    |      | Α        |

| $T_{start}$                        | Startup Time, VDD rising above UVLO                                    | INx = 5 V ,VDD rising above<br>UVLO to OUTH rising                               |      | 40   | 78   | us       |

| $T_{\text{shut-off}}$              | ULVO falling                                                           | INx = 5 V ,VDD falling below<br>UVLO V to OUTH falling                           | 0.7  | 2.5  | 3.5  | us       |

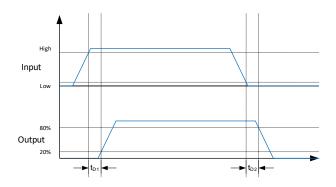

| T <sub>pd, r</sub> (1)             | Propagation delay, turn on                                             | INx to OUTH, 100-pF load                                                         |      | 2    | 4    | ns       |

| T <sub>pd, f</sub> <sup>(1)</sup>  | Propagation delay, turn off                                            | INx to OUTL, 100-pF load                                                         |      | 2    | 4    | ns       |

| $\Delta t_{pd}$                    | Pulse positive distrortion, (t <sub>pd, f</sub> - t <sub>pd, r</sub> ) |                                                                                  |      | 300  | 610  | ps       |

| t <sub>R</sub>                     | Output rise-time                                                       | 0Ω series 220 pF load                                                            |      | 450  |      | ps       |

| t⊧                                 | Output fall-time                                                       | 0Ω series 220 pF load                                                            |      | 450  |      | ps       |

| t <sub>PW</sub>                    | Minimum input pulse width that changes output state                    | 0Ω series 220 pF load                                                            |      | 0.69 |      | ns       |

<sup>(1)</sup> Guranteed by design.

**Figure 2 Input Timing Diagram**

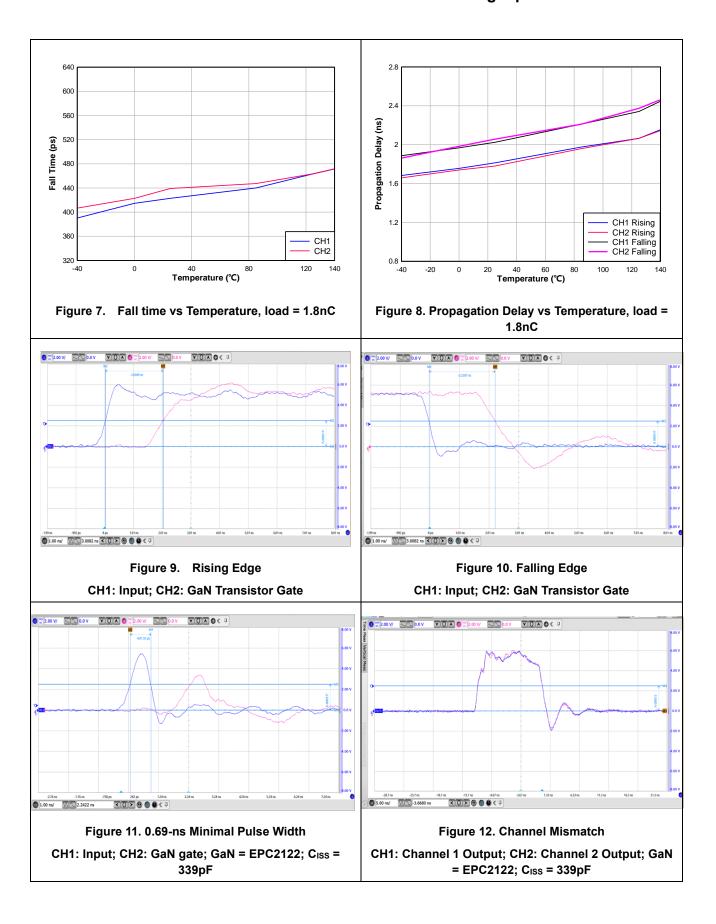

## **Typical Performance Characteristics**

### **Detailed Description**

#### **Overview**

The TPM2025 is a low-side dual-channel ultra-highspeed gate driver for GaN and logic-level MOSFETs. It is optimized for high-speed applications such as Lidar and high-density power convertors with enhanced low propagation delay design. The TPM2025's 2-mm×2-mm flip-chip QFN package minimizes parasitic inductance in the gate driver power loop and achieves state-of-the-art narrow pulse width as low as 0.69 ns. Channel independent transient suppressors ensure reliable operation with ultra-fast high-current output pulse.

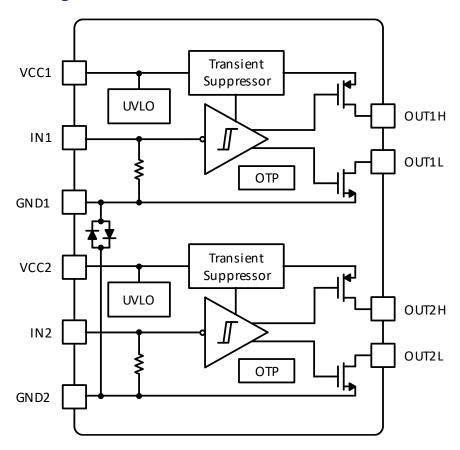

#### **Functional Block Diagram**

Figure 13 Functional Block Diagram

#### **Feature Description**

### Supply and Under-Voltage-Lock-Out (UVLO)

The device has dual supply inputs that are dedicated for each channel independently, to avoid interferences between channels during operations. The two ground paths for the dual channels are connected via back-to-back diodes.

Each channel has its own under-voltage-lock-out (UVLO) monitors. When supply voltage is above its rising threshold, the outputs are functional. When supply voltage is below its falling threshold, the device pulls OUTxL to GND. A short deglitch timer is inserted to avoid oscillations on power supply.

Due to ultra-fast turn-on speed, channel output may drain high current on supply nodes within nanoseconds.

3PEAK recommends placing 3-terminal capacitors close to device supply pins as low as possible. Parasitic inductance may prevent external capacitors from supplying current in such short time, the TPM2025 has built in transient suppressor circuitry to avoid sudden drop which may trigger UVLO and cause output malfunction.

TPM2025 provides dual device ground connection with back-to-back diodes to minimize channel-to-channel interference via internal ground connections. 3PEAK recommends connect GND1 and GND2 externally together with low impedance.

#### **Channel Input and Output**

The channel inputs are connected to a low-latency Schmitt trigger. It can cut propagation delay without additional gates. The inputs are pulled low via internal resistors.

The TPM2025 provides dual outputs with split pull-up and pull-down paths. The split outputs allow users to independently configure pull-up and pull-down slew-rate via external resistors. The maximum current the output can sink/source is +7 / -5 A. Configuring slew rates may reduce ringing on GaN gate node due to parasitic inductance/capacitance, thus it can improve reliability of GaN transistors.

| Inputs (INx)                  | OUTxH          | OUTxL          |  |  |

|-------------------------------|----------------|----------------|--|--|

| Н                             | Н              | High-Impedance |  |  |

| L                             | High-Impedance | L              |  |  |

| Floating (Internal Pull Down) | High-Impedance | L              |  |  |

**Table 1 Output Truth Table**

#### **Channel Output in Parallel**

To achieve higher pull-up current while still maintain short current path, the TPM2025 could support driving highside outputs together, as depicted in below diagram. OUT1L could be left floating in this case.

www.3peak.com 11 / 15 Rev.A.2

Figure 14 Parallel Output Pull-up

#### **Over Temperature Protection (OTP)**

The TPM2025 provides independent over temperature protection function to independently disable each channel. When junction temperature rises above rising threshold, the channel outputs are disabled; when junction temperature falls below falling threshold, the channel outputs are enabled.

### **Application and Implementation**

#### NOTE

Information in the following applications sections is not part of the 3PEAK's component specification and 3PEAK does not warrant its accuracy or completeness. 3PEAK's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### **Application Information**

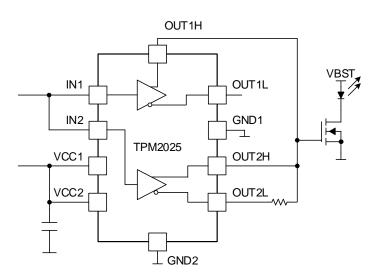

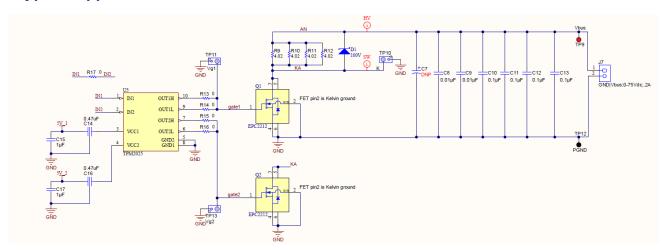

In modern Time-of-Flight (ToF) LiDAR system, it is necessary to ensure a narrow laser pulse. Gallium nitride (GaN) transistors are widely used in the industry due to its high switching frequency. As depicted in below schematic, it is required to keep gate driver output loop as small as possible to minimize parasitic inductance.

#### **Typical Application**

Figure 15 Typical Lidar Application Schematic

www.3peak.com 12 / 15 Rev.A.2

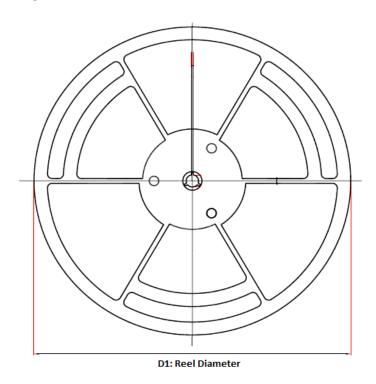

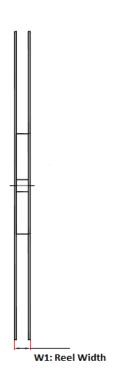

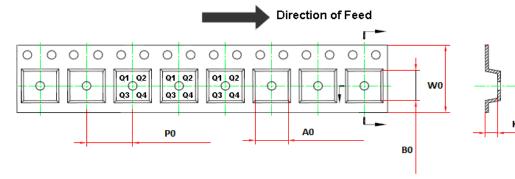

# **Tape and Reel Information**

| Order Number    | Package   | D1<br>(mm) | W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | W0<br>(mm) | Pin1<br>Quadrant |

|-----------------|-----------|------------|------------|------------|------------|------------|------------|------------|------------------|

| TPM2025Q-FC1R-S | QFN2X2-10 | 178        | 11.1       | 2.3        | 2.3        | 1.0        | 4          | 8          | Q1               |

| TPM2025-FC1R    | QFN2X2-10 | 178        | 11.1       | 2.3        | 2.3        | 1.0        | 4          | 8          | Q1               |

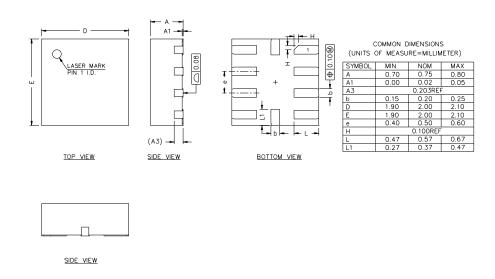

## **Package Outline Dimensions**

### **Order Information**

| Order Number    | Operating Ambient<br>Temperature Range | Package   | Marking<br>Information | MSL  | Transport Media,<br>Quantity |

|-----------------|----------------------------------------|-----------|------------------------|------|------------------------------|

| TPM2025Q-FC1R-S | -S -40 °C to 125 °C QFN2X2-10          |           | Q25                    | MSL3 | 3000                         |

| TPM2025-FC1R    | –40 °C to 125 °C                       | QFN2X2-10 | M25                    | MSL3 | 3000                         |

**Note:** Ambient temperature indicates device operation condition range. Application thermal behavior needs to be taken care of when operating in high temperature scenarios.

www.3peak.com 14 / 15 Rev.A.2

#### IMPORTANT NOTICE AND DISCLAIMER

Copyright© 3PEAK 2012-2023. All rights reserved.

**Trademarks.** Any of the 思瑞浦 or 3PEAK trade names, trademarks, graphic marks, and domain names contained in this document /material are the property of 3PEAK. You may NOT reproduce, modify, publish, transmit or distribute any Trademark without the prior written consent of 3PEAK.

**Performance Information.** Performance tests or performance range contained in this document/material are either results of design simulation or actual tests conducted under designated testing environment. Any variation in testing environment or simulation environment, including but not limited to testing method, testing process or testing temperature, may affect actual performance of the product.

**Disclaimer.** 3PEAK provides technical and reliability data (including data sheets), design resources (including reference designs), application or other design recommendations, networking tools, security information and other resources "As Is". 3PEAK makes no warranty as to the absence of defects, and makes no warranties of any kind, express or implied, including without limitation, implied warranties as to merchantability, fitness for a particular purpose or non-infringement of any third-party's intellectual property rights. Unless otherwise specified in writing, products supplied by 3PEAK are not designed to be used in any life-threatening scenarios, including critical medical applications, automotive safety-critical systems, aviation, aerospace, or any situations where failure could result in bodily harm, loss of life, or significant property damage. 3PEAK disclaims all liability for any such unauthorized use.